DISS. ETH NO. 29953

# Abstractions for Modern Heterogeneous Systems

A thesis submitted to attain the degree of

DOCTOR OF SCIENCES

(Dr. sc. ETH Zurich)

presented by

#### DARIO KOROLIJA

MSc in Electrical Engineering EPFL

born on 18.04.1993

accepted on the recommendation of

PROF. DR. GUSTAVO ALONSO (ETH Zurich) PROF. DR. TIMOTHY ROSCOE (ETH Zurich) PROF. DR. LANA JOSIPOVIĆ (ETH Zurich) DR. MICHAELA BLOTT (AMD)

2024

IKS-Lab Institute for Computing Platforms ETH Department of Computer Science

Dario Korolija

©Copyright by Dario Korolija, 2023

A dissertation submitted to ETH Zurich for the degree of Doctor of Sciences

#### DISS. ETH NO. 29953

examiner: Prof. Dr. Gustavo Alonso *co-examiners:* Prof. Dr. Timothy Roscoe Prof. Dr. Lana Josipović Dr. Michaela Blott

Examination date: December 19, 2023

Abstractions for Modern Heterogeneous Systems

## Abstract

The hardware landscape is undergoing a significant transformation, primarily fueled by the everincreasing demands for data processing. Modern computing systems are increasingly incorporating a wide range of heterogeneous processing units, signifying a departure from the traditional Von-Neumann architectures. A prime illustration of this diversification is the widespread adoption of hybrid computing platforms that combine a general-purpose CPU with a Field-Programmable Gate Array (FPGA), now becoming a standard feature in modern data centers and cloud environments.

These platforms significantly improve performance and energy efficiency across diverse workloads, thanks to their notable flexibility in accommodating a wide range of processing demands. However, their heterogeneity presents considerable challenges in terms of software compatibility, programming, and overall system design. Navigating these complex platforms to fully exploit the potential of the diverse hardware can be challenging. Notably, system software for these devices lags behind, lacking the traditional abstractions commonly found in conventional operating systems.

This thesis bridges this gap between modern heterogeneous hardware and its corresponding system software. To this end, we introduce Coyote, a comprehensive FPGA "shell" that provides a core set of essential features and abstractions upon which higher-level services can be built. In essence, Coyote can be viewed as a microkernel for modern hybrid computing systems, addressing the absence of critical abstractions such as multi-tenancy, virtualization, shared-memory, networking, and more. Coyote incurs small overhead while yielding substantial improvements in both performance and ease of use. Most importantly, it establishes a fundamental framework for the exploration of innovative data processing models and the role of modern heterogeneous platforms in modern computing on a broader scale.

## ZUSAMMENFASSUNG

Die Hardware-Landschaft erlebt eine bedeutende Transformation, angetrieben durch steigende Anforderungen an die Datenverarbeitung. Moderne Rechensysteme integrieren vermehrt heterogene Verarbeitungseinheiten, was einen Bruch mit traditionellen Von-Neumann-Architekturen bedeutet. Ein herausragendes Beispiel für diese Diversifizierung sind hybride Rechnerplattformen, die eine Allzweck-CPU mit einem Field-Programmable Gate Array (FPGA) kombinieren und mittlerweile in modernen Rechenzentren und Cloud-Umgebungen zum Standard geworden sind.

Diese Plattformen verbessern die Leistung und Energieeffizienz signifikant über verschiedene Workloads hinweg, dank ihrer bemerkenswerten Flexibilität bei der Bewältigung verschiedenster Verarbeitungsanforderungen. Die Heterogenität dieser modernen Geräte stellt jedoch erhebliche Herausforderungen in Bezug auf Softwarekompatibilität, Programmierung und das Gesamtdesign des Systems dar. Die Navigation durch diese komplexen Plattformen, um das volle Potenzial der vielfältigen Hardware auszuschöpfen, kann anspruchsvoll sein. Insbesondere hinkt die Systemsoftware für diese Geräte hinterher und weist nicht die traditionellen Abstraktionen auf, die in herkömmlichen Betriebssystemen üblich sind.

Diese Arbeit überbrückt die Kluft zwischen moderner heterogener Hardware und der entsprechenden Systemsoftware. Zu diesem Zweck stellen wir Coyote vor, eine umfassende FPGA-"Shell", die einen Kernsatz von wesentlichen Funktionen und Abstraktionen bietet, auf denen höhere Dienste aufbauen können. Im Wesentlichen kann Coyote als Mikrokernel für moderne hybride Rechensysteme betrachtet werden, der die fehlenden kritischen Abstraktionen wie Multi-Tenancy, Virtualisierung, Shared Memory, Netzwerke und mehr adressiert. Coyote verursacht geringe Overheads und bringt erhebliche Verbesserungen sowohl in Bezug auf Leistung als auch Benutzerfreundlichkeit mit sich. Am wichtigsten ist, dass es einen grundlegenden Rahmen für die Erforschung innovativer Datenverarbeitungsmodelle und die Rolle moderner heterogener Plattformen im modernen Computing im größeren Maßstab schafft.

Mome ocu

## **ACKNOWLEDGMENTS**

I extend my sincere gratitude to my advisor, Gustavo Alonso, for his invaluable support, abundant advice, and extensive feedback that significantly contributed to the progress of my research throughout my academic path. My appreciation extends to my co-advisor, Timothy Roscoe, for participating in insightful discussions and offering valuable ideas that have significantly impacted my work throughout the years. I'm also thankful for the continuous openness of other members in the System Group, namely Ana Klimović, Theodoros Rekatsinas, and Ghislain Fourny, to participate in discussions on various topics. Additionally, I would like to convey my thanks to Michaela Blott and Lana Josipović for graciously agreeing to be part of my doctoral committee and for the fruitful collaborations we have enjoyed.

I would also like to extend my gratitude to my collaborators from HPE, specifically Kim and Dejan, for the outstanding cooperation over the years that led to great results. I appreciate the valuable learning experiences gained through our joint efforts. My thanks also goes to my collaborators from Microsoft Research, namely Aleksandar, Shane, Juniy, Ho-Cheung, and Igor, for providing an enriching internship experience.

In adition, I wish to express my gratitude to the exceptional researchers and friends with whom I had the privilege of collaborating and spending time with over the years, including Zhenhao, Monica, Johannes, Dan, Dimitrios, Fabio, Thomas, David, Mohsen, Kaan, Abishek, Adam, Simon, Marko, Lazar, Michal, Michael, Andrea, Vasileios, Tom, Wenqi, and many others. It was also a pleasure collaborating with superb students, and I want to extend my thanks especially to Paul, Christian, Mihai, and Karol for their contributions to the research presented in this thesis. A special thank you to our dedicated administrators Nadia, Natasha, Jena, and Simonetta for their consistent assistance in times of need.

Finally, I want to express my heartfelt gratitude to my dearest friends and family, with a special acknowledgment to my parents, for their unwavering support throughout the entirety of my academic journey.

# CONTENTS

| Abstract |                                |         |                                                     |     |   |  | i     |     |       |    |

|----------|--------------------------------|---------|-----------------------------------------------------|-----|---|--|-------|-----|-------|----|

| Zı       | Zusammenfassung                |         |                                                     |     |   |  |       | iii |       |    |

| A        | cknow                          | vledgme | nts                                                 |     |   |  |       |     |       | v  |

| 1        | Introduction                   |         |                                                     |     |   |  |       |     | 1     |    |

|          | 1.1                            | Genera  | l Context                                           |     | • |  |       | •   | <br>• | 1  |

|          | 1.2                            | Thesis  | Goals                                               |     | • |  |       | •   | <br>• | 4  |

|          | 1.3                            | Contrib | outions & Structure                                 | ••• | • |  | •     | •   | <br>• | 5  |

| 2        | Do (                           | OS Abst | ractions Make Sense on FPGAs?                       |     |   |  |       |     |       | 7  |

|          | 2.1                            | Motiva  | tion                                                |     | • |  |       | •   | <br>• | 8  |

|          | 2.2                            | Founda  | tions                                               |     | • |  |       | •   | <br>• | 10 |

|          |                                | 2.2.1   | The Hardware "Split"                                |     | • |  |       | •   | <br>• | 15 |

|          |                                | 2.2.2   | Host System Software                                |     | • |  |       | •   | <br>• | 21 |

|          | 2.3 OS abstractions on an FPGA |         |                                                     |     |   |  | <br>• | 23  |       |    |

|          |                                | 2.3.1   | Processes, Threads, and Tasks                       |     | • |  |       | •   | <br>• | 23 |

|          |                                | 2.3.2   | Execution Environment                               |     | • |  |       | •   | <br>• | 28 |

|          |                                | 2.3.3   | Preemptive or Non-Preemtive Multitasking?           |     | • |  | •     | •   | <br>• | 32 |

|          |                                | 2.3.4   | Virtual Memory                                      |     | • |  | •     | •   | <br>• | 34 |

|          |                                | 2.3.5   | Memory Management                                   |     | • |  |       | •   | <br>• | 39 |

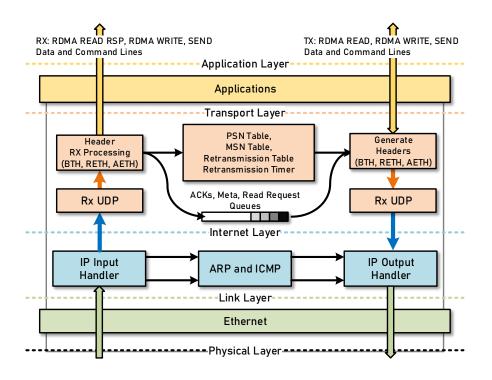

|          |                                | 2.3.6   | Network Stacks                                      |     | • |  |       | •   | <br>• | 42 |

|          |                                | 2.3.7   | Inter-Process Communication and Additional Services |     | • |  |       | •   | <br>• | 45 |

|          | 2.4                            | Related | l Work                                              |     | • |  |       | •   | <br>• | 47 |

|          | 2.5                            | Summa   | ary                                                 |     |   |  |       | •   | <br>• | 49 |

| 3 | Stat                             | ic Laye                                            | r: The System's Kernel                     | 51  |  |  |  |  |  |

|---|----------------------------------|----------------------------------------------------|--------------------------------------------|-----|--|--|--|--|--|

|   | 3.1                              | Communication with the Host: The FPGA's "Lifeline" |                                            |     |  |  |  |  |  |

|   |                                  | 3.1.1                                              | Interface: Memory-Mapped or Streaming?     | 54  |  |  |  |  |  |

|   |                                  | 3.1.2                                              | The DMA Wrapper                            | 56  |  |  |  |  |  |

|   |                                  | 3.1.3                                              | The Shell Interface                        | 58  |  |  |  |  |  |

|   |                                  | 3.1.4                                              | Device Driver                              | 66  |  |  |  |  |  |

|   |                                  | 3.1.5                                              | Cross-Platform Compatibility               | 67  |  |  |  |  |  |

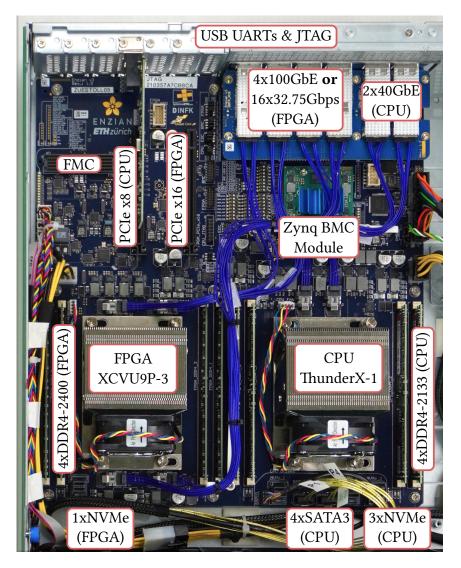

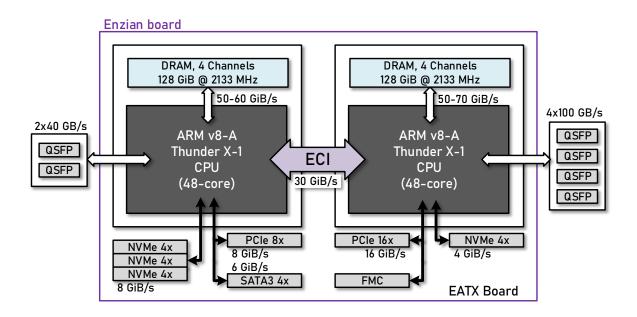

|   | 3.2                              | Enzian                                             | 1                                          | 68  |  |  |  |  |  |

|   |                                  | 3.2.1                                              | A Research Computer                        | 68  |  |  |  |  |  |

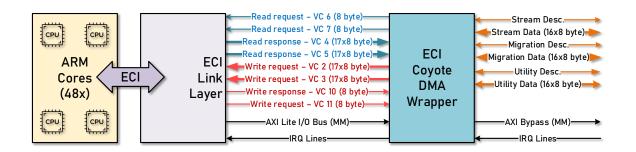

|   |                                  | 3.2.2                                              | Cache Coherent Interconnect                | 70  |  |  |  |  |  |

|   |                                  | 3.2.3                                              | Coyote on Enzian                           | 72  |  |  |  |  |  |

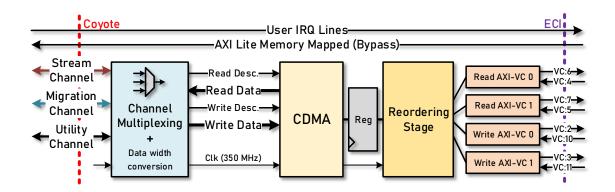

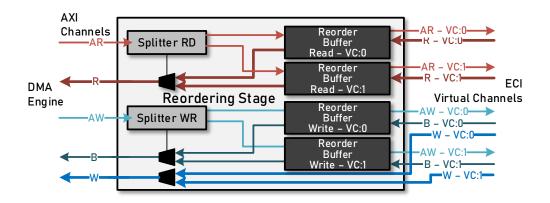

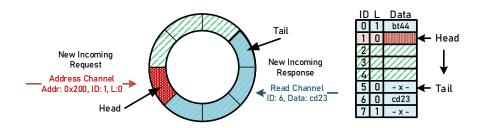

|   |                                  | 3.2.4                                              | Enzian DMA Wrapper                         | 75  |  |  |  |  |  |

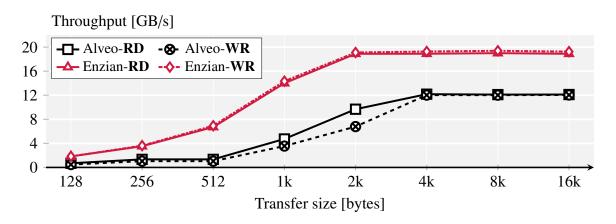

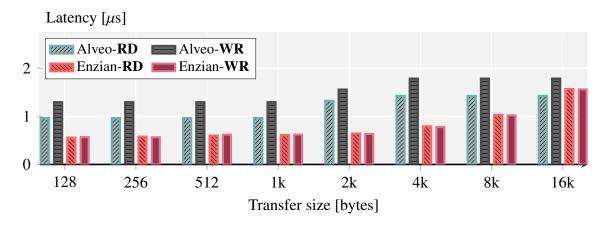

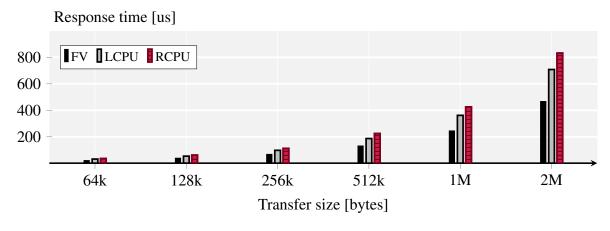

|   |                                  | 3.2.5                                              | Link Evaluation                            | 80  |  |  |  |  |  |

|   | 3.3                              | Hierar                                             | chical Dynamic Reconfiguration             | 83  |  |  |  |  |  |

|   |                                  | 3.3.1                                              | Reconfiguration Controller                 | 85  |  |  |  |  |  |

|   |                                  | 3.3.2                                              | Reconfiguration Performance                | 90  |  |  |  |  |  |

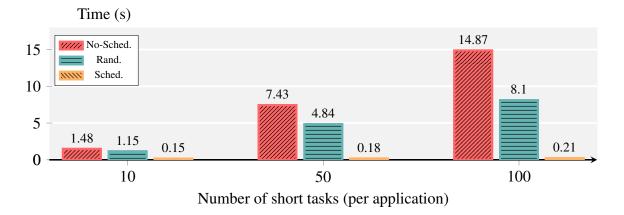

|   |                                  | 3.3.3                                              | Scheduling                                 | 92  |  |  |  |  |  |

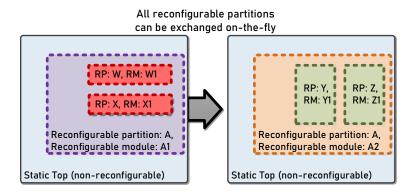

|   |                                  | 3.3.4                                              | Nested Reconfiguration                     | 94  |  |  |  |  |  |

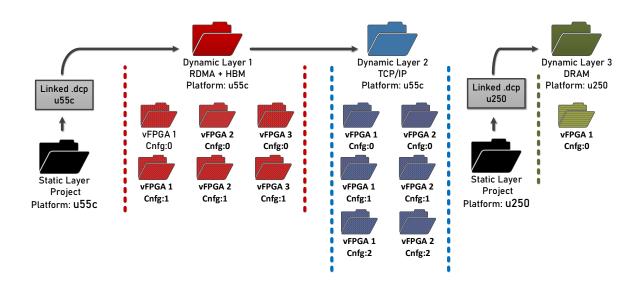

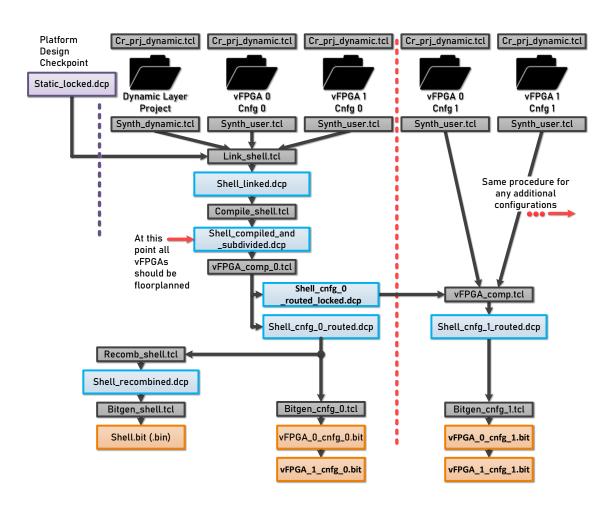

|   |                                  | 3.3.5                                              | Build Flow                                 | 97  |  |  |  |  |  |

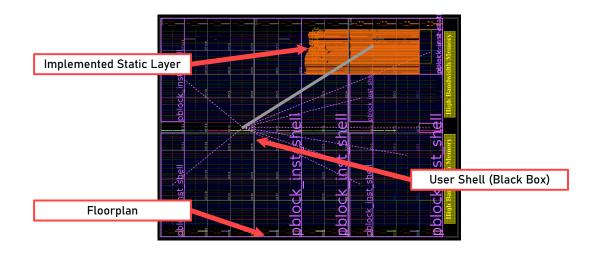

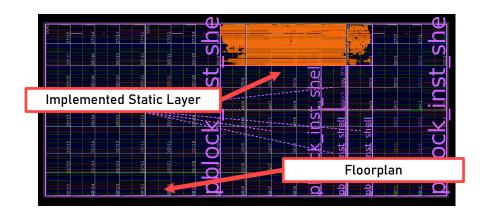

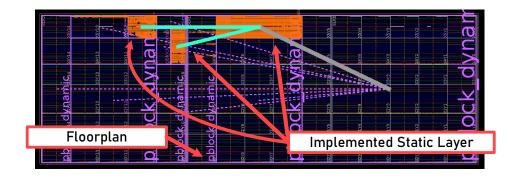

|   |                                  | 3.3.6                                              | Shell Floorplanning and Resource Usage     | 101 |  |  |  |  |  |

|   | 3.4                              | Summ                                               | ary                                        | 106 |  |  |  |  |  |

| 4 | Dynamic Layer: The User Shell 10 |                                                    |                                            |     |  |  |  |  |  |

|   | 4.1                              | The A                                              | rchitecture of the User Shell              | 108 |  |  |  |  |  |

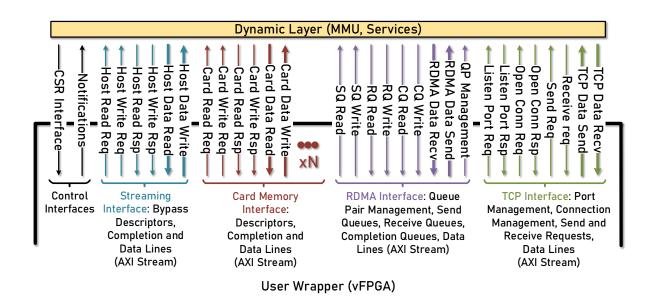

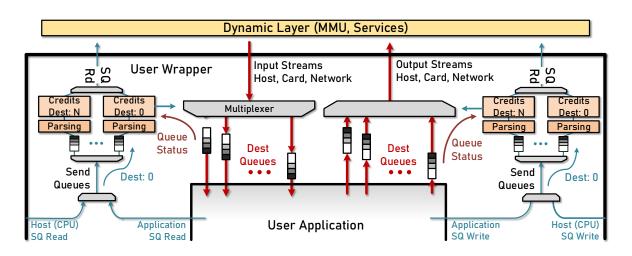

|   |                                  | 4.1.1                                              | Expansion of the Static Layer Interfaces   | 108 |  |  |  |  |  |

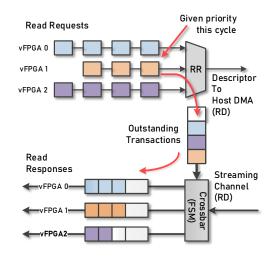

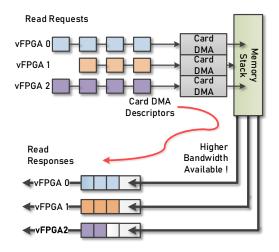

|   |                                  | 4.1.2                                              | Fair-Sharing and Packetization             | 111 |  |  |  |  |  |

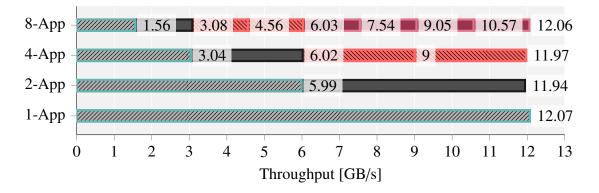

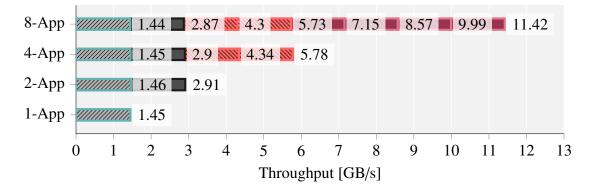

|   |                                  | 4.1.3                                              | Evaluation                                 | 112 |  |  |  |  |  |

|   | 4.2                              | Shared                                             | l Virtual Memory                           | 115 |  |  |  |  |  |

|   |                                  | 4.2.1                                              | Background                                 | 116 |  |  |  |  |  |

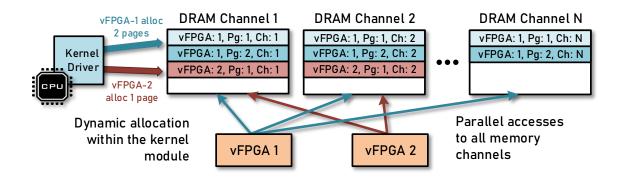

|   |                                  | 4.2.2                                              | Physical Memory Management                 | 118 |  |  |  |  |  |

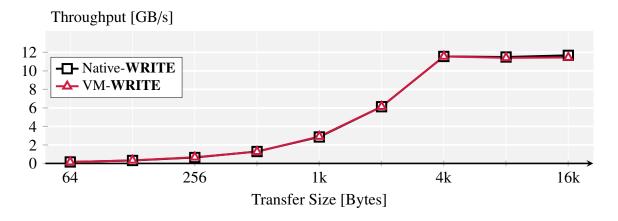

|   |                                  | 4.2.3                                              | Performance Evaluation of the Memory Stack | 123 |  |  |  |  |  |

|   |                                  | 4.2.4                                              | Memory Management Unit                     | 125 |  |  |  |  |  |

|   |                                  | 4.2.5                                              | Unified Memory                             | 135 |  |  |  |  |  |

|   |                                  | 4.2.6                                              | FPGAs Are Not GPUs!                        | 138 |  |  |  |  |  |

|   |                                  | 4.2.7                                              | Heterogeneous Memory Management            | 145 |  |  |  |  |  |

|   |     | 4.2.8 | Evaluation of the Shared Virtual Memory 150 |

|---|-----|-------|---------------------------------------------|

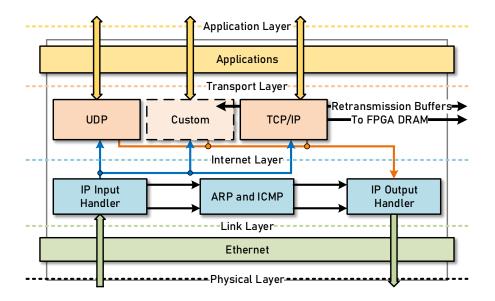

|   | 4.3 | Netwo | rk Services: TCP/IP                         |

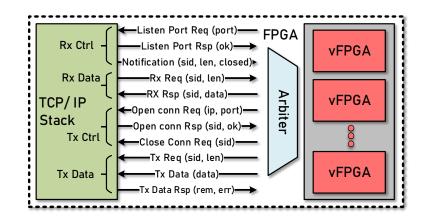

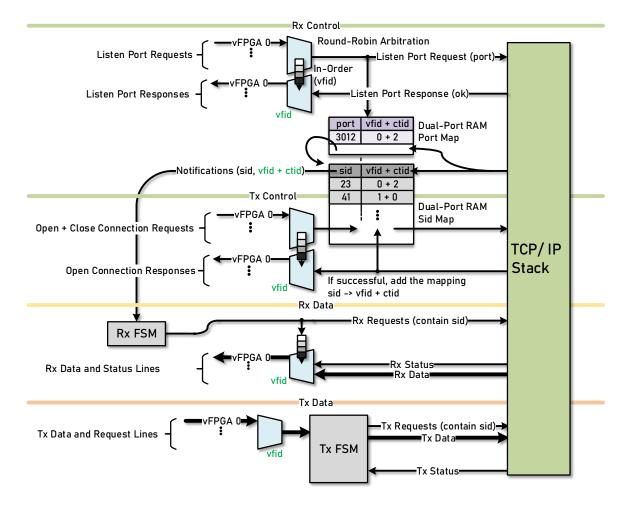

|   |     | 4.3.1 | TCP/IP Architecture and Interfaces          |

|   |     | 4.3.2 | Integration of the TCP/IP Stack             |

|   |     | 4.3.3 | Resource Usage of the TCP/IP Stack          |

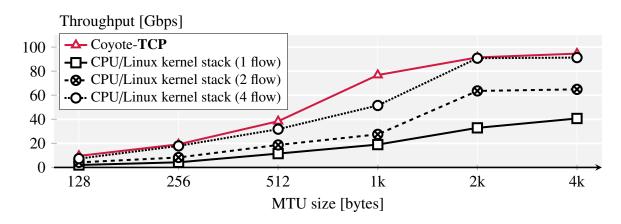

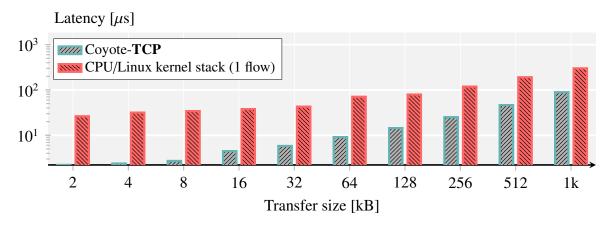

|   |     | 4.3.4 | Evaluation of TCP/IP                        |

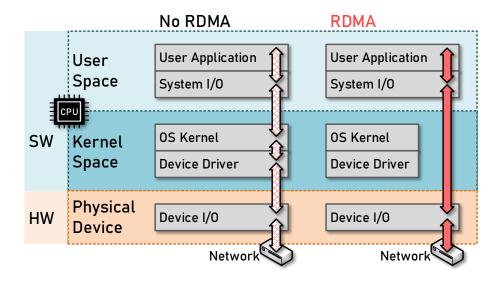

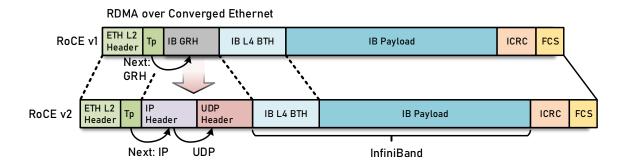

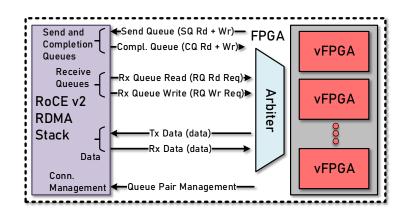

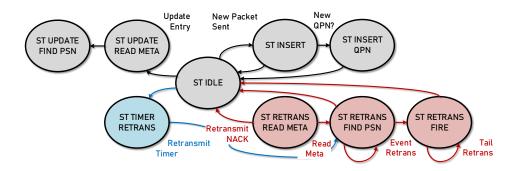

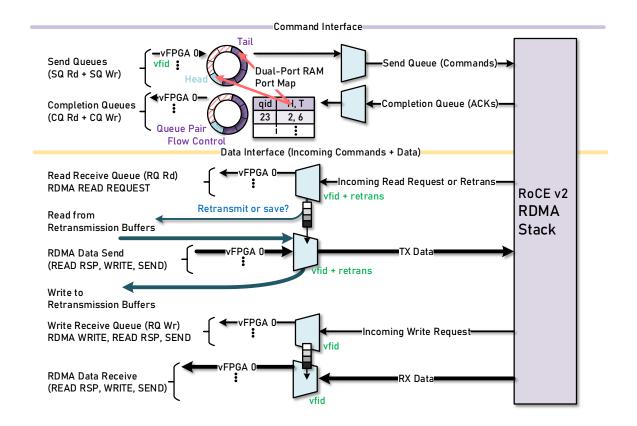

|   | 4.4 | Netwo | rk Services: RDMA                           |

|   |     | 4.4.1 | RDMA Architecture and Interfaces            |

|   |     | 4.4.2 | Integration of RDMA                         |

|   |     | 4.4.3 | Resource Usage of RDMA Stack                |

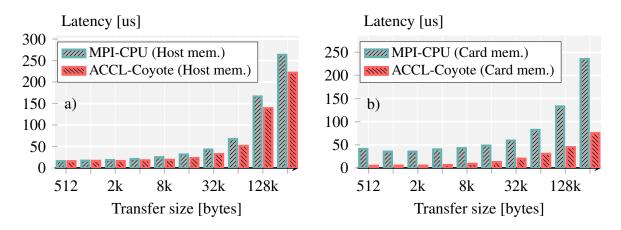

|   |     | 4.4.4 | Evaluation of RDMA                          |

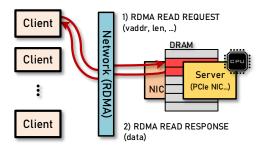

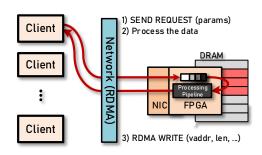

|   |     | 4.4.5 | Is RDMA a Fitting Abstraction?              |

|   | 4.5 | Summ  | ary                                         |

| _ |     |       |                                             |

| 5 |     |       | Layer: The Virtual FPGA179100100            |

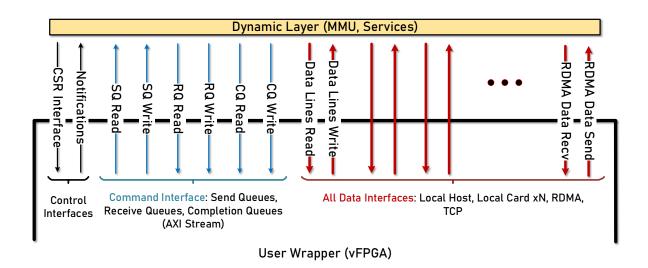

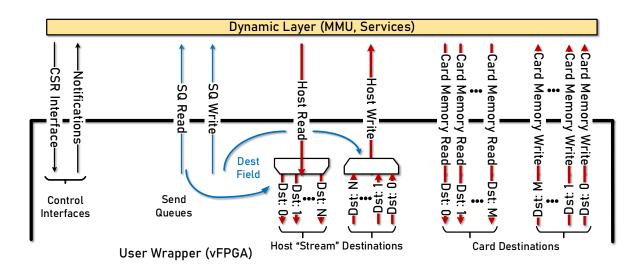

|   | 5.1 |       | d Logic Interface                           |

|   |     | 5.1.1 | Service Interfaces                          |

|   |     | 5.1.2 | Unifying the Interfaces                     |

|   |     | 5.1.3 | Parallel Data Streams                       |

|   |     | 5.1.4 | Untrusted Environment                       |

|   | 5.2 |       | Machines                                    |

|   |     | 5.2.1 | Virtualization of the Host Resources        |

|   |     | 5.2.2 | Background                                  |

|   |     | 5.2.3 | Virutalization of vFPGAs                    |

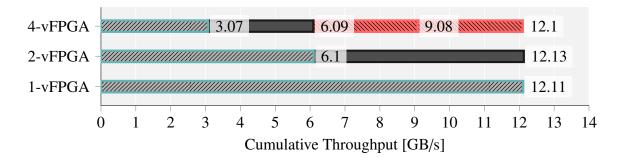

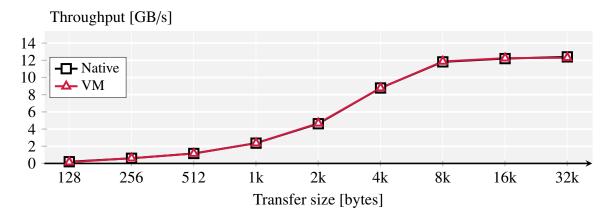

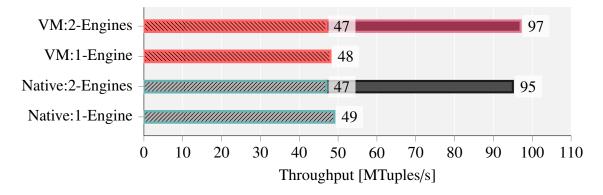

|   |     | 5.2.4 | Evaluation                                  |

|   | 5.3 |       | are API                                     |

|   |     | 5.3.1 | Coyote Threads and Tasks                    |

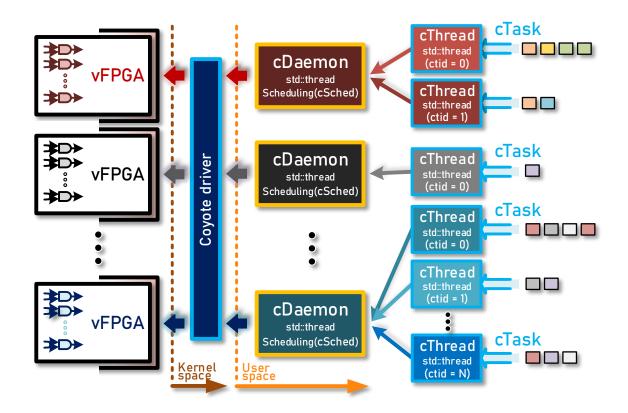

|   |     | 5.3.2 | Coyote Daemon                               |

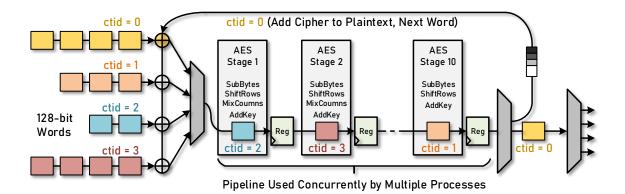

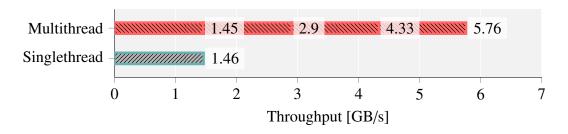

|   |     | 5.3.3 | Multithreading                              |

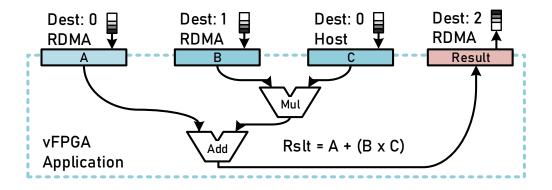

|   | 5.4 |       | ase - ACCL                                  |

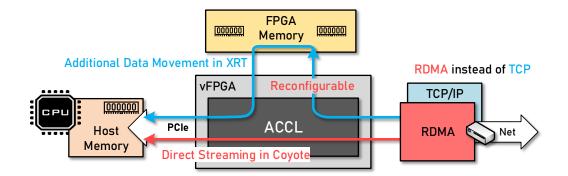

|   |     | 5.4.1 | Abstractions Used                           |

|   |     | 5.4.2 | Resource Usage                              |

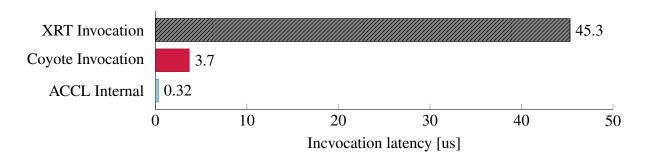

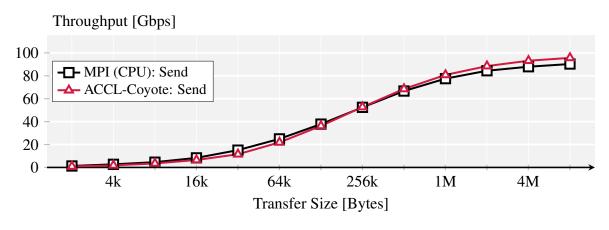

|   |     | 5.4.3 | Evaluation                                  |

|   | 5.5 | Summ  | ary                                         |

| 6            | Farview: Smart Disaggregated Memory |                               |                                            |     |  |  |

|--------------|-------------------------------------|-------------------------------|--------------------------------------------|-----|--|--|

|              | 6.1                                 | Motivation                    |                                            |     |  |  |

|              | 6.2                                 | 2 Background and Related Work |                                            |     |  |  |

|              |                                     | 6.2.1                         | Coping With Memory Pressure                | 225 |  |  |

|              |                                     | 6.2.2                         | Efficient Data Movement                    | 226 |  |  |

|              | 6.3                                 | System                        | n Overview                                 | 227 |  |  |

|              |                                     | 6.3.1                         | Smart Buffer Pool With Operator Offloading | 228 |  |  |

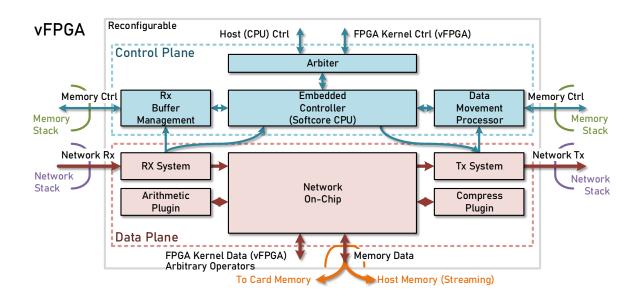

|              |                                     | 6.3.2                         | FPGA-Based Architecture                    | 228 |  |  |

|              | 6.4                                 | Implen                        | nentation                                  | 229 |  |  |

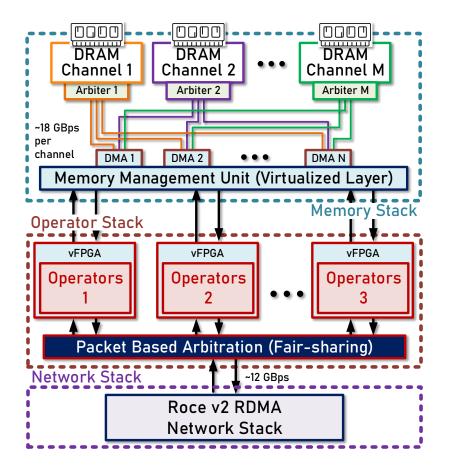

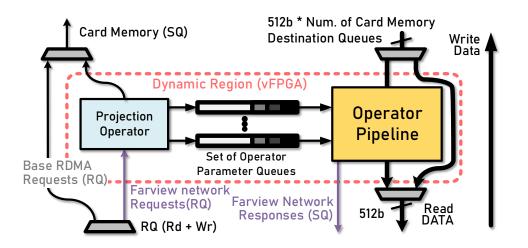

|              |                                     | 6.4.1                         | Architecture                               | 229 |  |  |

|              |                                     | 6.4.2                         | Farview Programmatic Interface             | 232 |  |  |

|              |                                     | 6.4.3                         | Network and Memory Stacks                  | 233 |  |  |

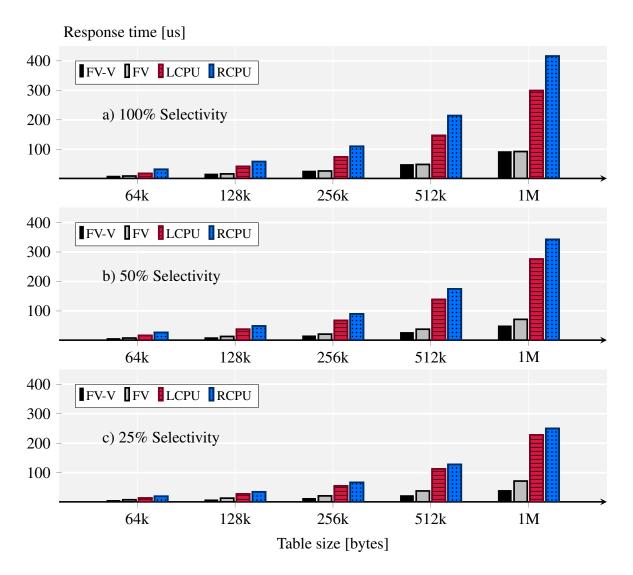

|              |                                     | 6.4.4                         | Operator Stack                             | 234 |  |  |

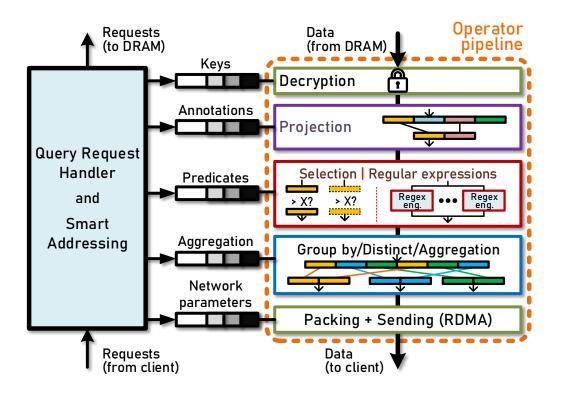

|              | 6.5                                 | Operat                        | ors and Pipelines                          | 235 |  |  |

|              |                                     | 6.5.1                         | Operator Pipelines                         | 235 |  |  |

|              |                                     | 6.5.2                         | Projection Operators                       | 237 |  |  |

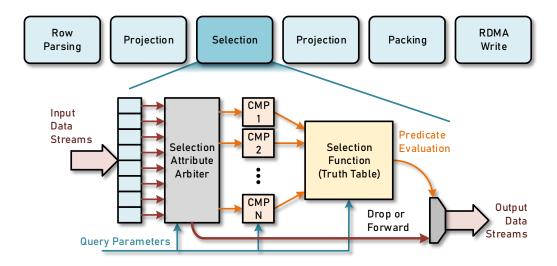

|              |                                     | 6.5.3                         | Selection Operators                        | 238 |  |  |

|              |                                     | 6.5.4                         | Grouping Operators                         | 240 |  |  |

|              |                                     | 6.5.5                         | System Support Operators                   | 241 |  |  |

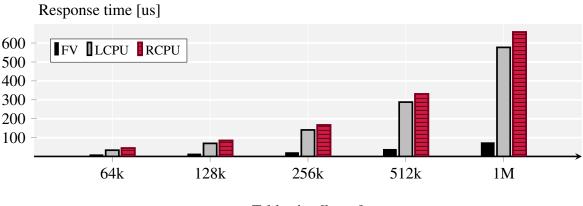

|              | 6.6                                 | Evalua                        | tion                                       | 242 |  |  |

|              |                                     | 6.6.1                         | Experimental Setup                         | 242 |  |  |

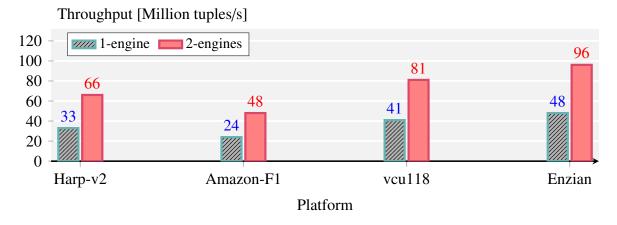

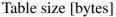

|              |                                     | 6.6.2                         | Projection                                 | 244 |  |  |

|              |                                     | 6.6.3                         | Selection                                  | 245 |  |  |

|              |                                     | 6.6.4                         | Grouping                                   | 247 |  |  |

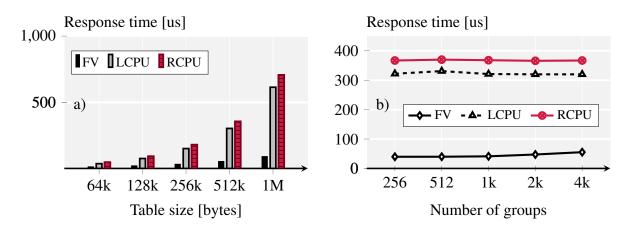

|              |                                     | 6.6.5                         | Regular Expression Matching                | 248 |  |  |

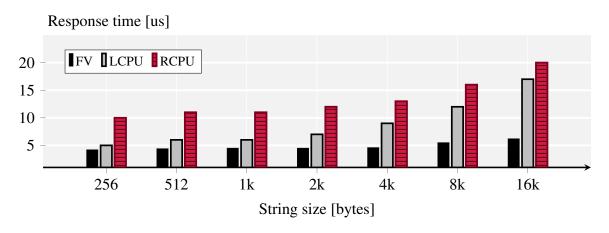

|              |                                     | 6.6.6                         | Encryption/Decryption and Multiple Clients | 249 |  |  |

|              | 6.7                                 | Farviev                       | w Frontend                                 | 251 |  |  |

|              |                                     | 6.7.1                         | Modularis                                  | 252 |  |  |

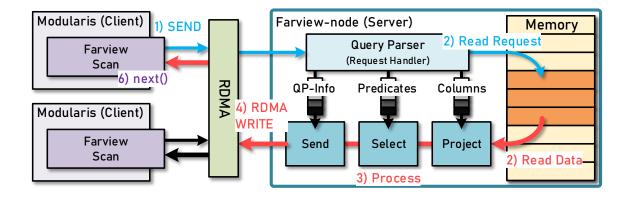

|              |                                     | 6.7.2                         | Integration                                | 252 |  |  |

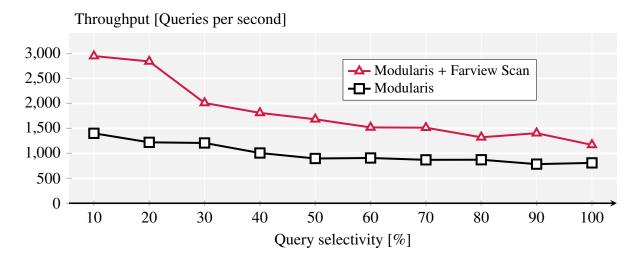

|              |                                     | 6.7.3                         | Initial Evaluation of a Compete System     | 254 |  |  |

|              | 6.8                                 | Summa                         | ary                                        | 255 |  |  |

| 7            | Con                                 | clusion                       |                                            | 257 |  |  |

| Bibliography |                                     |                               |                                            |     |  |  |

# CHAPTER **1**

## INTRODUCTION

## **1.1 General Context**

In an era marked by the exponential growth of data, our computational demands are experiencing exponential growth [191]. This coupled with the demise of Moore's law [82] and the end of Dennard Scaling [84] has prompted a significant paradigm shift in the world of computing. The level of effortless scalability in computational performance that was present just a decade or two ago has experienced a drastic decrease in recent times. The classical Reduced Instruction Set Computer (RISC) architectures, once considered scalable and sufficient for most computational needs, now require additional specialized hardware to cope with ever increasing computational demands. As a result, there is a growing trend to explore and implement a variety of heterogeneous architectures involving traditional general-purpose processing units and cutting-edge specialized hardware solutions.

This implies that hardware acceleration is increasingly recognized as a necessity in the realm of modern data centers and cloud computing. The exponential growth in data volumes, the complexity of applications, and the demand for real-time processing have outpaced the capabilities of traditional CPUs. General-purpose CPUs are versatile but fall short when it comes to handling highly parallelized workloads efficiently. This is where dedicated hardware accelerators come into play. They are purpose-built for parallel processing and can significantly enhance the performance of modern workloads. These hardware accelerators come in different flavours, including ASICs, GPUs, and FPGAs. Each with its own set of advantages and applications.

#### **Chapter 1. Introduction**

Application-Specific Integrated Circuits (ASICs) represent custom-designed microchips tailored for specific or closely related functions. ASICs are unparalleled in terms of performance and energy efficiency for their intended tasks. However, they are rigidly configured during manufacturing and cannot be reprogrammed for different applications. These extreme levels of specialization make ASICs well-suited for tasks where utmost performance is critical.

The growing importance of machine learning has brought notable examples of ASIC utilization, with the Tensor Processing Unit (TPU) developed by Google [114] being one such case. TPUs serve as dedicated hardware accelerators optimized primarily for matrix operations, a fundamental aspect of many deep learning algorithms. They excel in executing the computations commonly encountered during neural network training and inference, making them a vital component in the machine learning landscape. Still, not every individual or organization can leverage the extensive resources and capabilities possessed by corporate giants like Google, rendering large-scale ASIC projects a formidable task. Graphics Processing Units (GPUs) alleviate some of these complexities by offering added versatility, hence their widespread utilization in modern machine learning. However, numerous application scenarios, particularly in the realm of cloud computing, call for the adaptability to accommodate diverse workloads and evolving demands. This adaptability is an aspect where neither ASICs nor GPUs excel, as these devices exhibit strengths in certain domains of computing while showing severe limitations in others.

Field-Programmable Gate Arrays (FPGAs) offer a unique blend of flexibility and performance. These reconfigurable hardware devices essentially provide a "blank canvas" for developers, allowing them to implement custom circuits dynamically, serving a wide range of processing tasks. In exchange for some of the peak performance seen in ASICs, FPGAs provide a significantly higher degree of generality. Consequently, they prove to be particularly valuable for rapidly prototyping new hardware designs and swiftly adapting to evolving requirements. One of their key advantages lies in the multitude of approaches through which they can seamlessly integrate into the broader system framework.

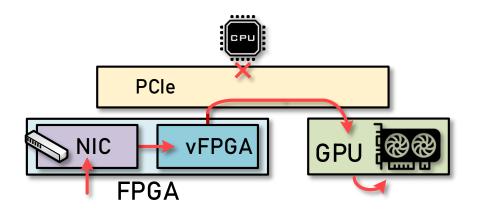

Their abundant I/O capabilities provide a variety of configuration options. They can operate as conventional CPU-attached accelerators or, in contrast to other accelerators, establish a number of direct connections to external devices and networks. In this role, they establish communication channels between multiple devices, both local and remote, functioning as true "bump-in-the-wire" processors. These "silent" processors seamlessly perform computation on the data as it flows through them, eliminating the need for additional data movement, a key solution to one of the primary bottlenecks in modern data processing. These properties have led modern large scale hyperscalers, such as Amazon and Microsoft to deploy FPGAs in large scale.

The large scale integration of these heterogeneous accelerators coupled to general-purpose CPUs, poses a significant challenge due to the mismatch between long-established abstractions designed for traditional load/store architectures and the intricate nature of these modern accelerators. Instead of having a single CPU with some attached memory and some I/O, these heterogeneous systems encompass a multitude of processing cores, including both traditional and specialized architectures, all engaged in complex interactions.

Each of these processors may maintain their own unique memory address spaces, which might or might not be accessible by other cores through memory-mapped instructions or via bulk DMA transfers. Different address spaces on different cores might even be potentially coherent. Added virtualization layers could exist on top of the attached memories, providing shared-memory models, etc. All these features add layers of complexity, requiring careful consideration.

Regrettably, traditional operating system abstractions are ill-equipped to exploit the full potential of this innovative hardware landscape. Consequently, end users are compelled to engage in low-level "bare-metal" like interactions with the hardware, resulting in developmental complexities, reduced productivity, and limitations on the exploration of high-level concepts and research.

To circumvent the non-existant abstractions, modern FPGA "shells" (essentially operating systems for FPGAs, orchestrating complete operation) limit what can be done on these devices. They hide or outright completely disable features from end users and instead provide very strict computational models. This holds true for Amazon F1 instances [30], that emulate the GPU-style computation, focusing on popular machine learning workloads while overlooking one of the key domains where FPGAs excel, namely, networking. On the contrary, Microsoft's Catapult shell [172] incorporates networking aspects but does not address the potential for these shells to be integrated into a virtualized cloud environment. In both instances, the level of programmability and interaction with these shells remains quite basic, demanding a steep learning curve and hindering their use by individuals lacking significant hardware development experience.

It's evident that there is a need to adjust the current set of abstractions in use (or come up with new ones). We should not only focus on achieving the best possible performance but also on making these systems approachable. While top-notch performance is important, if a system is challenging to program and interact with, it won't gain widespread acceptance and use. To illustrate this point, take into account that in the present day, very few individuals would opt to write code directly in assembly language for general-purpose CPUs, even though it has the potential to achieve peak performance. Instead, we tend to program using higher-level tools and leverage features such as multitasking, multithreading, virtual memory, networking services, and more.

## **1.2** Thesis Goals

In essence, the evolving landscape of hardware and technology demands that we rethink and refine our approach to abstractions to fully capitalize on the opportunities presented by modern hardware. The most critical abstractions we explore in this thesis are summarized as follows.

- Multitasking is a fundamental concept in traditional operating systems. In a multitasking environment, multiple processes run concurrently, making the most of the system's capabilities. Multitasking is usually absent in modern FPGAs, which leads to underutilization as they grow in size. Our work aims to introduce this missing capability to enable efficient resource sharing of these devices.

- Virtualization is crucial in modern computing for several key reasons. It provides security and flexibility by enabling multiple parallel users to safely distribute and utilize the system's underlying resources. This streamlines the development process by creating isolated environments, abstracting away the complexities of the physical hardware. It is yet another concept missing in modern FPGAs. In this thesis, we implement virtualization across the heterogeneous stack, covering both FPGA-side and CPU-side resources.

- Networking abstractions play a pivotal role in the context of primarily distributed, modern data processing. FPGAs emerge as ideal tools in such scenarios, enabling the reduction of data movement and efficient processing with minimal added costs. We explore how different networking services can be efficiently integrated and utilized in modern FPGAs.

- With the above abstractions implemented, we investigate the development of additional systems that can harness these to improve the performance of modern workloads. We place a particular focus on memory disaggregation and the concept of offloading computation close to data, both of which are prominent trends in modern cloud computing. We showcase how these abstractions, when executed on these heterogeneous platforms, can substantially enhance performance in this context.

The central objective of this thesis is to establish a fundamental set of abstractions that mirror the functionalities of a conventional operating system, tailored specifically for hybrid platforms featuring FPGAs. Our goal is to create a set of tools that have the potential to enhance productivity on these cutting-edge platforms for a wide range of users. Additionally, we aim to reduce the obstacles to exploring these platforms, especially for users with limited experience.

### **1.3** Contributions & Structure

The primary contribution of this thesis is the introduction of *Coyote*, a holistic framework that provides a range of hardware and software abstractions for contemporary heterogeneous systems. This framework is extensively detailed throughout the thesis, beginning from the foundational layers of the stack and advancing to the software interfaces designed for end-users. The culmination of this work is the development of *Farview*, a practical system build on top of Coyote that demonstrates how heterogeneous hardware can effectively support current trends in memory disaggregation. These contributions are summarized as follows.

- In <u>Chapter 2</u> we establish the basis for the entire thesis by addressing the fundamental question: "How relevant are traditional operating system abstractions in the context of an FPGA within a hybrid system?" This chapter lays the groundwork for the in-depth exploration of Coyote's implementation.

- In <u>Chapter 3</u>, we explore the core (kernel) of Coyote. This chapter emphasizes the critical interaction between the host CPU and the FPGA, serving as the foundation upon which additional abstractions and services within the system are constructed. We present the interfaces that render Coyote adaptable to different platforms and substantiate this by successfully porting it to a custom research computer. Additionally, We investigate hierarchical dynamic reconfiguration, providing Coyote with a flexibility that surpasses that of other state-of-the-art FPGA shells.

- In <u>Chapter 4</u>, we explore the configurable "shell" layer that provides system-wide abstractions and services within Coyote. We begin by concentrating on the memory architecture among devices and the development of the encompassing shared virtual memory model. Subsequently, we shift our attention to the network structures, where we analyze both the TCP/IP and RDMA network stacks and their integration into a multi-tenant environment.

- In <u>Chapter 5</u>, we introduce the standard execution environment in Coyote, facilitated by a series of clearly defined interfaces through which users can seamlessly interact with all Coyote services, whether they are local or remote. We also explore the software layer in Coyote, beginning with software virtualization, which offers the capability to fully encapsulate Coyote's tenants in virtual machines. We then examine the runtime abstractions and end-user software application interface. We conclude this chapter with a practical application that can leverage Coyote's abstractions.

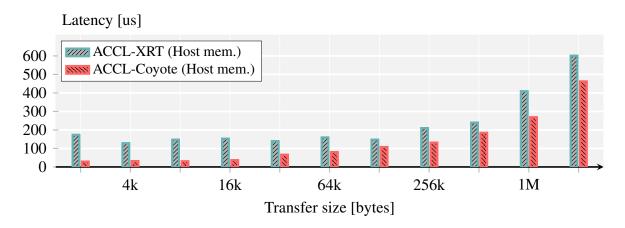

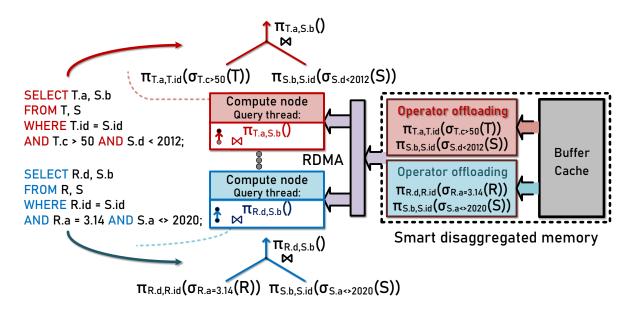

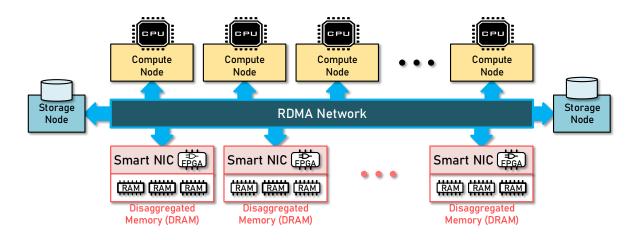

• In <u>Chapter 6</u>, we utilize Coyote as a foundation to construct supplementary systems. In this section we introduce *Farview*, a disaggregated memory solution designed for modern databases, which functions as a remote buffer cache with operator offloading capabilities. Farview illustrates how smart disaggregated memory can serve as a practical alternative for databases deployed in cloud environments.

A portion of the work used for this thesis has been published and is included here for reference:

- Do OS Abstractions Make Sense in FPGAs? by D. Korolija, T. Roscoe, G. Alonso, in the 14th USENIX Symposium on Operating Systems Design and Implementation

- Farview: Disaggregated Memory with Operator Off-loading for Database Engines by D. Korolija, D. Koutsoukos, K. Keeton, K. Taranov, D. Milojičić, G. Alonso in the 12th Conference on Innovative Data Systems Research

- LynX: A Flexible FPGA Virtualization Framework for Heterogeneous Systems by D. Korolija, T. Roscoe, G. Alonso, in 10th Workshop on Systems for Post-Moore Architectures

- Enzian: an open, general, CPU/FPGA platform for OS research by D. Cock, M. Giardino, Z. He, N. Hossle, D. Korolija, M. Licciardello, K. Martsenko, A. Ramdas, A. Turowski, G. Alonso, T. Roscoe, in the Architectural Support for Programming Languages and Operating Systems 2022

- Data Processing with FPGAs on Modern Architectures by W. Jiang, D. Korolija, G. Alonso, in the Companion of the 2023 International Conference on Management of Data

- Serverless FPGA: Work-In-Progress by F. Maschi, D. Korolija, G. Alonso, in the 1st Workshop on SErverless Systems, Applications and MEthodologies

# CHAPTER 2

# **Do OS Abstractions Make Sense on FPGAs?**

As computational demands continue to grow, hybrid computing systems that tightly integrate CPUs and FPGAs are increasingly common in modern data center and cloud settings. The combination of these heterogeneous devices can yield significant performance advantages and greater energy efficiency compared to conventional general-purpose architectures. Moreover, they provide significantly greater flexibility when compared to conventional ASIC accelerators, which constitutes one of their primary strengths.

However, it is crucial to recognize the existing challenges involved. In general, working with these systems, including development, deployment, and interaction, can often prove to be highly complex and cumbersome. To make the most of the performance and flexibility of these devices, the overall system interaction frequently involves the utilization of a low-level application programming interface (API) that closely resembles that used in traditional bare-metal programming. Inherent lack of support for higher-level abstractions, which we typically rely on in traditional operating systems, such as processes, multitasking, memory virtualization, and various accompanying services, becomes a significant constraint as FPGAs grow in size and capability. This limitation significantly reduces the overall productivity on these devices.

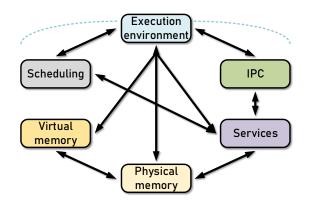

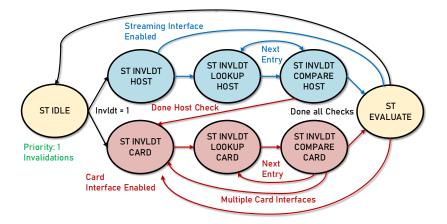

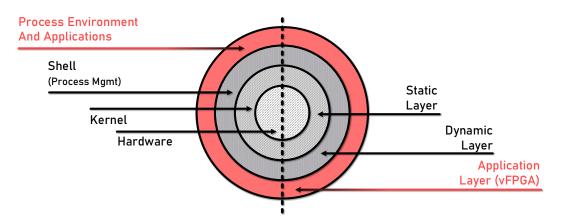

This has prompted recent efforts in research to replicate a portion of the traditional operating system execution environment on FPGAs, encompassing aspects such as processes, threads, scheduling, virtualization, and more. Yet, in these efforts, the predominant focus is on individual abstractions, whereas what makes these abstractions so challenging and difficult to explore lies in the interaction betwen them (Figure 2.1). As an example, virtual memory depends on the underlining physical memory management within the system. Services, which play a vital role

Figure 2.1: Interdependencies among various conventional OS abstractions.

in simplifying the user's experience, can, in turn, be dependent on this virtual memory. The scheduling of user applications needs to take into account all the stateful services that exist and must be executed without placing trust in the running user processes, each of which should also be kept isolated from one another, and so forth.

Given the above, in this chapter, we give an initial introduction to *Coyote*, the system we built to examine to what extent do traditional OS abstractions remain relevant when applied to an FPGA as part of a hybrid system, especially when considering them as an integrated whole, as they would be in a traditional operating system.

### 2.1 Motivation

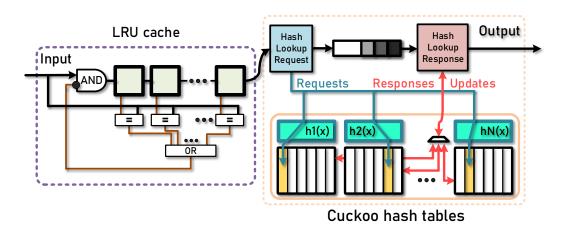

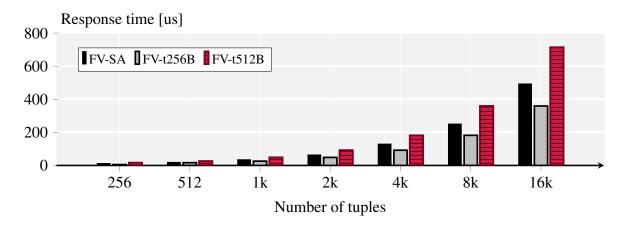

Field-Programmable Gate Arrays (FPGAs) are increasingly being adopted as a standard technology in datacenters and by cloud providers [30, 26, 62, 45]. Hardware acceleration is thus becoming increasingly relevant for a variety of use cases, e.g., machine learning workloads [118, 201, 166], data processing [128, 67, 144], high performance computing [56, 53] and networking [91, 185]. Reconfigurable platforms in these domains offer increased flexibility and lower power consumption compared to ASICs or GPUs for many applications, while retaining the performance (e.g. [43, 92, 137, 200, 129]). Despite their benefits, these platforms (due to their origins in embedded systems and prototyping), still present major challenges in terms of programming, deployment, and secure management. As a result, along with much research into making FPGAs easier to program [7, 159, 197, 203, 46, 180, 47], considerable recent work applied ideas from operating systems design and implementation to resource allocation, sharing, isolation, and management of an FPGA-centric computer. So far, this work has been piecemeal, primarily focusing on a particular aspect of functionality in isolation, e.g. Feniks [212] targets solely FPGA access to I/O peripherals, Optimus [146] provides access to a host's virtual memory via address translation, AmorphOS [122] prioritizes the scheduling of user applications as its central objective, etc. All these yield substantial incremental improvements over existing solutions and constitute the current state of the art.

At the same time, what makes good OS design so challenging is the close interaction in the kernel between *all* the functionality. Virtual memory without support for multiple applications (multi-tenancy) or strong isolation between them is of limited use. Virtualizing hardware devices without providing virtual addressing and creating a common execution enviroment that abstracts the hardware leaves most of the problem unsolved. An FPGA scheduler that cannot exploit the ability to dynamically reconfigure parts of the chip or/and cannot properly capture the complete state of the application running within the FPGA has a limited shelf-life, and so on. Moreover, in contrast to traditional operating systems that take advantage of the underlying general-purpose hardware, integrating these abstractions into a hybrid system with reconfigurable fabric introduces significant additional challenges. Questions arise about how these abstractions are mapped to the physical hardware, their physical placement, whether the physical timing requirements can be met, among many other considerations.

Therefore, we step back to ask the question: to what extent can (or should) traditional OS concepts (processes, virtual memory, etc.) be usefully translated to an FPGA? What happens when they are? To answer this question, we need to adopt a comprehensive, holistic approach and think about complete functionality, rather than sticking to particular aspects of an OS or supporting only limited FPGA features.

To this end, we developed *Coyote*, combining a coherent set of OS abstractions in a single unified runtime for FPGA-based applications. Coyote serves as an FPGA shell, assuming control over the entire FPGA fabric as well as all the connections to the external environment. A suitable analogy for Coyote within the domain of operating systems would be to liken it to a microkernel. It provides the core set of essential functions and features on which other services can be based: a uniform execution environment and portability layer, virtualization, physical memory management, communication, spatial and temporal scheduling, networking, and an analog of software processes or tasks for various custom user logic and applications. Coyote helps us to examine a range of OS abstractions and to provide a critical assessment of how each might map to an FPGA, especially in the context of its interaction with other abstractions.

## 2.2 Foundations

We begin this section by assessing the hardware architecture commonly encountered in hybrid platforms deployed within modern data centers and cloud systems. Our focus will be on the organization of the *shells* running on these platforms. These shells constitute the system software layer responsible for exposing the functionality of these platforms to end users.

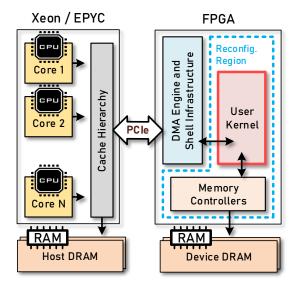

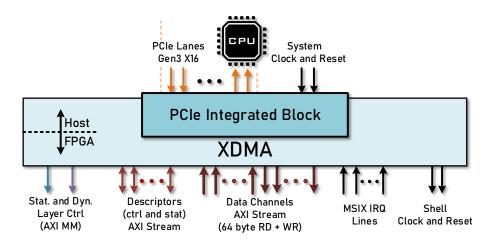

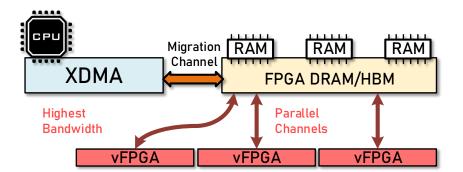

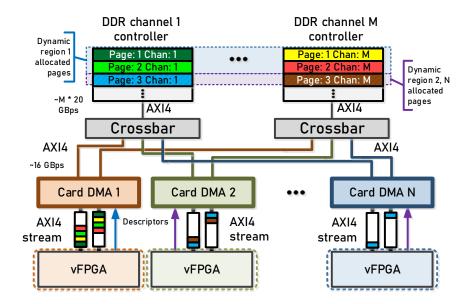

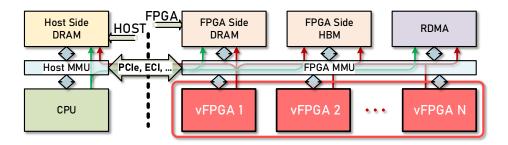

These hybrid platforms predominantly feature a combination of a conventional server-grade CPU and a high-performance FPGA. Typically, these two components are connected via a conventional peripheral bus like PCIe (shown in Figure 2.2), as observed in several AMD and Intel data center cards [12, 6, 5]. Because of the nature and complexity of hardware development, this CPU-FPGA interconnect serves a dual purpose. It not only facilitates data transfers during different processing stages but also handles the majority of the control and management tasks on these platforms (significantly simpler to accomplish on a general-purpose CPU). As a result, it assumes a pivotal role in the overall design decisions within the system.

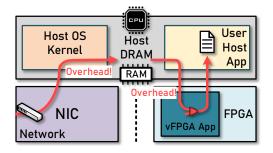

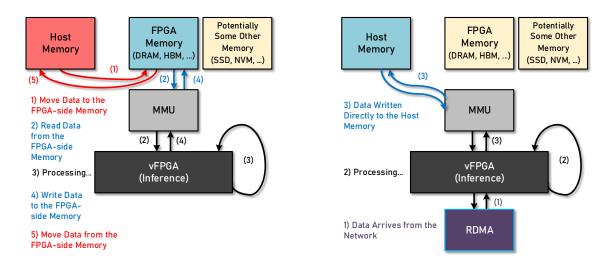

Different configurations with conventional PCIe interconnect are prevalent in modern hyperscaler cloud shells offered by companies such as Amazon [30] and Alibaba [26], using AMD commodity hardware (Figure 2.2). Microsoft, similarly, employs Catapult [62], their proprietary, internally developed combination of hardware and shell (Figure 2.4). In these cloud configurations, the model of computation is primarily centered around the bulk-oriented data movement between the host CPU and the FPGA accelerator. However, due to the limited abstractions in the overall systems software support, these frameworks offer limited flexibility in terms of a computation model. They typically adhere to a rigid GPU-style of computation, where data must first be copied to the FPGA's local memory before starting the computation, and subsequently copied back upon completion. Additionally, most of these platforms are completely *host-centric*, relying fully on the CPU to manage complete transactions. As a direct result, these limitations in the compute model add significant overheads.

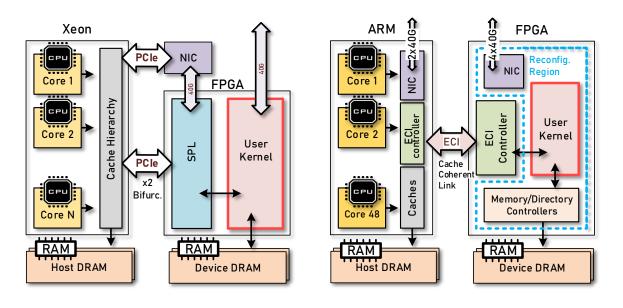

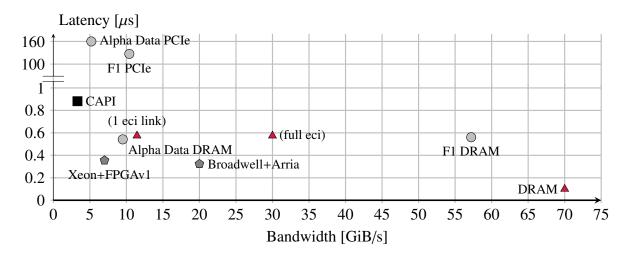

More recently, efforts have been made to mitigate these limitations, especially for fine-grained workloads, by connecting FPGAs through cache-coherent interconnects such as CXL [73], CCIX [63], OpenCAPI [188], or Intel UPI [19]. In the research community, an example of such a system is an ongoing initiative with Enzian (shown in Figure 2.5), a research computer built at ETH Zurich [101], utilizing the proprietary ECI (Enzian Cache-coherency Interface) protocol [28, 70]. These interconnects, coupled with cache coherency, deliver reduced latency and significantly enhance the "bond" between the host CPU and FPGA devices. Cache coherency,

Xeon FPGA CPU Reconfig. Region Core 1 System Protocol Layer Cache Hierarchy СРЦ Core 2 QPI User Kernel CPU Core N .... RAM Host DRAM

Figure 2.2: Traditional PCIe based platform.

Figure 2.3: Intel HARP v1.

Figure 2.4: Microsoft Catapult.

Figure 2.5: Enzian v3.

in particular, unlocks some interesting use cases that can yield performance benefits in various domains, such as RPC or memory management [132, 61, 60].

Nevertheless, a significant proportion of data flow latency-insensitive workloads (such as analytical database processing or some machine learning algorithms) which involve processing

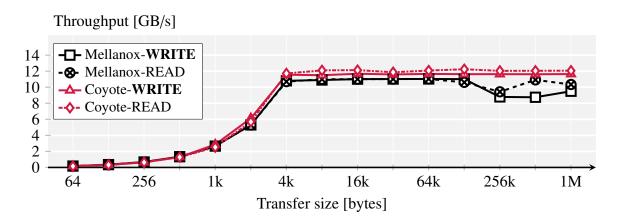

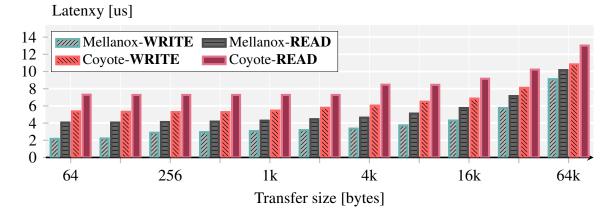

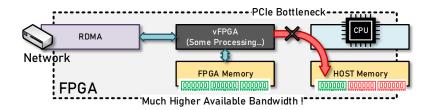

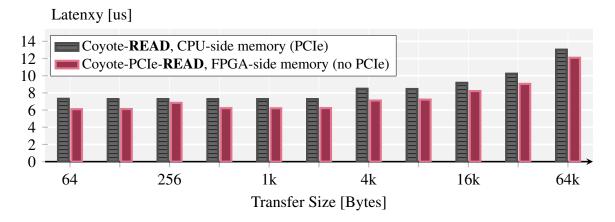

**Figure 2.6:** Interconnect throughput and latency performance comparison (adapted from Enzian paper published at ASPLOS '22 [70].

on streamed data elements within deep pipelines, may not experience substantial benefits from these cache-coherent interconnects. This can be inferred from the experiments done on CXL with Pond [135]. Instead, these workloads are more likely to derive significant advantages from the reliability and comprehensive system support provided by a more conventional peripheral bus. It's worth noting that FPGAs in these configurations have also demonstrated proficiency in handling these types of workloads effectively. While there certainly are latency-sensitive workloads [135], particularly applicable to graph processing algorithms, it remains uncertain to which extent are FPGAs well-suited for these type of fine-grained tasks.

Besides the host interconnect, another crucial and distinctive feature of these hybrid systems incorporating FPGAs is their effortless integration with abundant I/O resources. Usually, this I/O is directly linked to the FPGA fabric, enabling applications within the FPGA to interact with this I/O with minimal overhead. This capability represents a fundamental advantage of FPGAs, as it facilitates the swift transfer of data from the host, memory, storage, network, etc., directly to the processing elements with minimal overhead, serving as the primary source of performance advantages that these devices can yield.

However, a significant challenge arises from the fact that various types of I/O, including highspeed networking, external off-chip memory, storage devices, and external accelerators, each come with their own unique low-level interfaces that often require substantial system software support. Given that FPGAs usually arrive with minimal shells lacking features reminiscent of those found in conventional operating systems, a substantial portion of this I/O often remains underutilized. As an illustrative example, consider the current state-of-the-art AMD Alveo data center cards [12], which boast high-performance 100 Gbps networking interfaces. Surprisingly, the default vendor shell for these devices [207] does not provide any networking support by default, thus leaving this valuable I/O capability untapped. A comparable scenario could be noted with the competing platform, where earlier versions of Intel's HARP [162, 167], shown in Figure 2.3, provided extremely limited support for FPGA side, off-chip memory components.

A critical component in modern computing is the high-performance network interface. Contemporary FPGAs come equipped with high-speed transceivers capable of handling the data rates commonly seen in today's data center networks. This means that FPGAs can seamlessly integrate with the network and directly process incoming and outgoing network packets. Additionally, as mentioned, FPGAs are connected to various other resources, including host CPU memory through PCIe, local FPGA memory, storage, and other network ports. This connectivity allows FPGAs to function as smart Network Interface Cards (NICs) and perform hardware acceleration tasks with minimal impact on data movement. Essentially, FPGAs act as "bumpin-the-wire-processors", making them well-suited for various streaming workloads.

Microsoft Catapult project extensively explored the significance of this capability. It aimed to accelerate network processing for Microsoft's cloud workloads, leveraging FPGAs. One example of a workload that benefited significantly from this acceleration was the page-rank algorithm [62] used in production for Bing searches. Another noteworthy project, BrainWave, demonstrated the effectiveness of FPGAs in large-scale graph neural network inference [68].

Catapult platform stands out among data center heterogeneous platforms due to its unrestricted user access to networking resources. While there are dedicated smart NICs equipped with reconfigurable hardware, they often feature smaller FPGAs and therefore place less emphasis on reconfigurable hardware. Both these dedicated smart NICs and Catapult share a common feature in fully hardened NICs situated outside the FPGA fabric. This design choice, while enhancing NIC performance, imposes limitations on the extent of system-level exploration one can do with these smart NICs as large portions of the system are hardened.

One of the primary advantages of FPGAs is their inherent flexibility, which is derived from their reconfigurable nature. This adaptability is most effectively harnessed through technologies like partial reconfiguration [198]. With partial reconfiguration, specific sections of the FPGA logic can be exchanged with alternative logic "on-the-fly", during runtime, without impacting the functionality of other parts of the FPGA logic. This capability enables users to seamlessly swap accelerators, representing a significant advantage of these devices over more traditional ASIC accelerators.

Regrettably, large-scale heterogeneous platforms rarely offer robust support for partial reconfiguration. While these platforms often employ it for loading the accelerators, there is minimal effort dedicated to providing users with fine-grained control over the reconfiguration process, as it remains largely concealed.

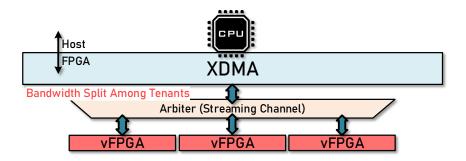

These large-scale cloud platforms consistently offer only single-tenant environments, which poses a significant drawback. This is especially problematic as FPGAs continue to grow in size, and a substantial number of accelerators can be accommodated with just a fraction of the available FPGA resources [126]. Consequently, significant portions of the FPGA fabric remain underutilized, leading to adverse effects on the overall cost, performance and efficiency.

As evident from the information above, the currently available shells and platforms consistently have certain limitations in terms of features and functionalities. Consequently, they offer restricted environments for both research and the deployment of various types of applications. For instance, while a system like Catapult may excel in the context of distributed processing across the network, it may fall short in other areas, lacking support for multi-tenancy, reconfiguration, or any form of virtualization. In general, these frameworks lack fundamental OS abstractions such as multi-tenancy, virtualization, memory management, networking services, etc. This limitation restricts their utility, making them highly specialized and somewhat counterproductive for leveraging the inherent flexibility of such hardware.

Moreover, these frameworks come with intricate interfaces, rely on proprietary hardware and software IP, and entail a steep learning curve for developers. System abstractions present on one platform will typically be absent or markedly different when transitioning to other platforms. Thus achieving portability across these platforms becomes a challenging task, with minimal opportunities for cross-compatibility.

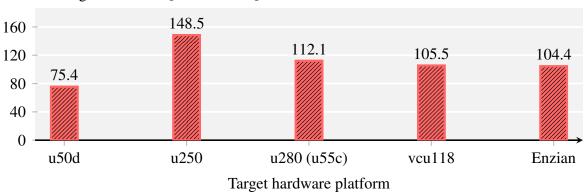

We developed *Coyote* to overcome the mentioned limitations. Currently, Coyote is compatible with a wide array of AMD Alveo data center cards, including models such as Alveo-U250, Alveo-U280, Alveo-U55C, Alveo-U50D, and Alveo-U200 [8, 9, 10, 15, 14]. In addition to the aforementioned compatibility with AMD Alveo data center cards, Coyote is also capable of running seamlessly on Enzian [70]. This real-world example serves as concrete evidence of the essential portability aspect of the entire system.

A central component of Coyote's design is the establishment of a multi-tenant environment, akin to the structure of a traditional microkernel. Significantly, this environment additionally provides a spectrum of services that are available to all tenants. These services, including virtualization, memory and network stacks, play a pivotal role in boosting productivity on these

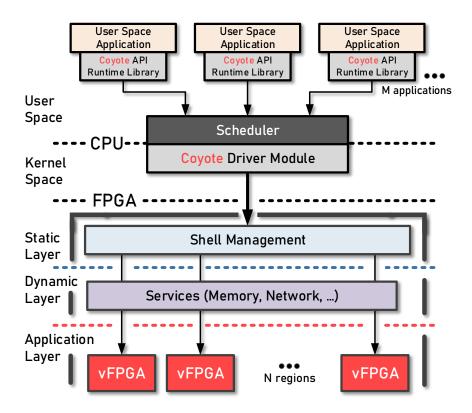

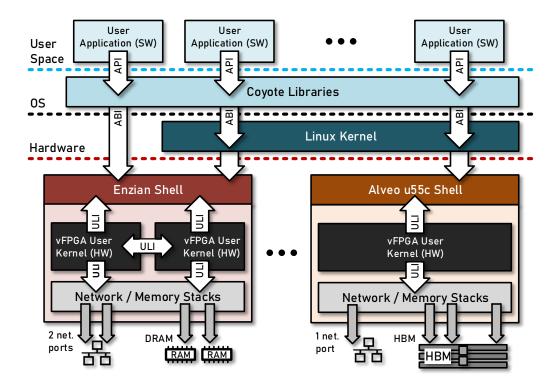

Figure 2.7: Coyote high level overview of the system architecture.

devices. Importantly, we have deliberately steered clear of any design choices that could hinder the utilization of modern FPGA capabilities, such as dynamic partial reconfiguration of multiple regions or valuable "hard" on-chip functions.

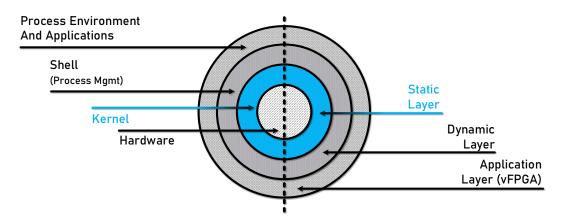

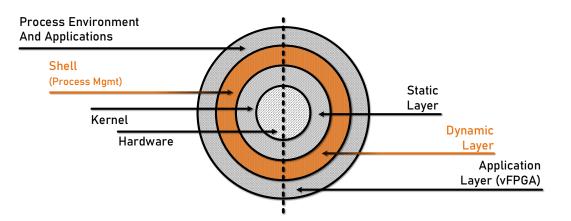

A high-level overview of Coyote is depicted in Figure 2.7. The framework architecture is naturally divided into two primary components. The first component resides in the "hardware" realm and runs on the FPGA, while the second component operates on the host CPU, as part of the OS and support libraries.

#### 2.2.1 The Hardware "Split"

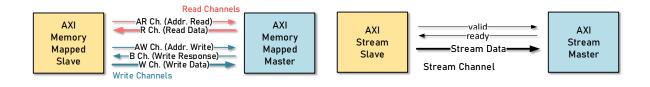

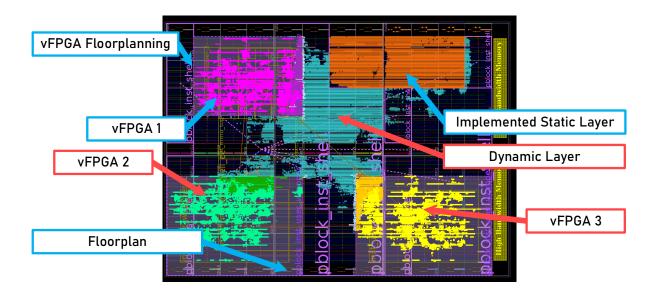

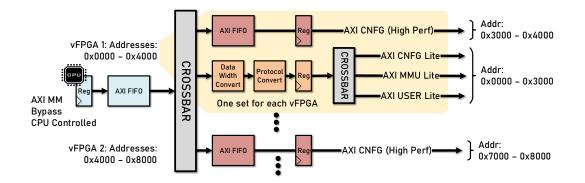

As is customary in the cutting-edge shell designs, dynamic reconfiguration of the FPGA induces a further split of the hardware component into a "static region", configured at boot, and a "dynamic region", containing subregions (vFPGAs), each of which may be changed on the fly. This split exists (often in simplified form) in all FPGA datacenter deployments. Within and between regions, it is customary for hardware components to interact via interconnects like AXI [145]. The AXI (Advanced eXtensible Interface) protocol stands as a widely embraced and standardized interface within the areas of digital design and computer engineering. Its primary function is to enable seamless communication among diverse hardware components residing within SoCs, FPGAs, or ASICs. This protocol is crafted to enhance performance, scalability, and the ease of integration within digital systems.

Within the context of Coyote, both full AXI4 memory-mapped interfaces and AXI4 streaming protocol (a specialized iteration of AXI optimized for continuous data flows) are employed. The streaming protocol, which uses a simple handshaking logic, is particularly well suited for the creation of intefaces exposed to the end user applications. This protocol represents the preferred choice within Coyote. We'll postpone deliberating on this selection for a later time (Section 3.1.1).

#### 2.2.1.1 Static Layer

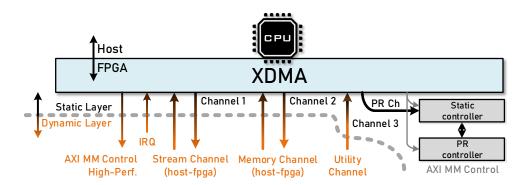

The FPGA static layer must contain the functionality required to reconfigure the dynamic layer and communicate with the CPU's OS. This layer needs to contain only the essential features which support the operation of user applications and this is indeed the case for most of the vendor shells out there.

In Coyote, the static layer always contains logic to partially reconfigure portions of the dynamic layer, communicate with the host machine (a DMA copy engine), and to divide the dynamic region into a set of *virtual FPGAs* ("vFPGAs"), each of which has an interface mapped into the physical address space of the host CPU.

Considering that Coyote is designed for data center applications and is typically deployed within large clusters, it's essential to highlight that the static layer remains in a constant state of being "online". This continuous availability ensures that logic within the FPGA can be adapted and modified without the necessity of taking the entire system offline or resorting to procedures like cold reboots.

It's important to note that this layer is the sole layer in Coyote that is inherently platformdependent. Currently employed approach is to maintain it internally under strict version control for all platforms. However, given that Coyote is an open-source research project, users have the flexibility to experiment and explore various configurations and modifications within this layer at any given time (at their own risk).

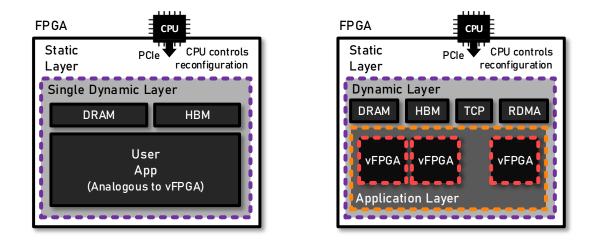

Figure 2.8: Amazon F1 FPGA shell reconfiguration. Figure 2.9: Coyote FPGA shell reconfiguration.

However, what truly sets Coyote apart from similar systems is its dynamic layer. Its uniqueness is found in how multi-tenancy and FPGA-based services come together and interact within this layer.

#### 2.2.1.2 Dynamic (Service) Layer

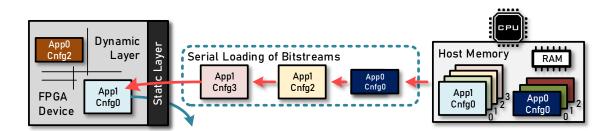

The dynamic region is the basic mechanism for time-division multiplexing of the FPGA resources. Modern FPGAs allow selective portions of this region to be reconfigured independently at any time.

Most deployed systems (e.g. F1 [30] and Intel's HARP [162]) dedicate this region to a single application, and reprogram it only rarely with large overheads (e.g. when an associated virtual machine on the host is booted up).

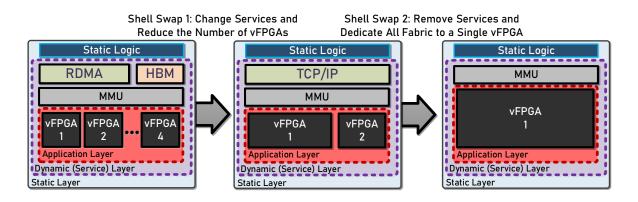

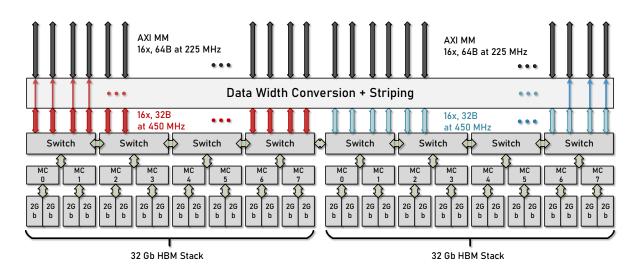

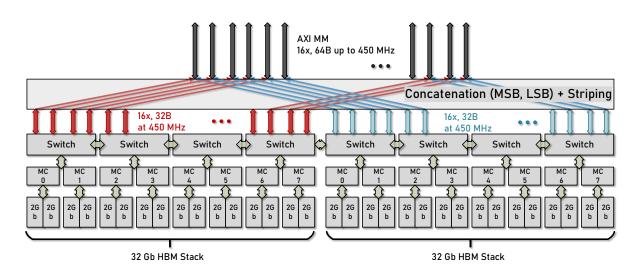

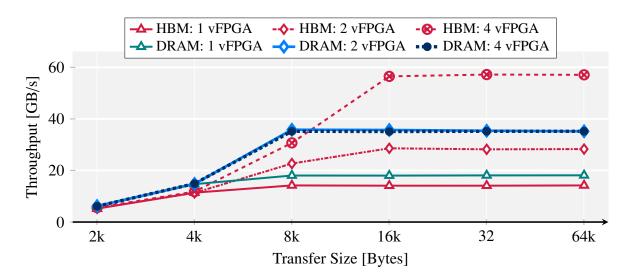

Space (chip area, logic blocks, wires, etc.) remains a scarce resource on FPGAs, and unlike OS resources such as CPU time and virtual memory, it is hard to make it "elastic" through virtualization. Moreover, services like memory stacks (HBM, DRAM) and networks stacks (TCP/IP, RDMA) contain large complexity and use significant FPGA resources, thus it is is important to make these components optional so they can be ommited if not needed. Additionally, the number of tenants can also change dynamically, thus all of these modules need to be part of the dynamic fabric which can be configured on-the-fly to best utilize the available resources. Coyote supports multi-tenancy as its core abstraction, further extended by the inclusion of system-wide services. Each tenant within the system can be reconfigured independently without impacting other tenants. This concept closely aligns with the notion of processes in operating systems. This stands in sharp contrast to traditional single-tenant shells, which always allocate the dynamic region to a single application.

Coyote introduces added complexity through its system-wide services. These services are utilized collectively by all tenants and cannot be merged within the same dynamic regions as the applications. The creation of distinct dynamic regions for each service is also not a viable solution, as it would lead to notable congestion and floorplanning challenges (dynamic regions come with strict resource and floorplanning requirements). Moreover, these services cannot be interchanged as freely as applications and typically operate at a lower level within the notion of the operating systems.

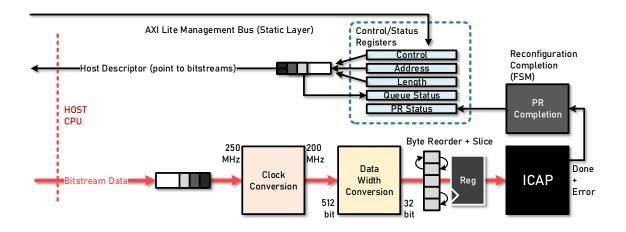

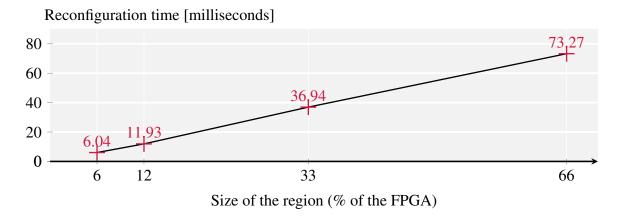

To address this complexity, Coyote employs a solution by using *hierarchical dynamic reconfiguration*. This approach allows for the creation of layers within layers of reconfigurable regions, granting the flexibility to not only swap dynamic user applications but also the services that serve these applications. A comprehensive explanation of the hierarchical reconfiguration approach in Coyote will be provided later on in Chapter 3.3. Both the service layer (memory and network stacks) and the application layer are integral components of the dynamic layer within Coyote.

#### 2.2.1.3 Application Layer

At the application layer, Coyote, much like other recent systems [212, 86, 64, 210], offers flexible spatial and temporal multiplexing. The application layer is divided into independent *virtual FPGAs* (vFPGAs), enabling the concurrent execution of multiple applications and their seamless switching in and out. Since the entire layer is part of the overarching dynamic layer, the number of these vFPGAs is a compile-time parameter determined by the shell. Different versions of the dynamic layer loaded during runtime can accommodate varying numbers of vFPGAs. This adaptability can also be leveraged for efficient resizing and scheduling of user applications based on current occupancy.

A novel aspect of Coyote is its division of each vFPGA into two components: the *user logic* and the *user wrapper*. The user logic consists of a bitstream that is entirely synthesized by a Coyote user, subsequently validated by the system, and contains both trusted and untrusted segments. It is crucial to emphasize that the user logic is regarded as untrusted, and precautions are implemented to prevent users from potentially engaging in malicious actions that could impact

the system adversely. Furthermore, the Coyote management layer maintains the capability to remove the entire state of the user logic at any given moment, if deemed necessary.

It is tempting to draw an analogy between the structure of Coyote and a microkernel model of an OS, consisting of the kernel (the static layer), services (the service layer), system libraries (the dynamic layer), applications code (the application layer) and user processes (vFPGAs). However, this would not be entirely correct. For example, the user wrappers in the dynamic layer form part of a trusted computing base (TCB), whereas system libraries in a microkernel do not. Nonetheless, this analogy retains significance and can serve as a simple means to visualize the layers in Coyote.

The user wrapper is part of Coyote, and both sandboxes user logic and imporantly provides a set of standard interfaces to the rest of the system (in FPGA terms, partition pins are inserted by the reconfiguration tool locking all the boundary interface signals in the fabric). This incurs a cost in chip area usage (same applies to the above service/dynamic layer), but the benefit is that Coyote pushes the "portability layer" for FPGA applications up to the language level: an application written for Coyote can, given sufficient resources, be synthesized to run on any Coyote FPGA. In contrast, with native FPGA development at present, code is rarely portable between device models (or even, in some cases, revisions of the same model).

We will dive into a more in-depth examination of the *Unified Logic interface* available to users in a later Section 5.1. At this point, it's worth noting that this interface primarily comprises straightforward AXI streams, offering significant flexibility in programming models. Due to the straightforward nature of these streaming interfaces and their broad range support, developers in Coyote can create applications using a variety of language models, including traditional Hardware Description Languages (HDL), various forms of High Level Synthesis (HLS), or even a blend of these and other programming languages.

Traditional hardware description languages (HDLs) such as Verilog and VHDL function at the Register Transfer Level (RTL), allowing the description of circuits using either behavioral or structural representations. This facilitates fine-tuning of designs to achieve optimization in both resource utilization and performance and thus most of Coyote's infrastructure is in HDL.

HDLs offer an excellent abstraction for hardware development demanding utmost precision. However, it's crucial to acknowledge that, especially when working at the application level, achieving efficient utilization can be challenging due to the need for a profound grasp of the microarchitectural specifics, spatial characteristics, and timing constraints inherent to the target device, which can potentially hinder productivity. Listing 2.1: Top Level HLS code of the *Hyper-Log-Log* operator in Coyote.

```

1 void hyper_log_log (

2

// Coyote Host Streams

3

hls::stream<ap_axiu<AXI_DATA_BITS, 0, PID_BITS, 0> >& axis_host_sink,

4

hls::stream<ap_axiu<AXI_DATA_BITS, 0, PID_BITS, 0> >& axis_host_src,

5

// Coyote CSR

6

7

ap_uint<64> axi_ctrl

8){

9

#pragma HLS DATAFLOW disable_start_propagation

10

#pragma HLS INTERFACE ap_ctrl_none port=return

11

#pragma HLS INTERFACE axis register port=axis_host_sink name=s_axis_host_sink

12

#pragma HLS INTERFACE axis register port=axis_host_src name=m_axis_host_src

13

#pragma HLS INTERFACE s_axilite port=axi_ctrl bundle=control

14

15

// Hyper Log Log Kernel

16

hyper_log_log_compute(s_axis_host_sink, m_axis_host_src, axi_ctrl);

17 }

```

These challenges associated with using HDLs are widely recognized, and as a result, considerable effort has been dedicated to the development of high-level synthesis (HLS) languages to simplify FPGA programming. Modern tools like Vitis [207] and Intel HLS [109], for example, employ the syntax of conventional programming languages such as C. These tools abstract the intricacies of hardware, apply traditional software compiler optimization techniques, and ultimately transform a program into a hardware representation through allocation and scheduling processes. For these productivity reasons, the decision to use streaming interfaces was significant because they enjoy strong support within HLS. This choice enables Coyote and its interfaces to seamlessly support HLS kernels without requiring additional modifications. Listing 2.1 shows the top level of the Hyper-Log-Log operator written in HLS for Coyote.

Unfortunately, extracting parallelism from sequential HLS code is a challenging task, necessitating users of such compilers to provide extra input and hints to the compiler to achieve a reasonable level of result quality. Tools like Xilinx's HLS or Intel's OpenCL heavily rely on programmers adding "pragmas" [207] to specify where and how to parallelize the final design. Pragmas enable developers to annotate code with additional information that compilers or HLS tools can utilize, such as marking loops as parallelizable or pipelining specific code sections, but add a layer of complexity to otherwise very C like code.

While HLS can undoubtedly enhance productivity in hardware development, it's worth noting that significant portions of the code written in these languages deviate from the conventions of traditional C code and frequently adhere to typical hardware programming patterns [138], which

can additionally make the code difficult to debug [85].

Therefore, while HLS is a valuable tool, it may not provide an ultimate solution, and having the ability to combine both traditional HDL and HLS support is a preferable option. The interface choice in Coyote facilitates this possibility.

#### 2.2.2 Host System Software

In a hybrid system, the host operating system must clearly be aware of the FPGA environment, and also provide suitable and safe abstractions to user application code running on the CPU for interacting with user logic on the FPGA.

Beyond this, however, there is a fundamental tradeoff between how much management of FPGA resources is performed on the FPGA itself (by a combination of static region logic and dynamic functionality) and how much is implemented by system software on the CPU. Offloading FPGA management functionality to the CPU and OS frees up valuable space on the FPGA, and allows much more policy flexibility than could be reasonably implemented in logic. Hovewer a functionality that is on a critical path can lead to degraded performance and/or loss of predictability in response time (often a key attribute of hardware solutions). In some ways this mirrors the traditional OS tradeoff between kernel-mode and user-space implementation, but the contrast is more stark.

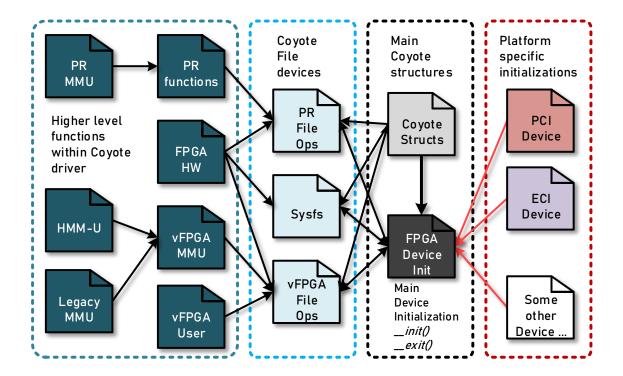

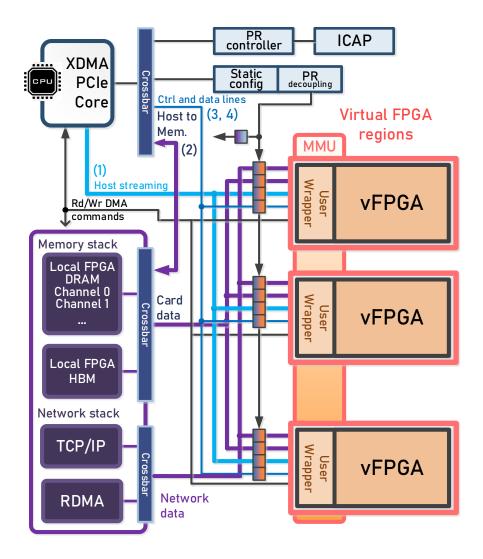

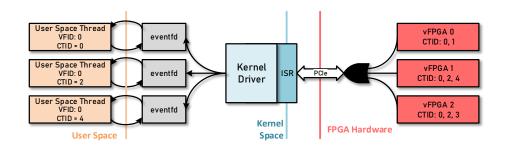

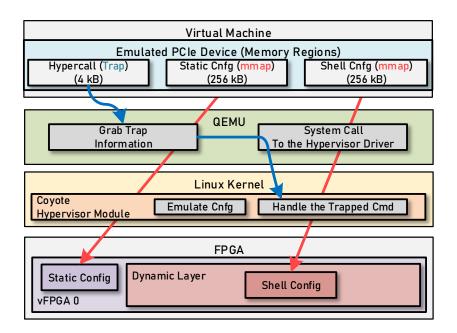

Coyote maximizes the FPGA area allocated for user logic by offloading many non-essential functionalities onto the host CPU's operating system. The software component of Coyote comprises a kernel *driver* that handles most of the core operations (currently designed for Linux), a *runtime manager* process, and user application code.

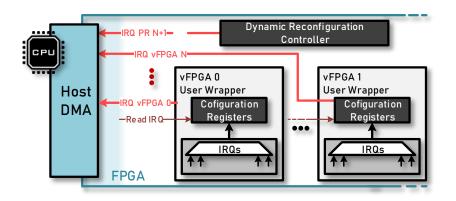

#### 2.2.2.1 Kernel Driver

During startup, the driver reads the configuration of the static layer on the FPGA and establishes the initial data structures required to support the system's operation within the cluster. At this point, the driver can be directed to load different versions of user supplied *dynamic shells* with various configurations of virtual FPGAs (vFPGAs) and associated services. Subsequently, it creates *character file devices* for each of these vFPGAs, which are then exposed in the Linux kernel. In addition to this a separate character device is created for reconfiguration purposes.

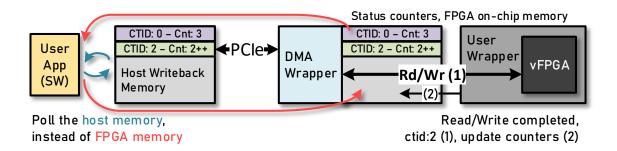

These character devices constitute the main interface between the Coyote driver and the user space applications. Communication between the user space and the driver is achieved through system calls, with a significant portion involving the use of functions like *mmap* and *ioctl*.

The *mmap* calls are employed to directly map various memory locations from hardware directly into user space, allowing Coyote to bypass the kernel in many instances. These direct memory mappings offer substantial performance advantages for a wide range of tasks, including any kernel invocations, initiating data transfers, and launching network calls such as Remote Direct Memory Access (RDMA), among others. This approach bears similarities to DPDK [11] (Data Plane Development Kit) in that it shifts a substantial portion of functionality (in DPDK's case typically related to networking), into user space, circumventing the kernel and thereby improving efficiency.

The *ioctl* calls function as a method for general communication between user space libraries and the Coyote kernel driver. This interface has proven to be reliable and well-established in controlling device drivers. It is also extensible as it allows easy incorporation of new commands. Importantly, it can be utilized through character devices and sockets, which are the main file descriptors used within the Coyote framework.

The *sysfs* file system serves as the default status and debugging tool provided by Coyote. It enables the exposure of various hardware parameters for transparent configuration. Additionally, it provides access to various live system information, facilitating simple debugging and monitoring processes.

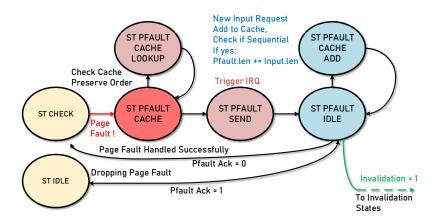

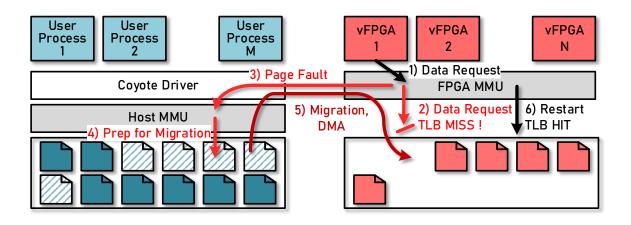

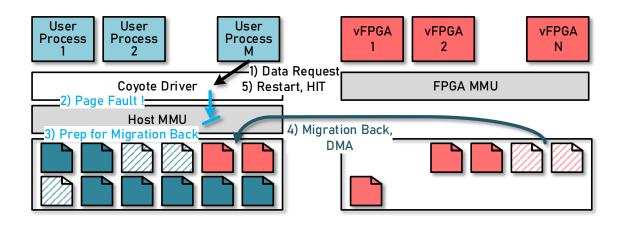

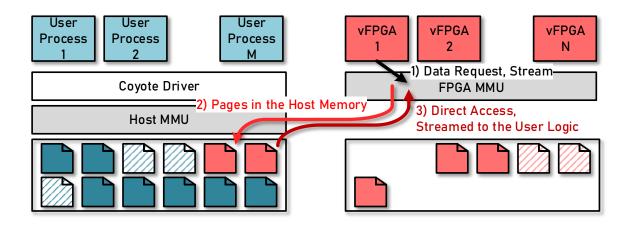

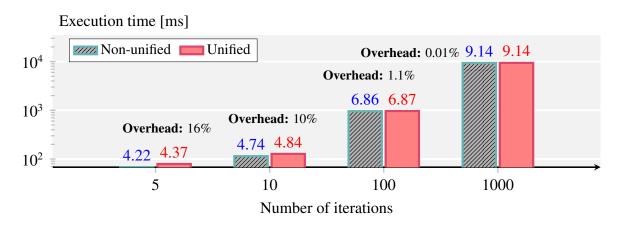

The kernel driver also manages the broader control plane communication with the FPGA. This includes tasks like reconfiguring a vFPGA and establishing memory mappings to enable direct interaction between application code and a vFPGA. Additionally, the driver has several other duties, including dynamic memory allocation, processing user notifications from hardware, managing page faults, addressing TLB misses, overseeing memory migrations, and more.

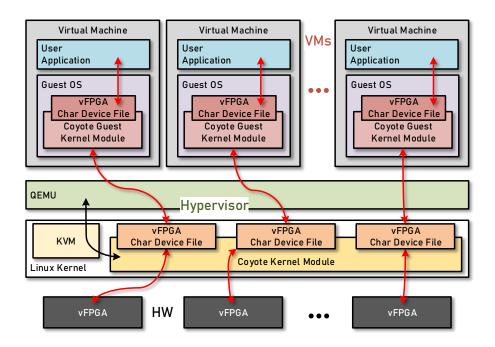

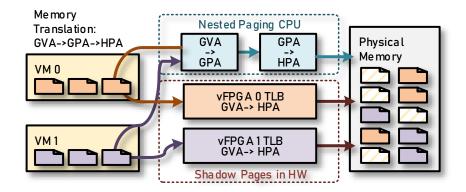

The Coyote driver also operates as a *hypervisor*, providing the system with the capability to run virtual machines on top of individual hardware processes (vFPGAs). This represents the ultimate layer of hardware abstraction and isolation that Coyote provides.

#### 2.2.2.2 Runtime Manager and API

Coyote's runtime manager operates within user space. This component of the system software takes on the role of coordinating interactions among numerous concurrent software users and

the corresponding multi-tenant hardware in the FPGA. It is responsible for scheduling usersubmitted tasks. Thus, it manages partial reconfigurations and handles all communication with the reconfiguration character device. The decision to implement this layer in user space, as opposed to kernel space, is grounded in two key advantages: 1) it allows us to bypass potential kernel overhead, and 2) it leverages the extensive array of user space libraries to simplify the implementation of scheduling tasks.

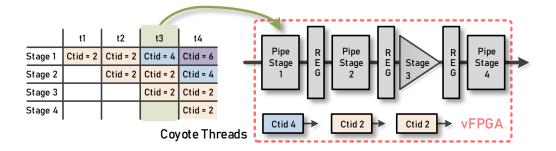

In Coyote, the Application Programming Interface (API) offers additional abstractions aimed at harnessing the potential for parallelization on both the FPGA and CPU sides. The central abstraction provided by this API is the *Coyote thread*. This object represents a singular thread of execution within the hardware pipelines in vFPGAs. In this way, it can be described as a hardware thread running within hardware processes (vFPGAs). Each Coyote thread is also linked to its corresponding software thread of execution (standard POSIX threads [1]). Users have the flexibility to submit their arbitrary tasks to these threads and distribute them between hardware and software execution as desired.

# 2.3 OS abstractions on an FPGA

Now that we have covered the fundamental aspects of Coyote, we will go into a discussion about traditional OS abstractions and how they can potentially be applied to heterogeneous devices. In the upcoming chapters, we will examine the detailed implementation of Coyote's abstractions. For each OS abstraction under consideration, we will begin by reviewing its role in a conventional OS designed for homogeneous multicore machines. We will then explore what fundamentally differs in an FPGA environment and how this impacts the design decisions when creating an equivalent abstraction on the FPGA.

#### 2.3.1 Processes, Threads, and Tasks

Most operating systems offer fundamental abstractions for efficiently managing and virtualizing processor resources. These abstractions typically revolve around processes, threads, and/or tasks, and they play a pivotal role in enhancing the user experience. While precise definitions can differ between operating systems, a thread typically represents an ongoing execution of a set of instructions on a single virtual processor. A task, represents a discrete unit of computational work that can be assigned to a CPU core. Meanwhile, a process is typically a collection of threads that share a common address space, isolated from other processes, to which CPU resources are allocated.

The hardware mechanisms underlying these abstractions are basically the ability of the processor to context switch, and be preempted by an interrupt or trap.

Such abstractions can be readily adapted to architectures like GPUs, which retain the notion of a hardware thread, albeit with a very different degree of parallelism. GPU drivers for modern OSes attempt to extend the process abstraction of the host CPU to the GPU, although in a somewhat limited form [51], and this is the foundation for programming models like CUDA and OpenCL. The task abstraction has also been successfully deployed on GPUs [178].

#### What's Different on an FPGA?

Resource multiplexing on FPGAs is fundamentally different, since there is no hardware entity corresponding to a "processor", "core", or "hardware thread" on which to base an abstraction aimed at multiplexing processing resources.

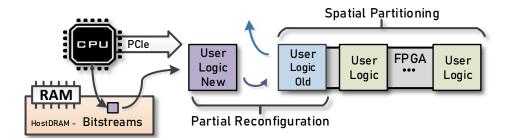

Instead, two basic mechanisms (Figure 2.10) available on the FPGA for multiplexing compute resources between different users are:

- **Spatial partitioning** of the application logic within the FPGA fabric. This is also one of the primary techniques for optimizing FPGA utilization and performance.

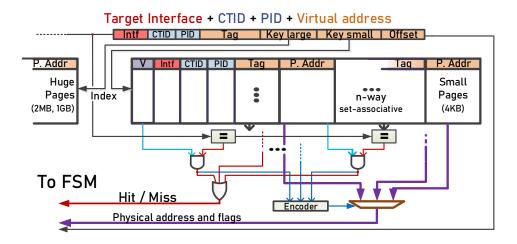

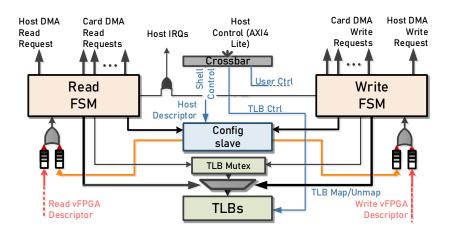

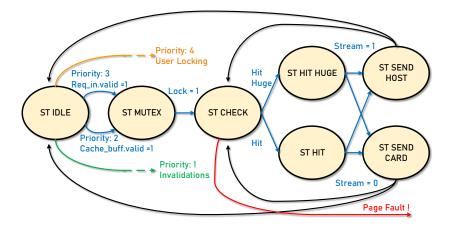

- **Partial reconfiguration** where certain portions of the FPGA logic are swapped during runtime, all while leaving the rest of the fabric unaffected in its operation.