## **ETH** zürich

# Scaled, Ferroelectric Memristive Synapse for Back-End-of-Line Integration with Neuromorphic Hardware

#### **Journal Article**

#### Author(s):

Bégon-Lours, Laura; Halter, Mattia; Puglisi, Francesco Maria; Benatti, Lorenzo; Falcone, Donato Francesco; Popoff, Youri; Dávila Pineda, Diana; Sousa, Marilyne; Offrein, Bert Jan

Publication date: 2022-06

Permanent link: https://doi.org/10.3929/ethz-b-000538271

Rights / license:

Creative Commons Attribution-NonCommercial-NoDerivatives 4.0 International

#### Originally published in:

Advanced Electronic Materials 8(6), https://doi.org/10.1002/aelm.202101395

#### Funding acknowledgement:

732642 - Ultra-Low Power Event-Based Camera (SBFI) 871737 - BEOL technology platform based on ferroelectric synaptic devices for advanced neuromorphic processors (EC)

### Scaled, Ferroelectric Memristive Synapse for Back-End-of-Line Integration with Neuromorphic Hardware

Laura Bégon-Lours,\* Mattia Halter, Francesco Maria Puglisi, Lorenzo Benatti, Donato Francesco Falcone, Youri Popoff, Diana Dávila Pineda, Marilyne Sousa, and Bert Jan Offrein

Ohmic, memristive synaptic weights are fabricated with a back-end-of-line compatible process, based on a 3.5 nm HfZrO<sub>4</sub> thin film crystallized in the ferroelectric phase at only 400 °C. The current density is increased by three orders of magnitude compared to the state-of-the-art. The use of a metallic oxide interlayer, WO<sub>y</sub>, allows excellent retention (only 6% decay after 10<sup>6</sup> s) and endurance (10<sup>10</sup> full switching cycles). The On/Off of 7 and the small device-to-device variability (<5%) make them promising candidates for neural networks inference. The synaptic functionality for online learning is also demonstrated: using pulses of increasing (resp. constant) amplitude and constant (resp. increasing) duration, emulating spike-timing (resp. spike-rate) dependent plasticity. Writing with 20 ns pulses only dissipate femtojoules. The cycle-to-cycle variation is below 2%. The training accuracy (MNIST) of a neural network is estimated to reach 92% after 36 epochs. Temperaturedependent experiments reveal the presence of allowed states for charge carriers within the bandgap of hafnium zirconate. Upon polarization switching, the screening of the polarization by mobile charges (that can be associated with oxygen vacancies and/or ions) within the ferroelectric layer modifies the energy profile of the conduction band and the bulk transport properties.

#### **1. Introduction**

Artificial neural networks, by analogy with the brain, consist of collections of interconnected neurons. The information

L. Bégon-Lours, M. Halter, D. F. Falcone, Y. Popoff, D. Dávila Pineda, M. Sousa, B. J. Offrein

IBM Research Europe – Zurich Research Laboratory Rüschlikon CH-8803, Switzerland E-mail: Ibe@zurich.ibm.com

M. Halter, Y. Popoff ETH Zurich – Integrated Systems Laboratory Zurich CH-8092, Switzerland

F. M. Puglisi, L. Benatti UNIMORE – Dipartimento di Ingegneria "Enzo Ferrari" Modena 41125, Italy

The ORCID identification number(s) for the author(s) of this article can be found under https://doi.org/10.1002/aelm.202101395.

© 2022 The Authors. Advanced Electronic Materials published by Wiley-VCH GmbH. This is an open access article under the terms of the Creative Commons Attribution-NonCommercial-NoDerivs License, which permits use and distribution in any medium, provided the original work is properly cited, the use is non-commercial and no modifications or adaptations are made.

#### DOI: 10.1002/aelm.202101395

flows from a layer of neurons to another, through vector-matrix multiplications (VMM). Tasks such as classification are possible by training the network, i.e., adjusting the matrix elements or "synaptic weights." Analog,<sup>[1]</sup> in-memory<sup>[2,3]</sup> as well as neuromorphic<sup>[4,5]</sup> computers aim at implementing the VMM in the analog domain:<sup>[6,7]</sup> the "multiply" (through Ohm's law) and "accumulate" (through Kirchhoff's law) operation is performed by a parallel voltage drop through a cross-bar array of nonvolatile, programmable resistances. Different technologies exist for memristive devices: phase-change memory,<sup>[8]</sup> filamentary-based resistive random access memory,<sup>[9]</sup> and electrochemical memory<sup>[10]</sup> rely on ion motion, with intrinsic limitations. In contrast, ferroelectric synaptic weights rely on electrostatic effects: for example, Schottky barrier height<sup>[11]</sup> or width<sup>[12]</sup> modulation, or electrostatically induced metal-insulator transitions.<sup>[13]</sup> The neuromorphic computers' learning

paradigms (unsupervised<sup>[14,15]</sup> or supervised<sup>[16,17]</sup>) require the ferroelectric memristive devices to show synaptic behavior, i.e., the ability to gradually decrease (depression) or increase (potentiation) their conductance upon voltage pulses emulating the effect on biological synapses of the pre- and postsynaptic spikes emitted by the neurons. Cointegrating ferroelectric materials with CMOS neurons became possible with the discovery of ferroelectricity in hafnia compounds.<sup>[18]</sup> In the race to miniaturization of front-end-of-line (FEOL) devices, logic functions and discrete multilevel memories are demonstrated at the 28 and even 22 nm node.<sup>[19]</sup>

Fabrication in the back-end-of-line (BEOL) relaxes the constraint on the device size, which can exceed micrometric dimensions: large numbers of nanometric ferroelectric domains can be contained in the active device area, allowing multilevel and/or analog conductance level updates, as demonstrated, for example, in field-effect transistors<sup>[20]</sup> and in metal–ferroelectric–insulator–metal (MFIM) devices. Based on thick HfO<sub>2</sub> layer, the band diagram of these two-terminal devices is engineered such that the electrons tunnel through the insulator, and partially through the ferroelectric.<sup>[21,22]</sup> These devices have a large dynamic range (>10), but suffer from a small current density ( $10^{-8}$  A cm<sup>-2</sup> at 2 V), operate at voltages larger than 5 V (but ±8 V); and their large nonlinearity (which can be circumvented by

the use of a logarithmic driver<sup>[3]</sup>) limit their usage for VMM. Furthermore, the dielectric interlayer is responsible for moderate retention<sup>[23]</sup> and endurance<sup>[24]</sup> performances. In contrast, in metal-ferroelectric-semiconductor (MFS) devices, the electrons see the full thickness of the ferroelectric. In the back-end, the process temperature cannot exceed 400 °C. 5-15 nm thick Hafnia films grown by atomic layer deposition can be crystallized in the ferroelectric phase with a moderate thermal budget by rapid thermal annealing,<sup>[25]</sup> laser annealing,<sup>[26]</sup> or millisecond-flash lamp annealing<sup>[27–29]</sup> but they result in low current densities. By decreasing the thickness, the current density increases, but at the cost of a higher thermal budget required for crystallizing the film, as shown in ref. [30] where 4 nm thick HZO requires 500 °C. As in ref. [31], where 600 °C are required to crystallize 5 nm of HfZrO<sub>4</sub> (HZO), ferroelectricity was demonstrated but not resistive switching. Ali et al.<sup>[32]</sup> reported synaptic functionality in HZO/Al<sub>2</sub>O<sub>3</sub> bilayers with HZO thickness of 6 nm, but found that the On/Off ratio vanishes from 4 to 1 for 4 nm thick films, both crystallized at 800 °C.

In this work, ferroelectricity was obtained in a TiN/WO<sub>r</sub>/ HZO/TiN structure with an HZO film as thin as 3.5 nm crystallized at 400 °C, a thermal budget compatible with back-endof-line. Compared to synaptic weights based on a 5 nm thick HZO layer fabricated in the same conditions<sup>[29]</sup> and to stateof-the-art MFIS HfO2(10 nm)/Al2O3 bilayers,[21,22] the current density is three and six orders of magnitude higher respectively, drastically reducing their footprint. Their synaptic functionality, endurance, and retention properties were characterized. By thinning the HZO from 5<sup>[29]</sup> to 3.5 nm, the On/Off at 100 mV was reduced from 10 to 7, but the maximum voltage for linear read-out was increased from 30 to 70 mV. In addition, the cycleto-cycle variation was improved from 10% to 2%. The synaptic weights were further integrated in a passive cross-bar array configuration. The performance of a neural network based on this technology was estimated. The conduction mechanisms across the device, as well as the mechanisms governing the resistive switching, were explored using structural and ferroelectric characterization, as well as temperature dependent electrical measurements.

#### 2. Ferroelectricity in Ultrathin, Back-End Compatible Bilayer

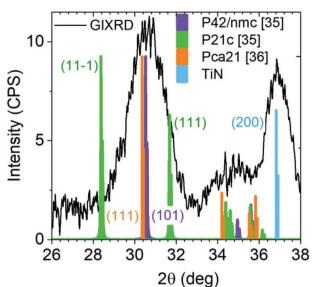

TiN, WO<sub>3</sub>, HfZrO<sub>4</sub> (HZO), and TiN layers were deposited by plasma-enhanced atomic layer deposition (PE-ALD) on an SiO<sub>2</sub> buffered Si substrate. The role of the WO<sub>x</sub> interlayer, as discussed in ref. [33], is to induce an asymmetry in the energy profile of the memristor, leading to a resistive switching effect driven by the ferroelectric domain switching. TiN was chosen as a capping layer to promote the crystallization of HZO in the ferroelectric phase by a mechanical constraint during the annealing.<sup>[34]</sup> HZO was preheated to 400 °C, then a 20 ms long energy pulse of 90 J cm<sup>-2</sup> was applied to crystallize it in the orthorhombic/tetragonal phase, without any fraction of the monoclinic phase, as is confirmed by the grazing incidence X-rays diffraction scan in **Figure 1**. For comparison, the green

Figure 1. GIXRD scan of the device stack after crystallization (black curve). The green lines (resp. purple) correspond to the monoclinic HZO (resp. tetragonal ZrO<sub>2</sub>) in Materlik et al.,<sup>[35]</sup> the orange lines to the orthorhombic HZO in Müller et al.,[36] the blue lines to TiN (CIF 1011102). X-ray reflectivity (Figure S1a, Supporting Information) confirms sharp interfaces and an ultralow HZO thickness of 3.5 nm. To confirm the back-end-of-line compatibility of the crystallization process, the same annealing was performed on MOSFETs (130 nm). The drain current as a function of the gate voltage characteristics of the annealed transistors fell within the spread of the characteristics of the pristine transistors. During the whole process, tools and temperatures compatible with back-end-of-line conditions were used: the devices were defined by optical lithography and reactive ion etching. The HZO, WO<sub>x</sub>, and bottom TiN layer were etched using inductive coupled plasma with a CF<sub>4</sub> chemistry. The sputtered W metal lines were isolated by a SiO<sub>2</sub> spacer, deposited by plasma-enhanced chemical vapor deposition at 300 °C, as sketched in Figure S2 (Supporting Information). Devices with top electrode diameters comprised between 10 and 30  $\mu$ m are fabricated. In the following sections, devices of 22 µm are chosen: their resistance around 10  $M\Omega$  is easily measurable with standard source measurement units.

lines (resp. purple) correspond to the monoclinic HZO (resp. tetragonal ZrO<sub>2</sub>) in Materlik et al.,<sup>[35]</sup> and the orange lines to the orthorhombic HZO in Müller et al.<sup>[36]</sup> The peak at  $2\theta = 37^{\circ}$  is attributed to TiN (CIF 1011102). Fitting the peak at  $2\theta = 30.2^{\circ}$  by a Gaussian with a width at half maximum of  $w = 1.7^{\circ}$ , using a k factor in the range 0.7–0.94, would lead to an in-plane crystallite size of d = 3.8-5.0 nm (Scherrer equation:<sup>[37]</sup>  $d = k \lambda_{k\alpha 1}^{Cu} / (w \cos \theta)$ ). To get more insight on the microstructure of the film, high-resolution bright field scanning transmission electron microscopy (BF-STEM) image was acquired around the HZO/WO<sub>x</sub> region of a cross section of the device and is presented in Figure S1b (Supporting Information). It reveals that the HZO grains have a typical in-plane dimension above 10 nm, indicating that the broadening of the GIXRD peak at  $2\theta = 30.2^{\circ}$  could be due to the presence of the tetragonal phase of HZO. The STEM analysis confirms the polycrystalline nature of the top and bottom TiN electrodes and of the HZO layer. It also reveals a columnar growth of the bottom TiN layer which translates into a slight  $WO_x$  and HZO roughness.

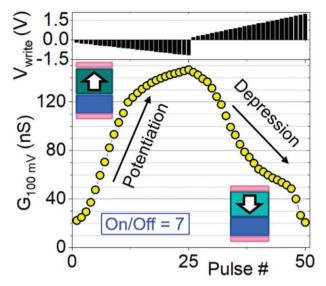

**Figure 2.** Potentiation and depression of the device upon DC pulses (the duration of the bias depends on the amplitude) of increasing amplitude  $V_{\text{write}}$ . The On/Off ratio is the maximal conductance divided by the minimal conductance.

#### 3. A Ferroelectric Synaptic Weight

#### 3.1. DC Resistive Switching

Potentiation (depression) of the two-terminal device was first obtained by applying a negative (positive) DC "pulses" of decreasing (increasing) amplitude with respect to the grounded TiN/WO<sub>x</sub> electrode. In this DC configuration, the duration of the bias is not parametrized and decreases as the current flowing through the device, thus the amplitude, increases. After the application of each pulse of amplitude  $V_{\text{write}}$  (that varies in the -1.4 to 1.6 V range) the bias was set back to zero, then the conductance was measured at 100 mV, as shown in Figure 2 (yellow data points). In the high resistive state (HRS), the HZO polarization points toward the WO<sub>x</sub> layer (blue layer in the sketch in Figure 2). Upon the application of an increasing positive bias, the fraction of domains whose polarization points away from the  $WO_x$  layer gradually increases. The On/Off ratio, defined as the ratio of the device conductance in the low resistive state (LRS) and in the HRS is 7. More than 25 levels can be clearly distinguished. The nonlinearity of the long-term potentiation and depression was quantified by fitting the normalized data represented in Figure 2, by a function of the normalized

pulse number  $\gamma: x \to \frac{1 - e^{(-\frac{x}{A})}}{1 - e^{(-\frac{1}{A})}}$ , as proposed in ref. [38]. The para-

meter *A* was chosen by minimizing the root mean square error of the fitting. Values of  $A_{LTP} = 0.5$  for the long-term potentiation and  $A_{LTD} = -1$  for the long-term depression, respectively, were found. For a device area of 314 μm<sup>2</sup>, the resistance in the LRS,  $R_{on}$ , is 7 MΩ. The device-to-device variation, measured at 0.1 V as shown in Figure S3 (Supporting Information), is 5%.

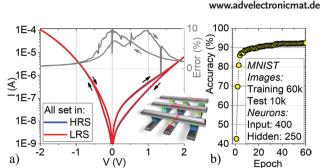

In **Figure 3**a, the *I*–*V* characteristics of a device in a  $3 \times 3$  crossbar are presented. Below the voltage of 70 mV the characteristics are linear, and quasi linear at 100 mV which is ideal for

**Figure 3.** a) *I*–*V* of a device in a  $3 \times 3$  array when the eight other elements are in HRS (blue line) or in LRS (red line). Gray line: relative error. b) Simulated accuracy of a 1R array of 400 input, 250 hidden and 10 output neurons (MNIST database).

vector-matrix multiplication when the input is mapped on this range. Above, the nonlinearity, quantified by the I(V)/I(V/2)ratio, gradually increases from 3 at 0.6 V to 18 at 2.0 V, as represented in Figure S4 (Supporting Information). In a neural network, the use of a selector or a selector diode is required to suppress the sneak paths. To assess their effect, the current-voltage characteristic of the same device in the center of the array was measured in the worst-case scenario (all the other devices in the crossbar array were set to the LRS) and in the best-case scenario (all the other devices in the HRS). The unaddressed word and bit lines were floating during the measurement. The data, shown in Figure 3a, differ by maximum 10% (gray curve). With the parameters listed earlier, the online learning accuracy of a selector-less array of 400 input, 250 hidden, and 10 output neurons trained on the MNIST database was simulated using the "MLP+NeuroSimV3.0" framework.[39] It is a circuit level macro model designed for benchmarking neuromorphic architectures. The weight update characteristics and device parameters listed above are mapped to a list of parameters used for the simulation, and are provided in the Supporting Information. As shown in Figure 3b, the accuracy reaches 92% after 36 training epochs.

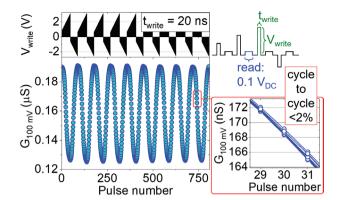

#### 3.2. Pulsed Weight Update

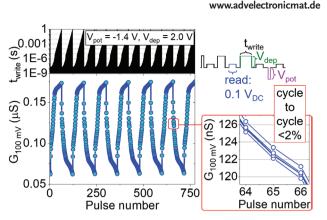

The conductance was then modulated using an arbitrary waveform generator and trapezoidal pulses of constant rising and dropping time of 20 ns. **Figure 4** shows the conductance at  $V_{\text{read}} = 100 \text{ mV}_{\text{DC}}$ , measured after each write pulse of increasing amplitude ( $V_{\text{write}}$ ) and of constant duration  $t_{\text{write}} = 20$  ns. In the inset, the same data are represented as a function of the pulse number within the cycle: the conductance varies by less than 2% from cycle to cycle. The energy dissipated during the writing is minimal for  $V_{\text{write}} = 0.2 \text{ V} (E^{0.2 \text{ V}} \approx 10^{-15} \text{ J})$  and maximal for  $V_{\text{write}} = -2 \text{ V} (E^{-2 \text{ V}} \approx 10^{-12} \text{ J})$ .

In Figure 5, the amplitude is kept constant (-1.4 V for potentiation, 2.0 V for depression) and the pulse width ( $t_{write}$ ) is increased. With this scheme, 20% of the dynamic range is traversed after the first pulse (20 ns, lower limit of the generator). The circuitry required for the on-chip implementation of this scheme is more accessible than the one required by the scheme with increasing amplitude. Moreover, it emulates spike trains and shows that the proposed devices have potential

**Figure 4.** Synaptic potentiation and depression with pulses of increasing amplitude. The pulse amplitude  $V_{\text{write}}$  and the pulse duration  $t_{\text{write}}$  are defined as in the measurement scheme (top right). The inset shows the cycle-to-cycle variation.

applications in neuromorphic systems implementing a spikerate-dependent-plasticity learning rule.<sup>[40,41]</sup> The cycle-to-cycle variation for both schemes is <2%. Cumulative switching (upon applying pulses of constant width and amplitude) was not observed. Because of the dual dependence on the pulse amplitude and duration for ferroelectric synaptic weights, implementing spike-timing-dependent-plasticity (STDP) rules with such devices requires tailored spike shapes as described by Boyn et al. in ferroelectric perovskites<sup>[42]</sup> and Max et al. in ferroelectric hafnia.<sup>[21]</sup>

Retention properties were measured for over ten days: the worst-case scenario corresponds to a 6% decay at 300 h  $(10^6 \text{ s})$  in the case where the polarization points toward the oxide interlayer (pink triangles in Figure S5, Supporting Information). This confirms that the devices based on a metal oxide/ ferroelectric bilayer showed limited back-switching compared to devices based on a dielectric interlayer: for comparison, optimized junctions based on a SiO<sub>2</sub>/Si:HfO<sub>2</sub> bilayer showed a 30% decay.<sup>[43]</sup> This observation is consistent with a better screening of the polarization charges by the metallic WO<sub>x</sub>, which implies a reduction of the depolarization field across the HZO ferroelectric layer that leads to improved retention characteristics. Finally, the devices showed strong robustness against fatigue, with no dielectric breakdown after more than 10<sup>10</sup> full switching cycles (±2 V at 100 kHz). Dynamic hysteresis measurements performed during the endurance experiment can be found in Figure S6 (Supporting Information).

#### 4. Investigation of the Resistive Switching Mechanism

Both tungsten oxides<sup>[44]</sup> and hafnium oxides<sup>[45]</sup> were used as memristors operating with the displacement of oxygen vacancies and ions. In this work, the current density (see Figure S7a, Supporting Information) is constant in the range (–2 V; 2 V) for circular devices with diameters in the 10–30  $\mu$ m range: Figure S7b (Supporting Information) shows the resistances measured at 0.1 V in the HRS and LRS in logarithmic scale, showing a constant On/Off ratio of 7. The homogeneous conduction across the device indicates there is no filament or

**Figure 5.** Long-term potentiation and depression for pulses with constant amplitudes  $V_{\text{pot}}$  and  $V_{\text{dep}}$  (as defined in the measurement scheme) and increasing duration  $t_{\text{width}}$ . The inset shows the cycle-to-cycle variation.

conduction at the edges. In addition, for a given polarity, resistive switching was only observed for pulses of increasing amplitude or time. Electroresistance loops (Figure S8, Supporting Information) revealed hysteretic behavior: the resistance increases (resp. decreases) while the amplitude increases from 0 to 2 V (resp. decreases from 0 to -2 V), then remains constant as the amplitude decreases from 2 to 0 V (resp. increases from -2 to 0 V). Moreover, a saturation is observed above 1.8 V and below -1.5 V. This discards current-driven resistive switching mechanisms (governing, e.g., filamentary resistive memories for which the weight update is performed by successive identical pulses).

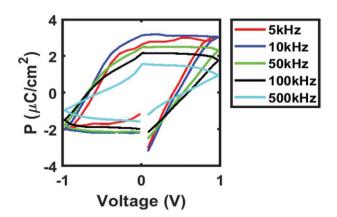

Positive-up-negative-down (PUND) experiments were performed to measure the ferroelectric properties of the devices. The waveform is schematized in Figure S9a, Supporting Information). The polarization for a 60  $\mu$ m capacitor measured at 50 kHz is represented in Figure S9b (Supporting Information). As for the current density, the polarization (per unit area) is independent on the device area (circular devices of diameter 40, 50, and 60  $\mu$ m), and confirms the ferroelectric properties of the devices ( $2P_r \approx 4.5 \ \mu$ C cm<sup>-2</sup>). This value is low compared to 10 nm films ( $\approx 20 \ \mu$ C cm<sup>-2</sup>) due to the reduced thickness. For a constant voltage range (-1 to 1 V), the polarization decreases with the frequency of the measurement, as represented in **Figure 6**: this effect reflects the dependence of the resistive

Figure 6. Polarization measured by the PUND method for a 60  $\mu m$  capacitor, for various frequencies.

switching on the pulse duration observed in Figure 5. The polarization switching occurs over a broad range of coercive fields (from  $\pm 0.2$  to above  $\pm 1$  V), matching the voltage range where the resistive switching is observed (see Figure 2. Such broad distribution is explained by the polycrystalline nature of the HZO film, determined by the X-ray analysis in Figure 1. Finally, we observed that the resistive switching saturates upon increasing field amplitude for both polarities (see the electroresistance loops in Figure S8, Supporting Information). These observations are consistent with the resistive switching originating from ferroelectric domains switching: it saturates when all the domains are aligned in the same direction. The multiple intermediate configurations are allowed by the polycrystalline nature of HZO: because of their different orientations and environment, some grains require a smaller electric fields to switch than others. By applying pulses of intermediate amplitude or duration, a fraction of the domains can be switched.

The role of the  $WO_x$  interlayer between the bottom TiN electrode and the HZO layer is to create an asymmetry in the energy profile of the device. By reversing the polarization from outward to toward this interlayer, the energy barrier seen by an electron is modified. A test structure was fabricated without the  $WO_x$  interlayer. The surface of the bottom TiN electrode is expected to be oxidized by the oxygen plasma applied during the HZO deposition. Despite this small asymmetry and consistently with the mechanism proposed above, no resistive switching was observed (see Figure S10, Supporting Information). In this paragraph,

the relative contribution of  $WO_x$  to the overall resistance is discussed. WO<sub>3</sub> is an insulator with a bandgap of 3.40 eV; oxygen vacancies create donor states that push the Fermi level close to the conduction band, conferring n-type semiconducting properties to  $WO_x$ .<sup>[46]</sup> For x < 2.9,  $WO_x$  shows metallic behavior.<sup>[47]</sup> The situation where  $WO_x$  is most likely to contribute to the resistance of the device is when the polarization points away from the WO<sub>x</sub> layer, after applying a negative bias on the top (TiN) electrode, causing an electrostatic depletion of electrons in the WO<sub>x</sub>. From the resistive switching experiments (e.g., in Figure 2), this corresponds to the LRS of the synaptic weight. This shows that the resistance change in the WO<sub>x</sub> layer is small compared to the resistance change in the HZO layer. In addition, a chip with identical HZO thickness but with a WO<sub>x</sub> layer thickness of only 1 nm (compared to 2 nm for the reference stack) was fabricated. Two devices of the same diameter (80 µm) but different WO<sub>x</sub> thicknesses shared the same LRS of  $R_{On} = 1.13 \text{ M}\Omega$ , showing that the resistance of the WO<sub>x</sub> layer was small compared to the resistance of the HZO layer. In the following paragraph, we assume that the electric field drop in the  $WO_x$  is small compared to that in the HZO layer.

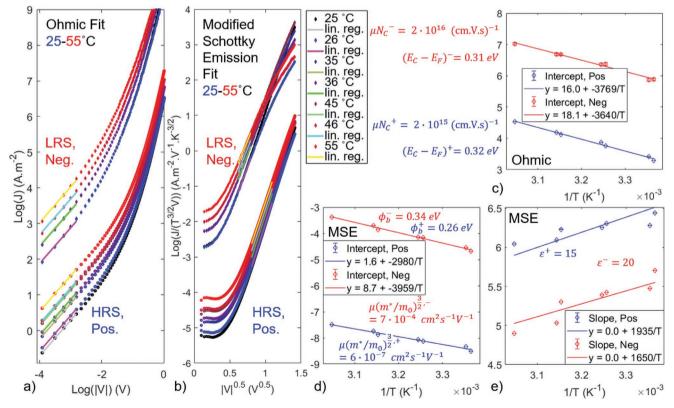

The conduction mechanisms across the devices were then analyzed with current–voltage (I-V) sweeps between 25 and 55 °C, back and forth with no degradation observed upon heating. Although the On/Off ratio remains constant, the resistance decreases with increasing temperature, as shown in **Figure 7** and Figure S8 (Supporting Information). For this

**Figure 7.** Current–voltage characteristics in the a) Ohmic and b) modified Schottky emission (MSE) representations. At each temperature, a linear regression is performed on the negative, increasing branch (LRS, nonswitching) and on the positive, decreasing branch (HRS, nonswitching). c) Arrhenius plots allow the calculation of the  $\mu N_C$  and  $E_C = E_F$  parameters from the intercepts of the linear regressions in the Ohmic regime, d) the  $\mu (m^*/m_0)^{3/2}$  parameter is calculated from the intercepts of the linear regression in the slopes of the latter.

reason, direct tunneling<sup>[48]</sup> and Fowler Nordheim tunneling<sup>[49]</sup> (respectively proposed in refs. [50] and [51]) were discarded as being the dominant transport mechanism. At low bias, below 70 mV and where the On/Off ratio is maximal, Ohmic conduction is observed, due to the drift of a small number of mobile electrons in the material's conduction band.<sup>[52]</sup> It is described by

$$J = \sigma E = \mu q N_{\rm C} \exp\left[\frac{-(E_{\rm C} - E_{\rm F})}{kT}\right] E \tag{1}$$

equivalent to

SCIENCE NEWS \_\_\_\_\_

$$Log(J) = Log(\mu q N_C / t) + \frac{-(E_C - E_F)}{k} \times \frac{1}{T} + Log(V)$$

(2)

where J is the current density,  $\sigma$  the electrical conductivity,  $\mu$ the electron mobility, q the electronic charge,  $N_{\rm C}$  the carrier concentration at equilibrium, t the sample thickness,  $E_{\rm C} - E_{\rm F}$ the energy difference between the conduction band and the Fermi level, k the Boltzmann constant, T the absolute temperature, and *E* the electric field across the ferroelectric layer. As discussed in the previous paragraph, the electric field was assumed to drop mainly across the ferroelectric layer resulting in E = V/twhere the thickness *t* is equal to 3.5 nm. Only the nonswitching branches of the IV sweeps were analyzed. The product  $\mu N_{\rm C}$ is assumed independent of the temperature.<sup>[52]</sup> At each temperature, a linear regression was performed in the  $Log(V) \mapsto$ Log() representation, shown in Figure 7a. Figure 7c shows the Arrhenius plot of the intercepts of the linear regression in the Ohmic regime: the presence of the conduction band at only 0.3 eV above the Fermi level, deducted using Equation (2), indicates the presence of donor states in the bandgap of HZO ( $\approx$ 5.4 eV<sup>[53]</sup>). Such states could originate from the presence of oxygen vacancies, but also from hydrogen trapped in the lattice during the atomic layer deposition.<sup>[54]</sup> From Figure 7c and Equation (2), we found that the resistive switching originates from an increase by one order of magnitude in the  $\mu N_{\rm C}$  product in the LRS compared to the HRS.

At large fields (below –600 mV and above 1.5 V) the *I*–V characteristics keep the same diode-like polarity regardless of the polarization direction, showing that the energy band diagram of the TiN/HZO/WO<sub>x</sub> junction is not structurally modified upon polarization reversal as, for example, in refs. [55–57].

At intermediate bias (from -400 to -640 mV and 640 to 1200 mV) we first considered electrode-limited mechanisms: the thermionic emission model<sup>[58]</sup> (proposed in ref. [59]) fitted reasonably well the data, however the Richardson constant obtained was of the order of 0.1 A m<sup>-2</sup> K<sup>-2</sup> in the HRS and 100 A m<sup>-2</sup> K<sup>-2</sup> in the LRS, which is orders of magnitude smaller than the universal Richardson constant<sup>[60]</sup> ( $\approx$ 10<sup>6</sup> A m<sup>-2</sup> K<sup>-2</sup>). Bulk-limited conduction mechanisms were also studied: similarly, it was possible to fit the experimental data with a Poole–Frenkel conduction model (proposed in ref. [61]), but the dielectric constant obtained with this model was unrealistically as high as 60. Thermionic-field emission,<sup>[62]</sup> hopping,<sup>[63]</sup> and space-charge-limited<sup>[63]</sup> fittings were not satisfying. Phonon-mediated trap-assisted-tunneling<sup>[65]</sup> models, in a single branch approach,

were not fitting the data on a sufficient range. Regardless of the conduction mechanisms explored, the corresponding barrier height seen by the electrons on the negative branch (TiN to HZO injection,  $\Phi_b^-$ ) is higher than in the other polarity ( $\Phi_b^+$ ), although the current flowing is larger. It supports the description of the transport by a "modified Schottky emission" (MSE) mechanism,<sup>[66]</sup> which confers both electrode and bulk limited characters to the conduction. The MSE model was previously observed in ZrO<sub>2</sub> thin films<sup>[67]</sup> and describes the experimental data well. It is governed by the equation

$$J = \alpha T^{\frac{3}{2}} E \mu \left(\frac{m^*}{m_0}\right)^{\frac{3}{2}} \exp\left[\frac{-q\left(\phi_{\rm B} - \sqrt{qE/4\pi\varepsilon_{\rm r}\varepsilon_0}\right)}{kT}\right]$$

(3)

equivalent to

$$\log\left(\frac{J}{T^{\frac{3}{2}}V}\right) = \frac{\alpha}{t} \mu\left(\frac{m^{*}}{m_{0}}\right)^{\frac{3}{2}} + \frac{-q\phi_{B}}{k} \times \frac{1}{T} + \frac{-q(\sqrt{q/t4\pi\varepsilon_{r}\varepsilon_{0}})}{k} \times \frac{1}{T} \times \sqrt{V}$$

$$(4)$$

where  $\alpha = 3 \times 10^{-4}$  A s cm<sup>-3</sup> K<sup>-3/2</sup> is a constant,  $m_0$  the free electron mass,  $m^*$  the effective electron mass in HZO,  $q\phi$ s the Schottky barrier height,  $\varepsilon_0$  the permittivity in vacuum, and  $\varepsilon_r$  the dynamic dielectric constant. Linear regressions in the representations of  $\log(J/(T^{3/2}V))$  as a function of  $|V|^{0.5}$  were performed (Figure 7b).

For this mechanism, the barrier heights measured from Figure 7d and Equation (4) are  $\phi_b^- = 0.34 \text{ eV}$  and  $\phi_b^+ = 0.26 \text{ eV}$ . Consistently with the increase of  $\mu N_C$  measured at low bias, the average product  $\mu (m^*/m_0)^{3/2}$  calculated from Figure 7d and Equation (4) increases by several orders of magnitude from the HRS to the LRS. On average, the dynamic dielectric constant  $\varepsilon$ , calculated from Figure 7e and Equation (4) also increases.

The models describe HZO as a semiconductor and show that the resistive switching originates from the modification of bulk transport properties upon polarization reversal. Such modification can be explained by the displacement of charged defects within the semiconducting ferroelectric layer upon polarization switching in the vicinities of the interfaces. The displacement of charged defects is driven by the screening of the polarization charges as observed recently in substoichiometric BaTiO<sub>3-x</sub> tunnel junctions,<sup>[68]</sup> but also in a polymer ferroelectric.<sup>[69]</sup> The simplified analytical models presented above do not capture eventual gradients within the HZO layer: further analysis using compact models simulations<sup>[70]</sup> may further improve the understanding of the resistive switching in the HZO/WO<sub>x</sub> bilayers.

#### 5. Conclusion

In this work, ferroelectricity was obtained in TiN/WO<sub>x</sub>/ HZO/ TiN structure with an HZO film as thin as 3.5 nm crystallized at 400 °C, a thermal budget compatible with back-endof-line. Thanks to the reduced thickness, the current density

was increased by three orders of magnitude compared to the state-of-the-art<sup>[33]</sup> and the devices operate in the Ohmic regime for read-out, which makes them ideal memristors for analog vector-matrix multiplication. The use of a metallic oxide electrode,  $WO_x$ , enables good retention properties: the conductance in the less stable state varies by only 6% after 10<sup>6</sup> s. In comparison, optimized MFIM devices show a 30% decay for the most stable state.<sup>[43]</sup> The On/Off of 7 and the small device-to-device variability (<5%) make them promising candidates for neural networks inference.

ADVANCED SCIENCE NEWS \_\_\_\_\_ www.advancedsciencenews.com

In addition, the synaptic functionality was demonstrated using pulses of increasing amplitude and constant duration, emulating spike-timing dependent plasticity. Using pulses as short as 20 ns, the writing energy was in the femtojoule range. Spike-rate dependent plasticity was also emulated, using pulses of constant amplitude (of only 2 V) and increasing duration. For both schemes the cycle-to-cycle variation was below 2%. The current–voltage nonlinearity in the range of 3–18, allowing limited effects of the sneak paths on addressing a device in passive cross-bar arrays, which was verified on a  $3 \times 3$  cross-bar. Using the weight update nonlinearity parameters of 0.5 and -1, the training accuracy of a neural network based on the proposed synapse on the MNIST data set was estimated to reach 92% after 36 epochs. In addition, the endurance of the devices exceeds  $10^{10}$  full switching cycles.

The conduction mechanisms across the device, as well as the mechanisms governing the resistive switching, were explored using temperature-dependent experiments: the results indicate the presence of allowed states for charge carriers within the bandgap of HZO, originating from defects such as oxygen vacancies. Upon polarization switching, the screening of the polarization by mobile charges (that could be associated with oxygen vacancies and/or ions) within the ferroelectric layer modifies the energy profile of the conduction band and the bulk transport properties.

#### 6. Experimental Section

Device Preparation: A 200 nm thick  $SiO_2$  oxide was grown on Si by thermal oxidation. The active stack was then deposited by PE-ALD: 20 nm of TiN was deposited at 300 °C with tetrakis(dimethylamino) titanium and N\_2 as precursors. 2 nm of WO\_x was deposited at 375  $^{\circ}\text{C}$ with (BuN)<sub>2</sub>W(NMe<sub>2</sub>)<sub>2</sub> and O<sub>2</sub>, then 3.5 nm of HZO was deposited at 300 °C alternating one cycle with tetrakis(ethylmethylamino) hafnium(IV) and O<sub>2</sub>, and two cycles with bis(methylcyclopentadienyl) (methyl) (methoxy) zirconium(IV) and O2. Ten additional nanometers of TiN were deposited. The crystallization was performed with the millisecond flash lamp annealing technique:[27] the sample was preheated to 400 °C, then a 20 ms long energy pulse of 90 J  $\rm cm^{-2}$ was applied. A 100 nm thick W metal electrode was then deposited by sputtering. The top electrode, defining the area of the junction, was defined by optical lithography and reactive ion etching (RIE) of the W and top TiN layers. Using this method, the HZO layer acted as an etch stop. The bottom electrode was then defined by optical lithography and inductive coupled plasma reactive ion etching (ICP) of the HZO, WOx, and TiN layers. A 100 nm thick SiO2 passivation layer was deposited at 300 °C by plasma-enhanced chemical vapor deposition (PECVD). Vias to the top and the bottom electrode were defined by optical lithography. The SiO<sub>2</sub> layer was etched by RIE, then the HZO and the WO<sub>x</sub> were etched by ICP, exposing the TiN layer to air. The etch was immediately followed by the sputtering of 100 nm of W. The first metal lines were then defined by optical lithography and etching by RIE. A 100 nm thick  $SiO_2$  passivation layer was deposited at 300 °C by PECVD. Vias to the bottom electrode contacts were defined by optical lithography. The  $SiO_2$  layer was etched by RIE. 100 nm of W was sputtered. The second metal lines were then defined by optical lithography and RIE.

*Structural Characterization*: Grazing-incidence X-ray diffraction (GIXRD) and X-ray reflectivity (XRR) measurements were performed on a Bruker D8 Discover diffractometer equipped with a rotating anode generator. The lamella for STEM analysis was prepared by focused ion beam (FIB) using an FEI Helios NanoLab 450S. STEM analysis was carried out on a double spherical aberration-corrected JEOL JEM-ARM200F microscope. BF-STEM images were acquired at 200 kV.

*Electrical Characterization*: Electrical measurements were performed on an Agilent B1500A semiconductor analyzer with a B1530A waveform generator/fast measurement unit (WGFMU). Write pulses were generated by a remote-sense and switch unit (RSU) module close to the probe and applied to the top electrode while the bottom electrode is grounded. The device resistance was measured at  $V = \pm 100$  mV with a high-resolution source-measurement unit (SMU) at the top electrode while the bottom electrode was grounded.

PUND experiments were performed to measure the ferroelectric properties of the devices. The waveform is schematized in Figure S9a (Supporting Information): during each of the P (positive, switching), U (positive, nonswitching), N (negative, switching), and D (negative, nonswitching) pulses of period *T*, the current *I* was measured during a time  $t_{\text{READ}}$  (that depends on the voltage range spanned and on the frequency) at a voltage *V*, then the voltage was increased by 0.1 V during a 20 ns long ramp. The polarization was calculated from the measured *I*–V curves.

#### **Supporting Information**

Supporting Information is available from the Wiley Online Library or from the author.

#### Acknowledgements

The authors thank the Cleanroom Operations Team of the Binnig and Rohrer Nanotechnology Center (BRNC) for their help and support. This work was funded by H2020: FREEMIND (No. 840903), ULPEC (No. 732642), BeFerroSynaptic (No. 871737), and UNICO (ANR-19-CHR3-0006).

#### **Conflict of Interest**

The authors declare no conflict of interest.

#### **Data Availability Statement**

The data that support the findings of this study are available in the supplementary material of this article.

#### **Keywords**

back-end-of-line, ferroelectrics, resistive switching, synaptic weight, transport  $% \left( {{{\left[ {{{C_{{\rm{s}}}} \right]}}}_{\rm{s}}}} \right)$

Received: January 21, 2022 Published online: March 8, 2022

#### **ADVANCED** SCIENCE NEWS

www.advancedsciencenews.com

- [1] Z. Sun, G. Pedretti, A. Bricalli, D. Ielmini, Sci. Adv. 2020, 6, eaay2378.

- [2] R. Yang, Nat. Electron. 2020, 3, 237.

- [3] R. Berdan, T. Marukame, K. Ota, M. Yamaguchi, M. Saitoh, S. Fujii, J. Deguchi, Y. Nishi, *Nat. Electron.* **2020**, *3*, 259.

- [4] Z. Yan, J. Chen, R. Hu, T. Huang, Y. Chen, S. Wen, Neural Networks 2020, 128, 142.

- [5] S. H. Jo, T. Chang, I. Ebong, B. B. Bhadviya, P. Mazumder, W. Lu, *Nano Lett.* 2010, *10*, 1297.

- [6] F. J. Kub, K. K. Moon, I. A. Mack, F. M. Long, IEEE J. Solid-State Circuits 1990, 25, 207.

- [7] M. Prezioso, F. Merrikh-Bayat, B. D. Hoskins, G. C. Adam, K. K. Likharev, D. B. Strukov, *Nature* 2015, *521*, 61.

- [8] S. Raoux, G. W. Burr, M. J. Breitwisch, C. T. Rettner, Y.-C. Chen, R. M. Shelby, M. Salinga, D. Krebs, S.-H. Chen, H.-L. Lung, C. H. Lam, *IBM J. Res. Dev.* **2008**, *52*, 465.

- [9] I. G. Baek, M. S. Lee, S. Sco, M. J. Lee, D. H. Seo, D.-S. Suh, J. C. Park, S. O. Park, H. S. Kim, I. K. Yoo, U.-I. Chung, J. T. Moon, in *IEDM Tech. Dig. IEEE Int. Electron Devices Meet. 2004*, IEEE, San Francisco, CA **2004**, pp. 587–590.

- [10] S. Kim, T. Todorov, M. Onen, T. Gokmen, D. Bishop, P. Solomon, K.-T. Lee, M. Copel, D. B. Farmer, J. A. Ott, T. Ando, H. Miyazoe, V. Narayanan, J. Rozen, in 2019 IEEE Int. Electron Devices Meet. IEDM, 2019, pp. 35.7.1–35.7.4.

- [11] X. Liu, Y. Wang, J. D. Burton, E. Y. Tsymbal, Phys. Rev. B 2013, 88, 165139.

- [12] Z. Xi, J. Ruan, C. Li, C. Zheng, Z. Wen, J. Dai, A. Li, D. Wu, Nat. Commun. 2017, 8, 15217.

- [13] X. Liu, J. D. Burton, E. Y. Tsymbal, Phys. Rev. Lett. 2016, 116, 197602.

- [14] A. Serb, J. Bill, A. Khiat, R. Berdan, R. Legenstein, T. Prodromakis, *Nat. Commun.* 2016, 7, 12611.

- [15] M. Hansen, F. Zahari, H. Kohlstedt, M. Ziegler, Sci. Rep. 2018, 8, 8914.

- [16] S. R. Nandakumar, I. Boybat, M. L.e Gallo, E. Eleftheriou, A. Sebastian, B. Rajendran, *Sci. Rep.* **2020**, *10*, 8080.

- [17] A. Renner, F. Sheldon, A. Zlotnik, L. Tao, A. Sornborger, in *Proc. Neuro-Inspired Computational Elements Workshop*, ACM, Heidelberg, Germany 2020, pp. 1–3.

- [18] T. S. Böscke, J. Müller, D. Bräuhaus, U. Schröder, U. Böttger, Appl. Phys. Lett. 2011, 99, 102903.

- [19] S. Dunkel, M. Trentzsch, R. Richter, P. Moll, C. Fuchs, O. Gehring, M. Majer, S. Wittek, B. Muller, T. Melde, H. Mulaosmanovic, S. Slesazeck, S. Muller, J. Ocker, M. Noack, D.-A. Lohr, P. Polakowski, J. Muller, T. Mikolajick, J. Hontschel, B. Rice, J. Pellerin, S. Beyer, in 2017 IEEE Int. Electron Devices Meet. IEDM, IEEE, San Francisco, CA 2017, pp. 19.7.1–19.7.4.

- [20] M. Halter, L. Bégon-Lours, V. Bragaglia, M. Sousa, B. J. Offrein, S. Abel, M. Luisier, J. Fompeyrine, ACS Appl. Mater. Interfaces 2020, 12, 17725.

- [21] B. Max, M. Hoffmann, H. Mulaosmanovic, S. Slesazeck, T. Mikolajick, ACS Appl. Electron. Mater. 2020, 2, 4023.

- [22] R. Berdan, T. Marukame, S. Kabuyanagi, K. Ota, M. Saitoh, S. Fujii, J. Deguchi, Y. Nishi, in 2019 Symp. VLSI Technology, IEEE, Kyoto, Japan 2019, pp. T22–T23.

- [23] B. Max, M. Hoffmann, S. Slesazeck, T. Mikolajick, *Electron. Lett.* 2020, 56, 1108.

- [24] M. Pesic, A. Padovani, S. Slcsazeck, T. Mikolajick, L. Larcher, in 2018 IEEE Int. Electron Devices Meeting IEDM, IEEE, San Francisco, CA 2018, pp. 25.1.1–25.1.4.

- [25] M. Lederer, D. Lehninger, S. Abdulazhanov, A. Reck, R. Olivo, T. Kampfe, K. Seidel, in 2021 IEEE Int. Symp. Applications of Ferroelectrics (ISAF), IEEE, Sydney, Australia 2021, pp. 1–4.

- [26] L. Grenouillet, T. Francois, J. Coignus, S. Kerdiles, N. Vaxelaire, C. Carabasse, F. Mehmood, S. Chevalliez, C. Pellissier, F. Triozon, F. Mazen, G. Rodriguez, T. Magis, V. Havel, S. Slesazeck, F. Gaillard,

ADVANCED ELECTRONIC MATERIALS

U. Schroeder, T. Mikolajick, E. Nowak, in 2020 IEEE Symp. VLSI Technology, IEEE, Honolulu, HI 2020, pp. 1–2.

- [27] É. O'Connor, M. Halter, F. Eltes, M. Sousa, A. Kellock, S. Abel, J. Fompeyrine, APL Mater. 2018, 6, 121103.

- [28] L. Bégon-Lours, M. Halter, Y. Popoff, B. J. Offrein, Phys. Status Solidi RRL 2020, 15, 2000524.

- [29] L. Begon-Lours, M. Halter, D. D. Pineda, Y. Popoff, V. Bragaglia, A. L. Porta, D. Jubin, J. Fompeyrine, B. J. Offrein, in 2021 5th IEEE Electron Devices Technology & Manufacturing Conf. (EDTM), IEEE, Chengdu, China 2021, pp. 1–3.

- [30] K. Tahara, K. Toprasertpong, Y. Hikosaka, K. Nakamura, H. Saito, M. Takenaka, S. Takagi, 2021 Symp. VLSI Technology 2021, p. 2.

- [31] Y.-K. Liang, J.-S. Wu, C.-Y. Teng, H.-L. Ko, Q.-H. Luc, C.-J. Su, E.-Y. Chang, C.-H. Lin, *IEEE Electron Device Lett.* **2021**, 42, 1299.

- [32] T. Ali, A. Sünbül, K. Mertens, R. Revello, M. Lederer, D. Lehninger, F. Müller, K. Kühnel, M. Rudolph, S. Oehler, R. Hoffmann, K. Zimmermann, K. Biedermann, P. Schramm, M. Czernohorsky, K. Seidel, T. Kämpfe, L. M. Eng, in 2021 Silicon Nanoelectronics Workshop SNW, 2021, pp. 1–2.

- [33] L. Bégon-Lours, M. Halter, Y. Popoff, Z. Yu, D. F. Falcone, D. Davila, V. Bragaglia, A. La Porta, D. Jubin, J. Fompeyrine, B. J. Offrein, in *IEEE Journal of the Electron Devices Society*, Vol. 9, **2021**, pp. 1275–1281, https://doi.org/10.1109/JEDS.2021.3108523.

- [34] M. H. Park, H. J. Kim, Y. J. Kim, T. Moon, C. S. Hwang, Appl. Phys. Lett. 2014, 104, 072901.

- [35] R. Materlik, C. Künneth, A. Kersch, J. Appl. Phys. 2015, 117, 134109.

- [36] J. Müller, T. S. Böscke, U. Schröder, S. Mueller, D. Bräuhaus, U. Böttger, L. Frey, T. Mikolajick, Nano Lett. 2012, 12, 4318.

- [37] B. E. Warren, X-Ray Diffraction, Courier Corporation, Chelmsford, MA 1990.

- [38] P. Chen, X. Peng, S. Yu, IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst. 2018, 37, 3067.

- [39] Y. Luo, X. Peng, S. Yu, in Proc. Int. Conf. Neuromorphic Systems, ACM, Knoxville TN 2019, pp. 1–7.

- [40] S. Li, F. Zeng, C. Chen, H. Liu, G. Tang, S. Gao, C. Song, Y. Lin, F. Pan, D. Guo, J. Mater. Chem. C 2013, 1, 5292.

- [41] N. Mohta, A. Rao, N. Remesh, R. Muralidharan, D. N. Nath, RSC Adv. 2021, 11, 36901.

- [42] S. Boyn, J. Grollier, G. Lecerf, B. Xu, N. Locatelli, S. Fusil, S. Girod, C. Carrétéro, K. Garcia, S. Xavier, J. Tomas, L. Bellaiche, M. Bibes, A. Barthélémy, S. Saïghi, V. Garcia, *Nat. Commun.* **2017**, *8*, 14736.

- [43] S. Fujii, M. Yamaguchi, S. Kabuyanagi, K. Ota, M. Saitoh, in 2020 IEEE Symp. VLSI Technology, IEEE, Honolulu, HI 2020, pp. 1–2.

- [44] T. Chang, S.-H. Jo, K.-H. Kim, P. Sheridan, S. Gaba, W. Lu, Appl. Phys. A 2011, 102, 857.

- [45] Y. Wang, Q. Liu, S. Long, W. Wang, Q. Wang, M. Zhang, S. Zhang, Y. Li, Q. Zuo, J. Yang, M. Liu, *Nanotechnology* **2010**, *21*, 045202.

- [46] M. T. Greiner, Z.-H. Lu, NPG Asia Mater. 2013, 5, e55.

- [47] E. Salje, B. Güttler, Philos. Mag. B 1984, 50, 607.

- [48] D. Pantel, M. Alexe, Phys. Rev. B 2010, 82, 134105.

- [49] D. K. Schroder, Semiconductor Material and Device Characterization, Wiley, New York 2015.

- [50] Y. Wei, S. Matzen, T. Maroutian, G. Agnus, M. Salverda, P. Nukala, Q. Chen, J. Ye, P. Lecoeur, B. Noheda, *Phys. Rev. Appl.* **2019**, *12*, 031001.

- [51] K. Ota, J. Deguchi, S. Fujii, M. Saitoh, M. Yamaguchi, R. Berdan, T. Marukame, Y. Nishi, K. Matsuo, K. Takahashi, Y. Kamiya, S. Miyano, in 2019 IEEE Int. Electron Devices Meeting IEDM, IEEE, San Francisco, CA 2019, pp. 6.2.1–6.2.4.

- [52] S. M. Sze, K. K. Ng, Physics of Semiconductor Devices, Wiley-Interscience, Hoboken, NJ 2007.

- [53] H. C. Shin, D. Tahir, S. Seo, Y. R. Denny, S. K. Oh, H. J. Kang, S. Heo, J. G. Chung, J. C. Lee, S. Tougaard, Surf. Interface Anal. 2012, 6.

#### **ADVANCED** SCIENCE NEWS

www.advancedsciencenews.com

- [54] H. Kim, S. Yun, T. H. Kim, H. Kim, C. Bae, S. Jeon, S. Hong, *Phys. Status Solidi RRL* 2021, 2100020.

- [55] Q. Luo, Y. Cheng, J. Yang, R. Cao, H. Ma, Y. Yang, R. Huang, W. Wei, Y. Zheng, T. Gong, J. Yu, X. Xu, P. Yuan, X. Li, L. Tai, H. Yu, D. Shang, Q. Liu, B. Yu, Q. Ren, H. Lv, M. Liu, *Nat. Commun.* **2020**, *11*, 1391.

- [56] T. Choi, S. Lee, Y. J. Choi, V. Kiryukhin, S.-W. Cheong, *Science* **2009**, 324, 63.

- [57] M. C. Sulzbach, S. Estandía, X. Long, J. Lyu, N. Dix, J. Gàzquez, M. F. Chisholm, F. Sánchez, I. Fina, J. Fontcuberta, Adv. Electron. Mater. 2020, 6, 1900852.

- [58] W. Schottky, Phys. Z. 1914, 15, 872.

- [59] H. Y. Yoong, H. Wu, J. Zhao, H. Wang, R. Guo, J. Xiao, B. Zhang, P. Yang, S. J. Pennycook, N. Deng, X. Yan, J. Chen, Adv. Funct. Mater. 2018, 28, 1806037.

- [60] C. R. Crowell, Solid-State Electron. 1965, 8, 395.

- [61] D. S. Jeong, H. B. Park, C. S. Hwang, Appl. Phys. Lett. 2005, 86, 072903.

- [62] C. Hamann, H. Burghardt, T. Frauenheim, *Electrical Conduction Mechanisms in Solids*, VCH Pub, 1988.

- [63] N. F. Mott, E. A. Davis, *Electronic Processes in Non-Crystalline Materials*, Oxford University Press, Oxford 2012.

- [64] D. R. Islamov, V. A. Gritsenko, T. V. Perevalov, V. A. Pustovarov, O. M. Orlov, A. G. Chernikova, A. M. Markeev, S. Slesazeck, U. Schroeder, T. Mikolajick, G. Y. Krasnikov, *Acta Mater.* 2019, 166, 47.

- [65] S. Fleischer, P. T. Lai, Y. C. Cheng, J. Appl. Phys. 1992, 72, 5711.

- [66] J. G. Simmons, Phys. Rev. Lett. 1965, 15, 967.

- [67] F.-C. Chiu, Z.-H. Lin, C.-W. Chang, C.-C. Wang, K.-F. Chuang, C.-Y. Huang, J. Y. Lee, H.-L. Hwang, J. Appl. Phys. 2005, 97, 034506.

- [68] J. Li, N. Li, C. Ge, H. Huang, Y. Sun, P. Gao, M. He, C. Wang, G. Yang, K. Jin, *iScience* **2019**, *16*, 368.

- [69] B. B. Tian, Y. Liu, L. F. Chen, J. L. Wang, Sci. Rep. 2015, 5, 9.

- [70] L. Larcher, A. Padovani, P. Pavan, Technical Proc. of the 2012 NSTI Nanotechnology Conf. and Expo, NSTI-Nanotech 20122012 2012, pp. 809–814.