Diss. ETH No. 16578

# A Neuromorphic VLSI System for Modeling Spike–Based Cooperative Competitive Neural Networks

## A dissertation submitted to the SWISS FEDERAL INSTITUTE OF TECHNOLOGY (ETH ZURICH)

for the degree of Doctor of Natural Sciences

presented by ELISABETTA CHICCA Dipl.-Phys. Università di Roma "La Sapienza" born April 1, 1972 citizen of Rome, Italy

accepted on the recommendation of Prof. Dr. Rodney J. Douglas, examiner Dr. Giacomo Indiveri, co-examiner Dr. Daniel Kiper, co-examiner

2006

# Abstract

*Neuromorphic engineering* is an emerging research field which explores methodologies for implementing biologically inspired systems in hardware. It has a key role in neuroscience as a means for testing hypotheses concerning the computation carried out by the brain, while at the same time it promotes the development of artificial systems capable of achieving performance figures comparable to those of biological neural systems. I am interested in applying neuromorphic engineering methods as a tool for understanding cortical computation and its relation to recurrent intra-cortical connectivity.

This thesis describes the development and testing of a neuromorphic VLSI implementation of a spiking recurrent cortical network model and the hardware/software infrastructure required to operate it. The local connectivity of my neural network is an abstract representation of the cooperative–competitive connectivity observed in cortex, which is believed to play a major role in shaping cortical responses and selecting the relevant signal among distractors and noise. The hardware/software infrastructure allows us to build multi–chip systems, to configure the inter–chip and intra–chip connectivity, to provide external stimuli to the multi–chip system and to monitor the activity of all chips, providing a highly flexible tool for testing complex systems.

I performed software simulations and real-time experiments with the working chip to demonstrate that the spiking network exhibits the complex behaviors predicted by well known theoretical studies on more abstract models (e.g. dynamic field theory, rate model) of similar architectures. I carried out experiments with both artificially generated, well controlled stimuli and "real" sensory data generated by a silicon retina chip. In the latter case, I implemented (in collaboration with my collegue Patrick Lichtsteiner) and tested a two chip vision based system for exploring computational models of feature selectivity in a real-world scenario, and so demonstrated the feasibility of real-time inter-chip communication through our hardware/software infrastructure. Such a feasibility proof is a necessary step for evolving the neuromorphic systems developed so far into complex and scalable systems endowed with sophisticated computational capabilities.

The VLSI spiking recurrent network and the hardware/software infrastructure described in this thesis provide a highly flexible platform to test the computational properties of cooperative competitive neural networks in real-time, and allows us to test the role of spike timing with real-world stimuli.

The insights gained through with this work, the technology developed and the methodologies derived provide an important stepping stone toward the understanding and practical application of recurrent, cooperative–competitive neural networks. **Keywords:** neuromorphic, VLSI, neural networks, Integrate–and–Fire (I&F) neuron, Address Event Representation, cooperative competitive networks, orientation selectivity.

# Prefazione

L'ingegneria neuromorfa è un campo di ricerca emergente che esplora le metodologie per progettare sistemi fisici prendendo ispirazione dalla biologia. Essa ha un ruolo fondamentale come mezzo per valutare ipotesi riguardo la computazione eseguita dal cervello e, allo stesso tempo, promuove lo sviluppo di sistemi artificiali capaci di raggiungere prestazioni confrontabili a quelle dei sistemi neurali biologici. Il mio interesse principale riguarda l'utilizzo delle metodologie dell'ingegneria neuromorfa come strumento per comprendere i processi computazionali che avvengono nella corteccia cerebrale e la loro relazione con la connettività ricorrente corticale.

Questa tesi descrive lo sviluppo e l'analisi di una trasposizione in VLSI neuromorfo di un modello di rete ricorrente corticale e l'infrastruttura *hardware/software* per farla funzionare. La connettività locale della rete neurale rappresenta in modo astratto la connettività di natura cooperativa e competitiva presente nella corteccia cerebrale, la quale si pensa abbia un ruolo fondamentale nel plasmare l'attività corticale e nell'amplificare i segnali che codificano l'informazione, sopprimendo quelli che derivano da distrattori e rumore. L'infrastruttura *hardware/software* sviluppata ci permette di costruire sistemi multi–chip, configurare la connettività inter–chip ed intra–chip, fornire stimoli esterni al sistema multi– chip e monitorare l'attività di tutti i chip, fornendo così uno strumento flessibile per testare sistemi complessi.

In questo lavoro ho eseguito simulazioni *software* ed esperimenti con il chip in tempo reale per dimostrare che la rete neurale artificiale esibisce gli stessi comportamenti complessi descritti da studi analitici su modelli di architetture simili. In questi esperimenti la rete ricorrente è stata stimolata sia con stimoli generati artificialmente sia con stimoli percettivi "reali" generati da una retina artificiale. In quest'ultimo caso, ho realizzato e caratterizzato (in collaborazione con Patrick Lichtsteiner) un sistema visivo composto da due chip per studiare possibili modelli computazionali per la selettività a caratteristiche dello stimolo visivo (come ad esemprio, orientamento) in uno scenario realistico. Questo sistema dimostra la funzionalità della comunicazione tra chip in tempo reale attraverso l'infrastruttura sviluppata. Questa prova di funzionalità rappresenta un passo fondamentale per lo sviluppo di sistemi neuromorfi in architetture complesse e scalabili dotate di proprietà computazionali elaborate.

La rete VLSI ricorrente realizzata con neuroni *integrate–and–fire* e l'infrastruttura *hardware/software* descritte in questa tesi costituiscono uno strumento flessibile per indagare le proprietà computazionali delle reti neurali, cooperative e competitive, in tempo reale e permette di verificare ipotesi riguardo al ruolo delle temporizzazioni tra gli impulsi neuronali attraverso l'uso di stimoli realistici.

I risultati ottenuti con questo lavoro, la tecnologia sviluppata e la metodologia proposta rappresentano un ulteriore passo verso la comprensione e l'applicazione pratica delle reti neurali competitive e cooperative.

**Parole chiave:** neuromorfo, VLSI, reti neurali, neurone *Integrate–and–Fire* (I&F), *Address Event Representation* (AER), reti cooperative e competitive, selettività all'orientamento.

To Daniele and Giulia

# Contents

|   | Abs  | tract                                                             | i   |

|---|------|-------------------------------------------------------------------|-----|

|   | Pref | azione                                                            | iii |

| 1 | Intr | oduction                                                          | 1   |

|   | 1.1  | Motivation                                                        | 1   |

|   | 1.2  | Outline of this Thesis                                            | 3   |

| 2 | The  | Address-Event Representation and Event-Based Neuromorphic Systems | 5   |

|   | 2.1  | The Address–Event Representation                                  | 5   |

|   | 2.2  | Analysis of Time Multiplexing Techniques                          | 6   |

|   |      | 2.2.1 Sequential Scanning                                         | 8   |

|   |      | 2.2.2 ALOHA Access Protocol                                       | 9   |

|   |      | 2.2.3 Priority Encoder                                            | 10  |

|   |      | 2.2.4 Arbitrated Access                                           | 10  |

|   |      | 2.2.5 Summary                                                     | 11  |

|   | 2.3  | Arbitrated AER for Multi-chip Systems                             | 12  |

|   | 2.4  | AER Hardware Infrastructures                                      | 14  |

|   | 2.5  | The PCI–AER Hardware Infrastructure                               | 15  |

|   |      | 2.5.1 The PCI–AER Board                                           | 15  |

|   |      | 2.5.2 Supporting Software                                         | 20  |

| 3 | Ana  | log Circuits for Implementing Spike Based Processing Models       | 23  |

|   | 3.1  | Subthreshold MOSFET Characteristic                                | 23  |

|   | 3.2  | Differential Pair and Transconductance Amplifier                  | 25  |

|   | 3.3  | Capacitive Voltage Divider                                        | 28  |

|   | 3.4  | Current Mirror                                                    | 29  |

|   | 3.5  | Current Mirror Integrator                                         | 30  |

|   |      | 3.5.1 Response to Spike Trains: Approximate Solution              | 31  |

|   |      | 3.5.2 Response to Spike Trains: General Analytical Solution       | 33  |

|   | 3.6  | Excitatory and Inhibitory Synapses                                | 34  |

|   | 3.7  | The Adaptive Synapse                                              | 34  |

|   |      | 3.7.1 Experimental Results                                        | 38  |

|   | 3.8  | The Integrate-and-Fire Silicon Neuron                             | 41  |

|   | 3.9         | Discussion                                                                                                 | 44  |

|---|-------------|------------------------------------------------------------------------------------------------------------|-----|

| 4 | Coo         | perative–Competitive Neural Networks                                                                       | 45  |

|   | 4.1         | Analytical Methods Applied to Cooperative–Competitive Networks                                             | 47  |

|   | 4.2         | The Neural Code                                                                                            | 50  |

|   | 4.3         | Neural Coding in Ring of Neurons Competitive Networks                                                      | 51  |

|   | 4.4         | Software Simulation of the Ring of Neurons Competitive Network                                             | 53  |

|   |             | 4.4.1 Sharpening and Suppression of Less Effective Stimuli                                                 | 53  |

|   |             | 4.4.2 Hysteretic Behavior                                                                                  | 55  |

|   | 4.5         | Discussion                                                                                                 | 56  |

| 5 | VLS         | I Competitive Networks of Spiking Neurons                                                                  | 59  |

|   | 5.1         | The IFRON Chip: a VLSI Implementation of a Spiking Cooperative Com-                                        |     |

|   |             | petitive Network                                                                                           | 61  |

|   |             | 5.1.1 Chip Architecture                                                                                    | 62  |

|   |             | 5.1.2 Circuits                                                                                             | 66  |

|   | 5.2         | IFRON Chip Experiments                                                                                     | 72  |

|   |             | 5.2.1 Basic Building Blocks Behavior                                                                       |     |

|   |             | 5.2.2 Basic Network Behavior                                                                               | 74  |

|   |             | 5.2.3 Sharpening and Suppression of Least Effective Stimuli                                                |     |

|   | 5.3         | Discussion                                                                                                 | 81  |

| 6 | A M         | ulti-Chip Neuromorphic System for Feature Selectivity                                                      | 83  |

|   | 6.1         | Orientation Selectivity Using a Silicon Retina and the IFRON chip                                          | 87  |

|   |             | 6.1.1 The TMPDIFF Chip                                                                                     | 87  |

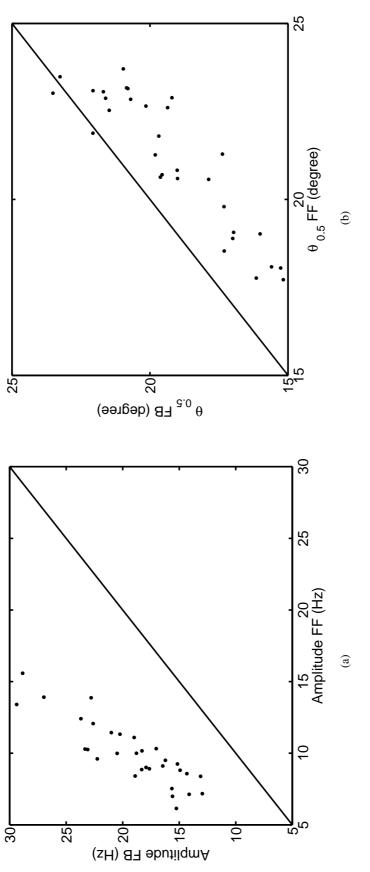

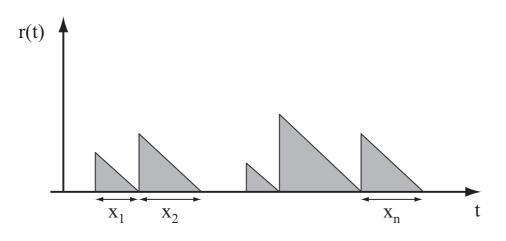

|   | 6.2         | Orientation Selectivity Experiments                                                                        | 88  |

|   | 6.3         | Discussion                                                                                                 | 95  |

| 7 | Con         | clusions                                                                                                   | 97  |

|   | 7.1         | Ideas for Further Work and Outlook                                                                         | 99  |

| A | The         | M/G/1 Queue and the Pollaczek-Khinchin formula                                                             | 101 |

| В | рст         | -AER Library Interface Specification                                                                       | 103 |

| D | в.1         |                                                                                                            |     |

|   | B.2         | Description of the PCI–AER Library Functions                                                               |     |

|   | <b>D</b> .2 | B.2.1 Common Functions Applicable to More Than One Sub-device                                              |     |

|   |             | B.2.1       Common Punctions Applicable to Wore Than One Sub-device         B.2.2       Monitor Sub-device |     |

|   |             | B.2.3 Sequencer Sub-device                                                                                 |     |

|   |             | B.2.4         Mapper Sub-device                                                                            |     |

|   |             |                                                                                                            |     |

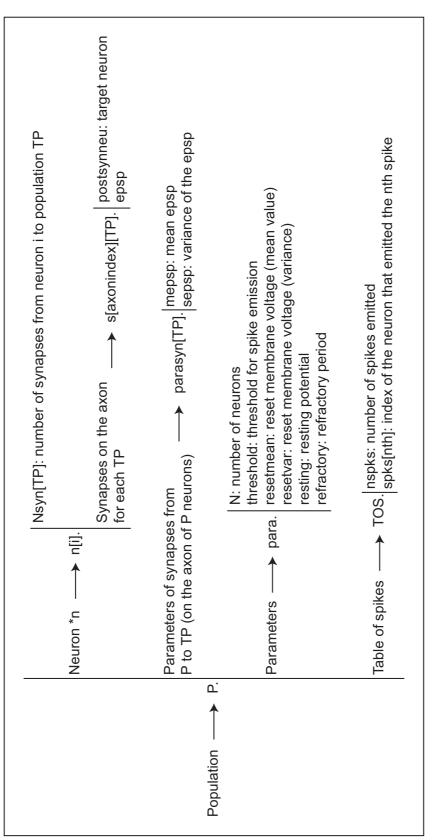

| С | IFR         | ON Software Simulation Tool                                                                                | 115 |

| D | Arbi        | iter UPI Code                                                                                              | 117 |

| Abbreviations and Symbols | 135 |

|---------------------------|-----|

| Bibliography              | 137 |

| Curriculum Vitae          | 147 |

# **List of Figures**

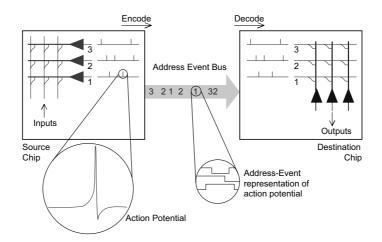

| 2.1  | Schematic diagram of an AER chip-to-chip communication example                   |    |

|------|----------------------------------------------------------------------------------|----|

|      | (adapted from [37])                                                              | 7  |

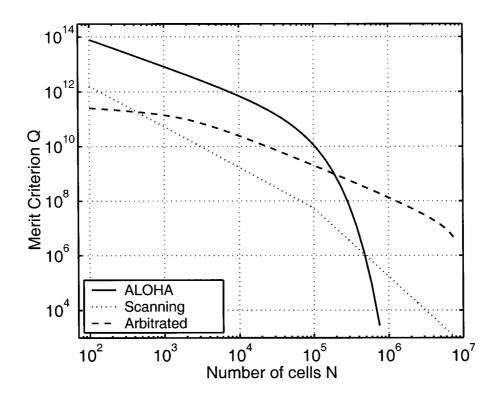

| 2.2  | Merit criterion versus number of cells for three different access protocols      |    |

|      | (adapted from [33])                                                              | 12 |

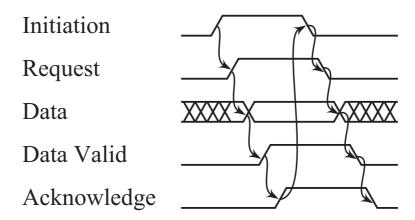

| 2.3  | Point-to-Point handshake protocol.                                               | 13 |

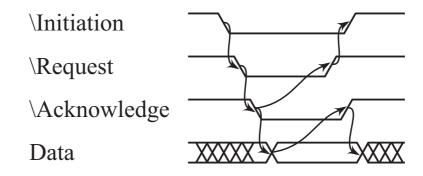

| 2.4  | SCX handshake protocol                                                           | 13 |

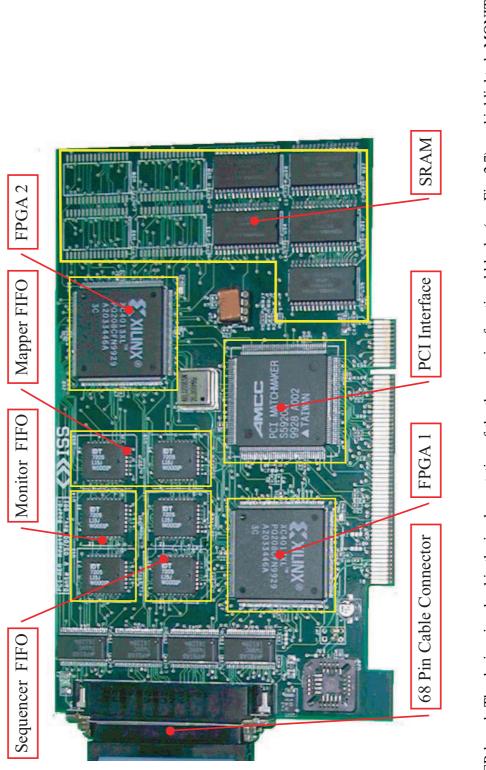

| 2.5  | PCI–AER board.                                                                   | 16 |

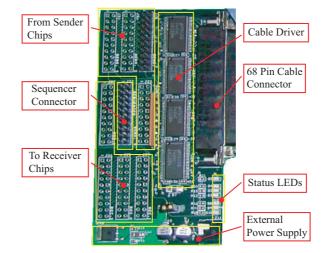

| 2.6  | PCI–AER header board.                                                            | 17 |

| 2.7  | Block diagram of the PCI-AER interface board                                     | 18 |

| 3.1  | Schematic drawing of the physical structure of an $n$ -type MOS transistor.      | 24 |

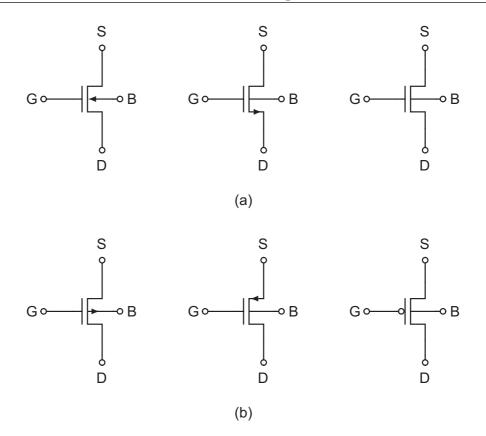

| 3.2  | Symbols for an <i>n</i> -type MOS transistor and a <i>p</i> -type MOS transistor | 25 |

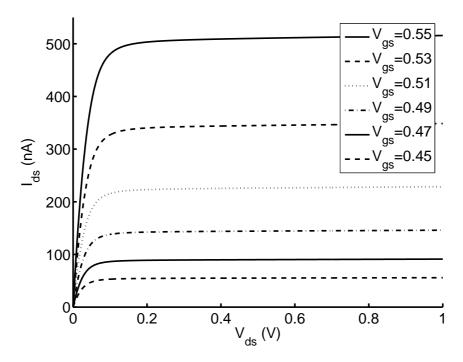

| 3.3  | The current $I_{ds}$ as a function of $V_{ds}$ .                                 | 26 |

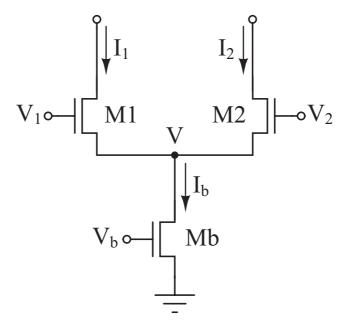

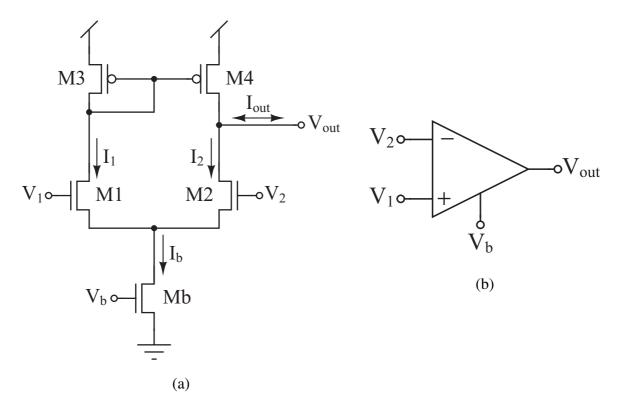

| 3.4  | Schematic diagram of the differential pair                                       | 27 |

| 3.5  | Transconductance amplifier.                                                      | 27 |

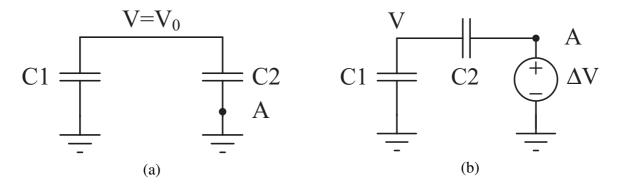

| 3.6  | Capacitive voltage divider.                                                      | 28 |

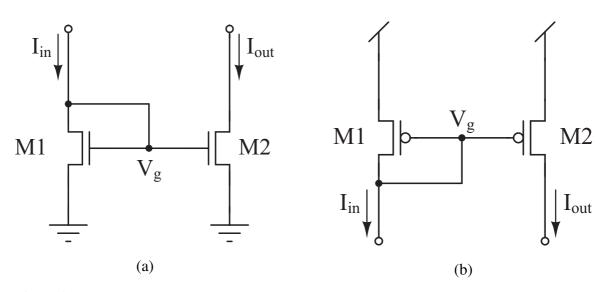

| 3.7  | Current mirror.                                                                  | 29 |

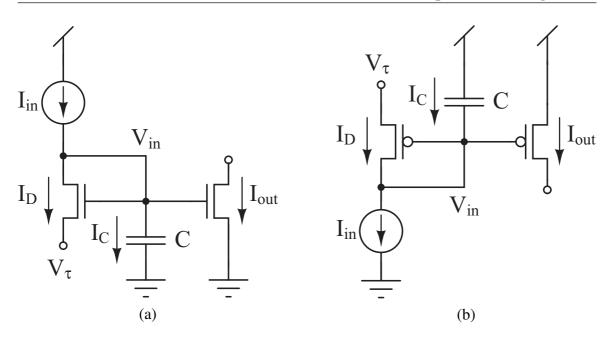

| 3.8  | Current Mirror Integrator (CMI)                                                  | 30 |

| 3.9  | Schematic diagram of the excitatory synapse                                      | 35 |

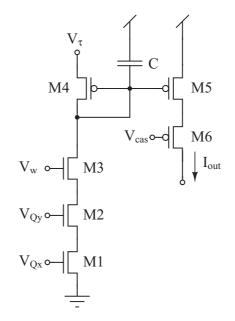

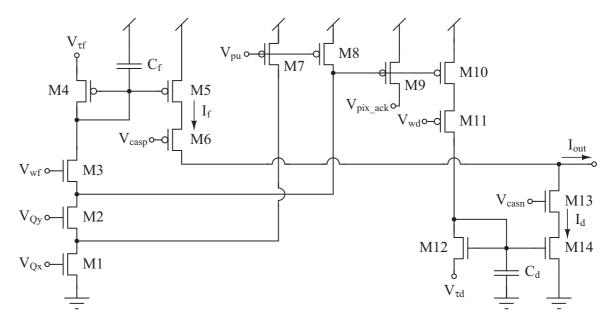

| 3.10 | Schematic diagram of the adaptive synapse                                        | 35 |

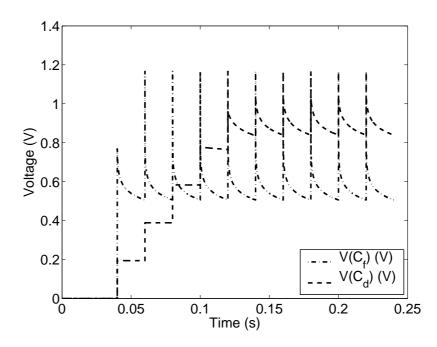

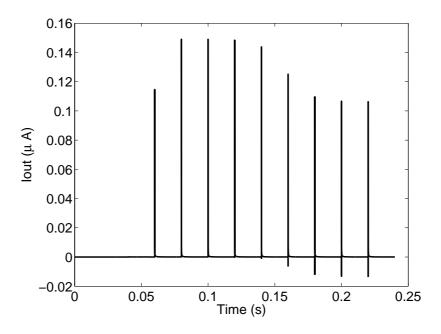

| 3.11 | Voltages across the facilitating capacitor $C_f$ and the depressing capacitor    |    |

|      | $C_d$ in response to a 50 Hz spike train (analytical derivation)                 | 37 |

| 3.12 | Output current of the adaptive synapse in response to a 50 Hz spike train        |    |

|      | (plot of the analytical expression of the current)                               | 37 |

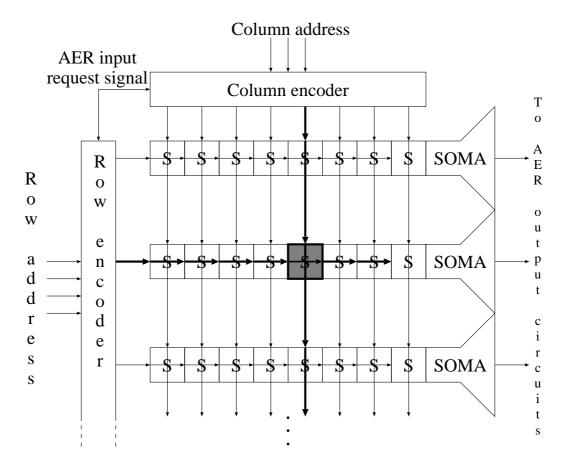

| 3.13 | Schematic diagram of the chip architecture                                       | 39 |

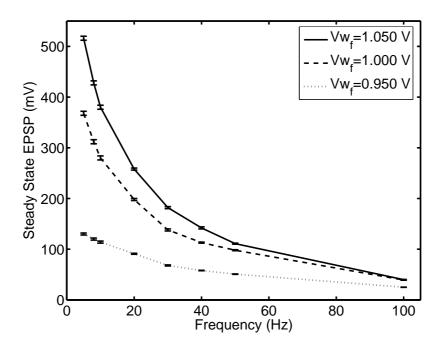

| 3.14 | Steady state amplitude of the EPSP as a function of presynaptic frequency        |    |

|      | for three different values of $Vw_f$                                             | 40 |

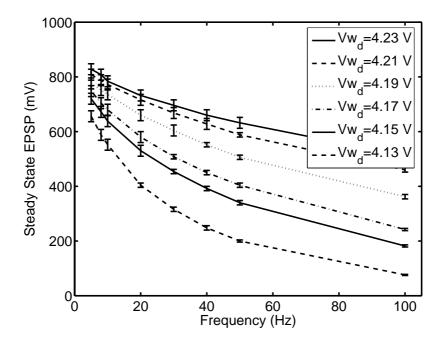

| 3.15 | Steady state amplitude of the EPSP as a function of presynaptic frequency        |    |

|      | for six different values of $Vw_d$                                               | 40 |

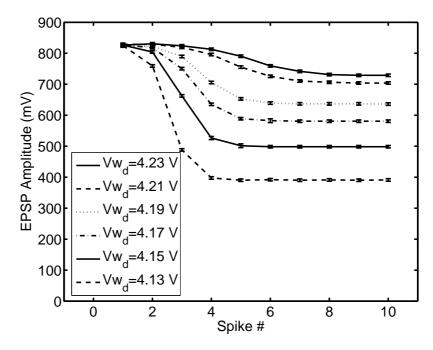

| 3.16 | Normalized EPSP amplitude in response to the first ten pulses of a 20Hz          |    |

|      | train of spikes for three different values of $Vw_d$                             | 41 |

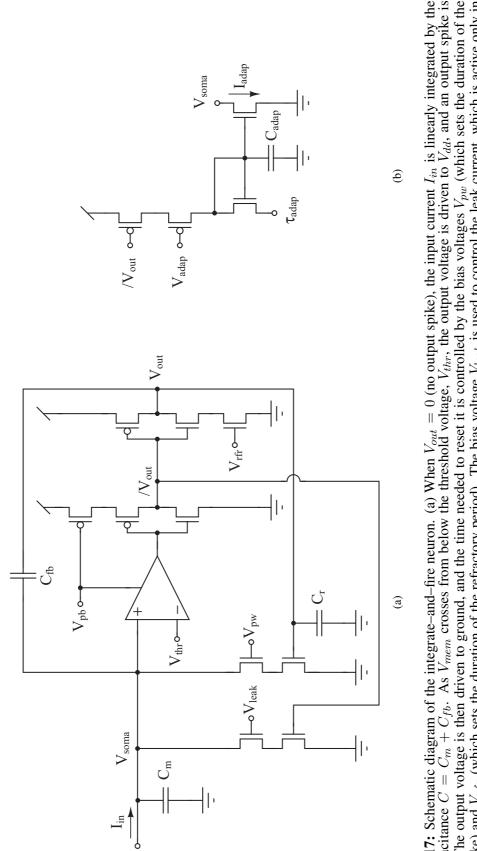

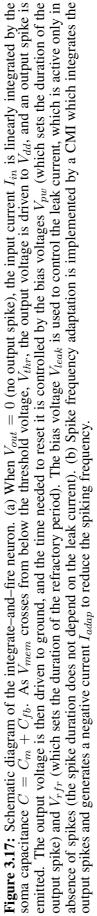

| 3.17 | Schematic diagram of the integrate–and–fire neuron.                              | 42 |

| 4.1  | Schematic representation of the ring–of–neurons architecture                     | 52 |

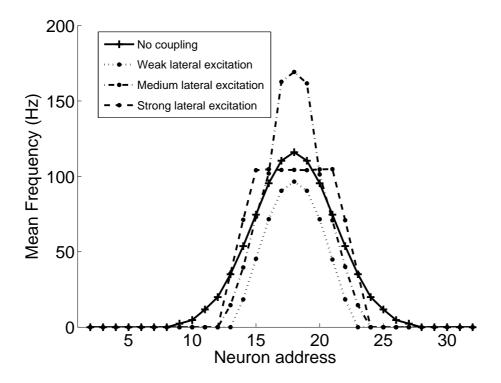

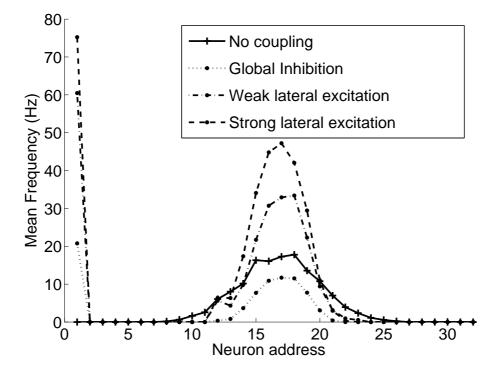

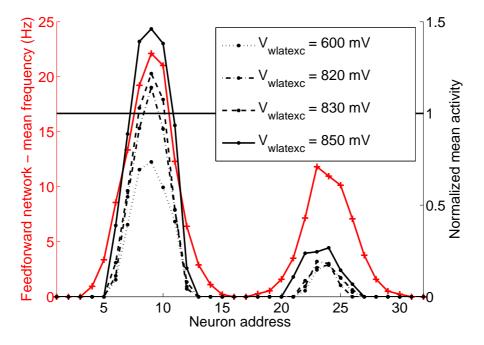

| 4.2  | Feature tuning curve sharpening                                                  | 54 |

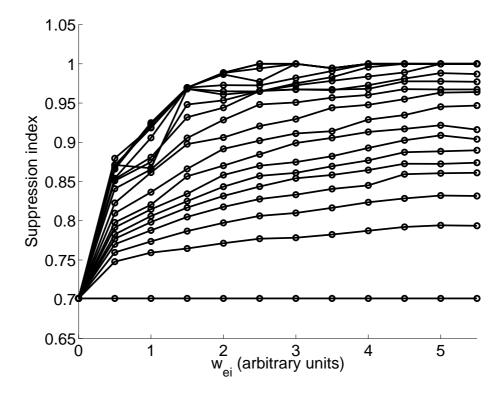

| 4.3         | Suppression of less effective stimuli                                      | 55       |

|-------------|----------------------------------------------------------------------------|----------|

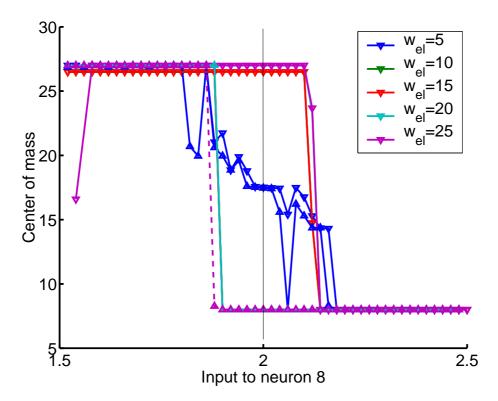

| 4.4         | Hysteretic behavior.                                                       | 56       |

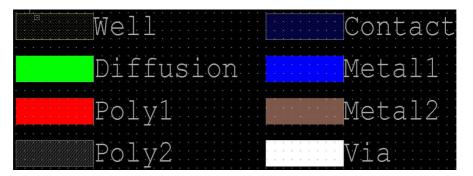

| 5.1         | Chip layout legend.                                                        | 61       |

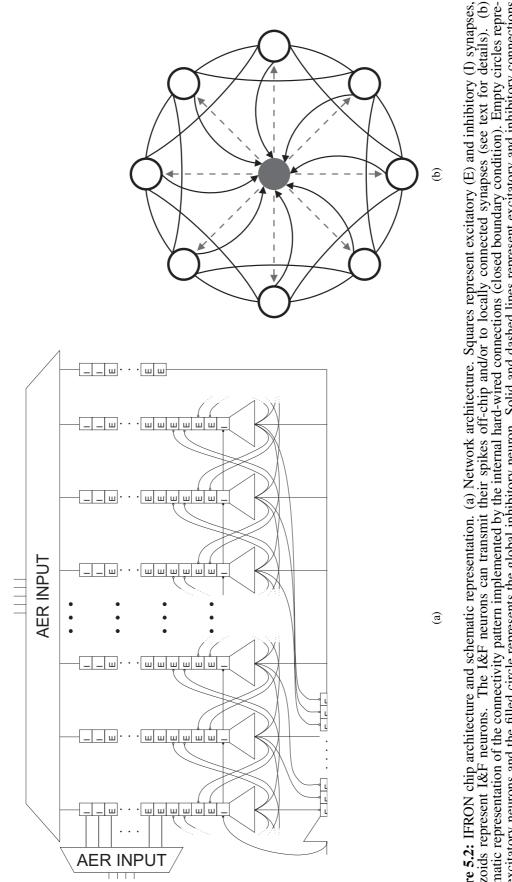

| 5.2         | IFRON chip architecture and schematic representation.                      | 63       |

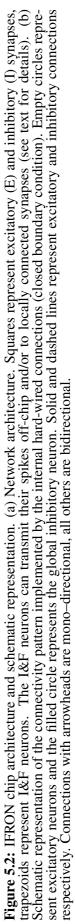

| 5.3         | IFRON chip layout and photograph.                                          | 64       |

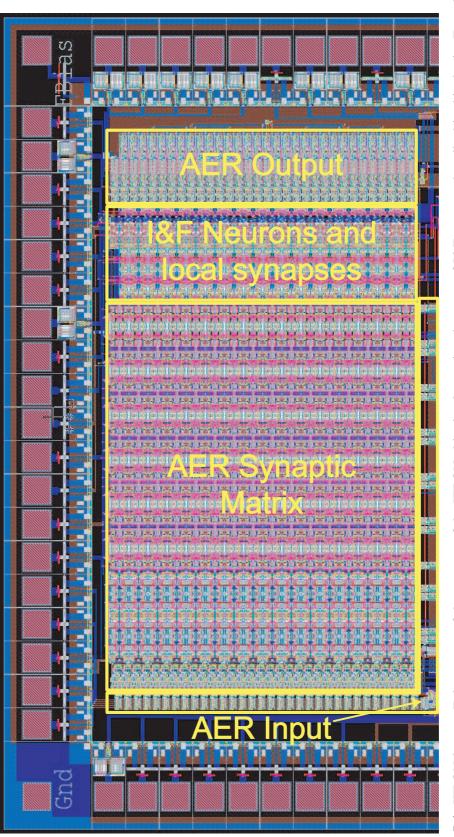

| 5.4         | IFRON layout.                                                              | 65       |

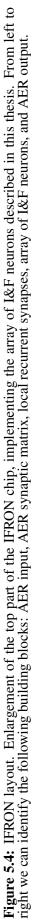

| 5.5         | Layout of the I&F neuron.                                                  | 67       |

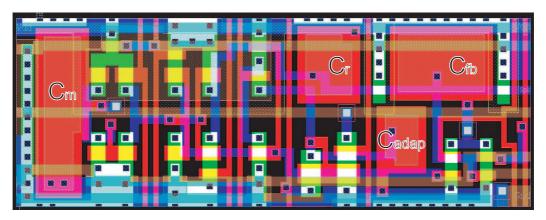

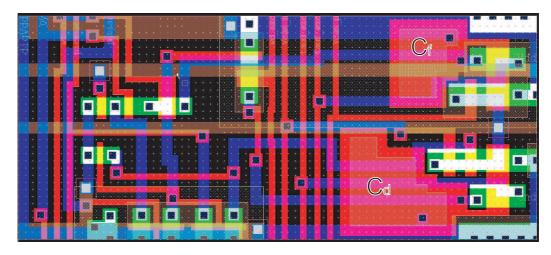

| 5.6         | Layout of the adaptive synapse                                             | 67       |

| 5.7         | Handshaking circuit for the AER input.                                     | 68       |

| 5.8         | Layout of the AER input decoder.                                           | 68       |

| 5.9         | Layout of the AER output.                                                  | 70       |

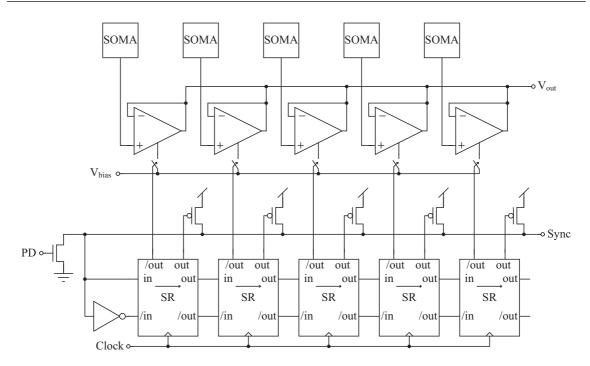

| 5.10        | The one-dimensional voltage scanner                                        | 71       |

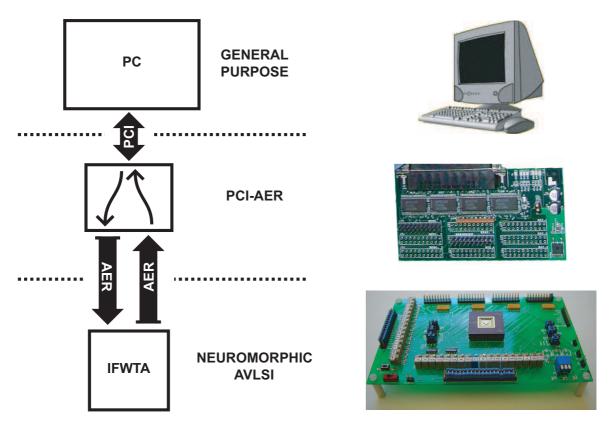

| 5.11        | The IFRON chip test setup                                                  | 73       |

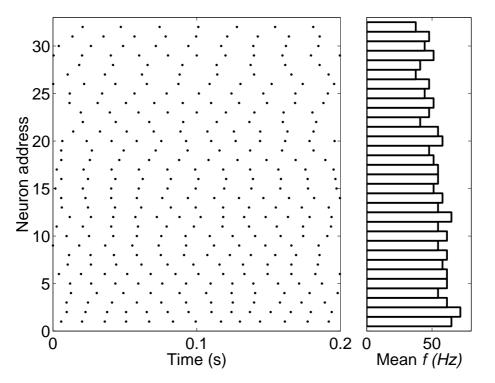

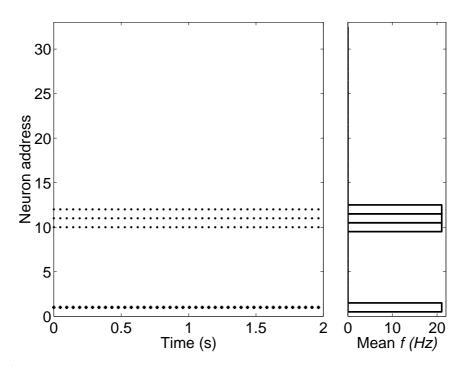

| 5.12        | Network response to homogeneous constant input current with all synaptic   |          |

|             | connections disabled                                                       | 74       |

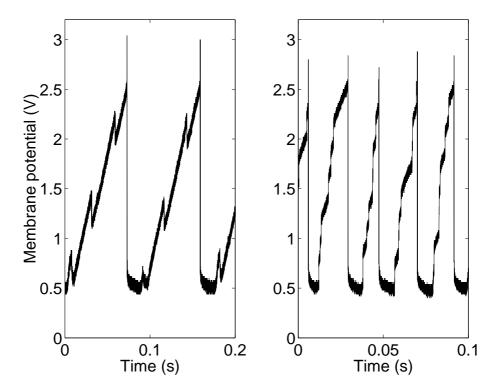

| 5.13        | Membrane potentials                                                        | 75       |

| 5.14        | Strong WTA behavior.                                                       | 76       |

| 5.15        | Traveling wave.                                                            | 76       |

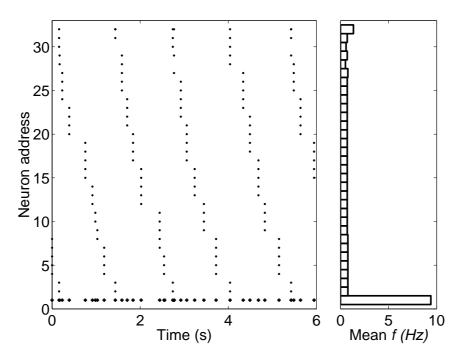

| 5.16        | Raster plot of the input stimulus used in the sharpening experiment        | 77       |

| 5.17        | Raster plot of the activity of the feed-forward network in response to the |          |

|             | stimulus shown in Fig. 5.16.                                               | 77       |

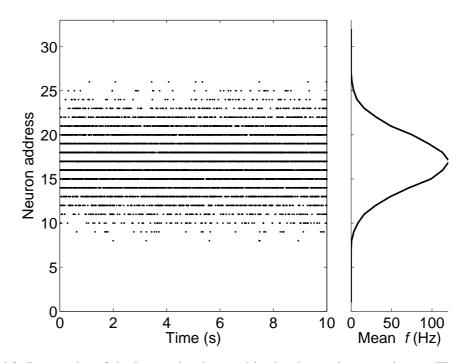

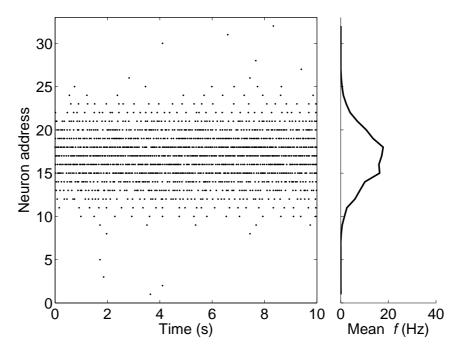

| 5.18        | Sharpening                                                                 | 78       |

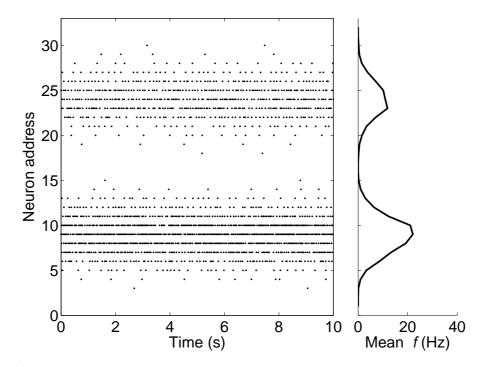

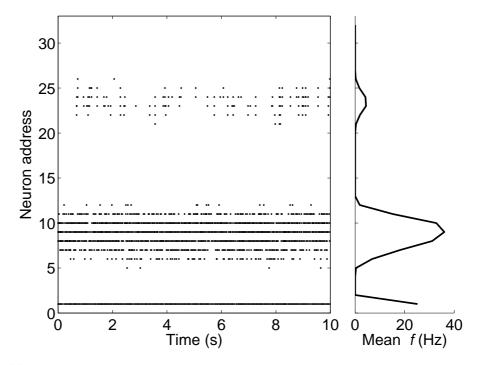

| 5.19        | Raster plot for the suppression experiment: feed-forward network response. | 79       |

| 5.20        | Raster plot for the suppression experiment: recurrent network response     | 79       |

| 5.21        | Suppression for three different values of global inhibition                | 80       |

| 5.22        | Suppression for several values of lateral excitation.                      | 80       |

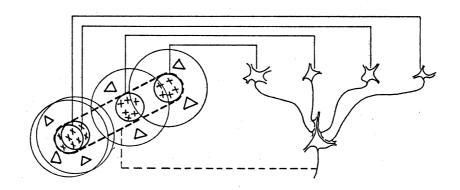

| 6.1         | Feed-forward model of the organization of simple receptive fields (adapted |          |

|             | from [59])                                                                 | 85       |

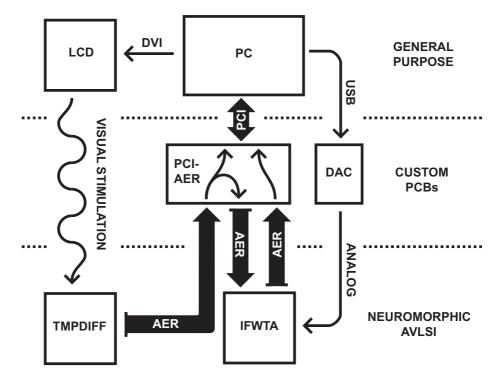

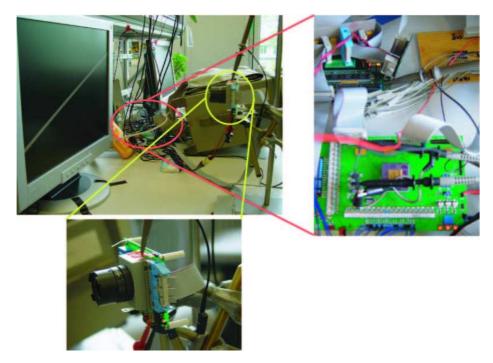

| 6.2         | AER vision system setup                                                    | 89       |

| 6.3         | AER vision system setup (photograph).                                      | 89       |

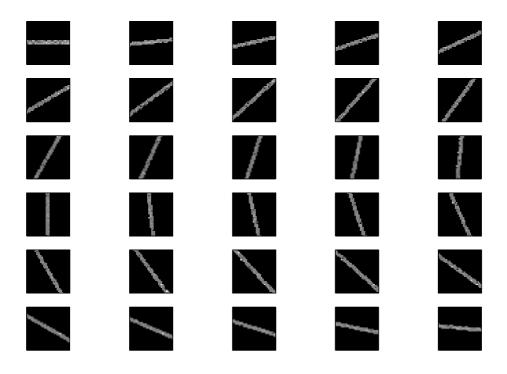

| 6.4         | Integrated response of the silicon retina to oriented flashing bars        | 90       |

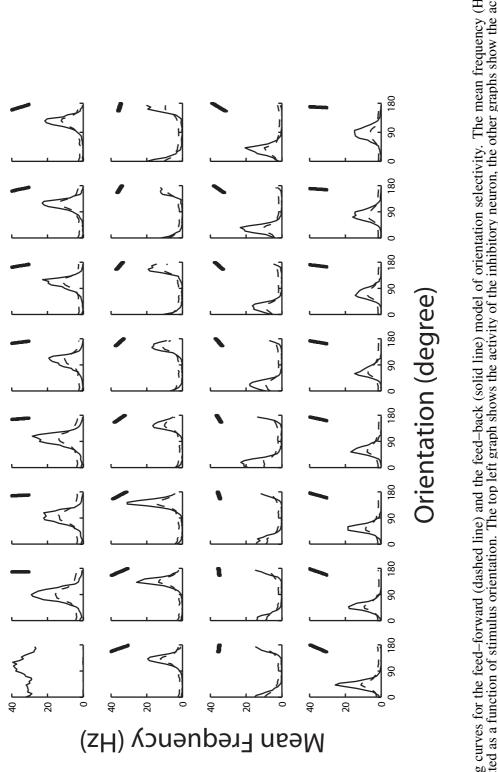

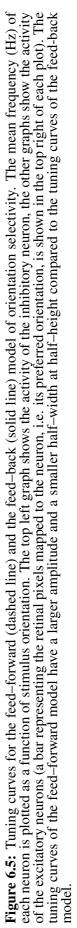

| 6.5         | Tuning curves for the feed-forward and the feed-back model of orientation  |          |

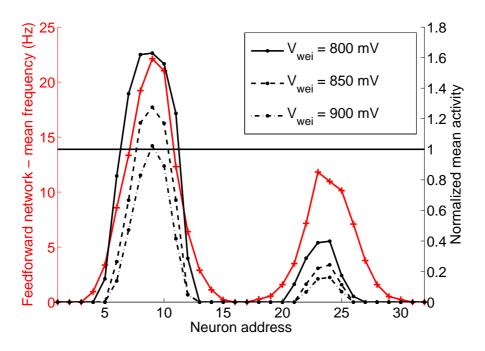

|             | selectivity                                                                | 91       |

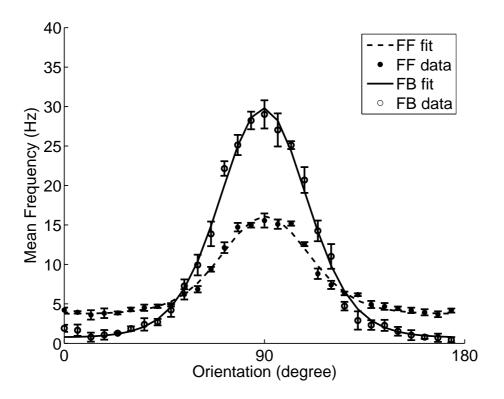

| 6.6         | Tuning curves for the feed–forward and the feed–back model of orientation  | 02       |

| 6.7         | selectivity for the neuron with vertical preferred orientation.            | 92<br>93 |

|             | •                                                                          |          |

| A.1         | Evolution of the residual service time over time                           | 102      |

| <b>C</b> .1 | Structure of variables used in the IFRON software simulation tool          | 116      |

# **List of Tables**

| Summary of the characteristics of four access algorithms for AE communi-                |                 |

|-----------------------------------------------------------------------------------------|-----------------|

|                                                                                         | 11              |

| Characteristics of the spiking WTA networks described in the literature                 | 60              |

| Parameters obtained by least-squares fitting of the data to the von Mises distribution. | 94              |

|                                                                                         | cation channels |

## **Chapter 1**

## Introduction

"As engineers we would be foolish to ignore the lessons of a billion years of evolution" - Carver Mead, 1993

### **1.1 Motivation**

Biological systems perform complex processing tasks on a scale and speed that can not be achieved by conventional digital computers. Machine simulation of human functions has been a challenging research field since the advent of digital computers. Despite the resources dedicated to this field, humans still outperform the most powerful computers in relatively routine functions such as vision. For example, in spite of about 50 years of research in the field of pattern recognition, the general problem of recognizing complex visual patterns with arbitrary orientation, location and scale remains largely unsolved [67]. Artificial systems have been implemented to solve more specific tasks in the field of pattern recognition, for example, the problem of character recognition. Machine simulation of character recognition has been the subject of intensive research for the last three decades, yet it is still far from achieving performances comparable with those of humans [8].

Computation in biological systems is based on completely different principles from those used in conventional digital computers. The disparity between the effectiveness of computation in the nervous system and in a computer is primarily attributable to the way the elementary devices are used in the systems, and to the kind of computational primitives they implement [87]. In digital systems the elementary devices are transistors whose physical properties are not exploited as computational primitives: the representation of information relies on digital values, ignoring the analog nature of transistors. The elementary operations, or computational primitives, are usually the logical operations AND, OR, and NOT.

*Neuromorphic engineering* plays a key role in the development of artificial systems capable of achieving performance figures comparable to those of the biological neural systems. This emerging research field is a methodology for implementing biologically inspired devices, comprised of artificial neurons and synapses, and combinations of sensory and computational modules in hardware. The term *neuromorphic* was coined by Carver Mead in the late '80s to describe Very Large Scale Integration (VLSI) systems comprised of ana-

log circuits and built to mimic biological neural cells and architectures [88]. The main idea behind neuromorphic engineering is to implement the same basic operations as those of the nervous system starting from the elementary operations defined by transistor device physics. Mead pointed out that the same physical principles apply to the conductance of a transistor operated in subthreshold and to the macroscopic conductance of a population of voltage–gated channels<sup>1</sup>, giving rise to an exponential dependence on the applied voltage in both cases.

Implementing artificial neural systems to perform specific tasks is not the only aim of neuromorphic engineering. Neuroscience can take advantage of full–custom neuromorphic integrated circuits as a means for testing hypotheses concerning the computation carried out by the brain. The neocortex is often considered the relevant brain structure in studying the evolution of intelligence because higher cognitive abilities are generally associated with neocortical functions, and primate encephalization is primarily a result of increased neocortical size [45, 68, 104]. Humans do not have the largest brain or cortex but they have the largest number of cortical neurons, the highest conductance velocity and smallest distances between cortical neurons [102]. Therefore human cortex probably has the greatest information processing capacity. As the neural circuits in the cortex are primarily responsible for the intelligent performance of our brain, I believe it is important to apply our research to the design of VLSI neuromorphic systems that implement models of cortical circuits.

The neocortex, so called because it is the area of the brain acquired most recently in evolution, is formed of a folded sheet of cells varying between 2 and 4 mm in thickness, and is the most superficial part of the cortex. The most striking morphological feature of the neocortex is that its neurons are arranged in six well-defined layers. Although this sixlayer structure is characteristic of the entire neocortex, the thickness of individual layers varies in different functional regions of cortex [71]. In addition to this horizontal layer structure, a vertically oriented columnar elementary pattern of organization is present in the cerebral cortex. It takes the form of units called modules or columns, each involving thousands of neurons in repeating patterns [98]. The observation that the somatic sensory cortex comprises elementary units of vertically linked cells was first noted in the 1920s by the neuroanatomist Rafael Lorente de Nó, based on his studies in the rat. In the 1950s, electrophysiological experiments indicated the presence of a similar repeating structure in cats, and later in monkeys. Vernon Mountcastle found that vertical microelectrode penetrations in the primary somatosensory cortex of these animals encountered cells sensitive to identical mechanical stimuli at the same location. Soon after this pioneering work, David Hubel and Torsten Wiesel discovered a similar arrangement in the cat primary visual cortex [59]. Each column in the primary visual cortex is about  $30-100 \ \mu m$  wide and  $2 \ mm$  high. Cells within a column share the same retinal position and preferred orientation, for this reason these groupings are called *orientation columns*.

There is reason to believe that, despite significant variation across cortical areas, the

<sup>&</sup>lt;sup>1</sup>The membrane proteins that give rise to selective permeability are called ion channels: each kind of ion has its own preferred channel through which it passes more easily than other kinds of ions. Individual channels open or close in a stochastic manner. Voltage–gated channels are able to sense the electrical potential across the membrane and the probability that any given channel is open varies with the membrane potential.

pattern of connectivity between cortical neurons is similar throughout neocortex. This implies that cortex is a kind of general purpose computer, with various regions specialized to perform certain tasks [43, 44]. An intriguing hypothesis about how computation is carried out by the brain is the existence of a finite set of computational primitives used throughout the cerebral cortex. If we could identify these computational primitives and understand how they are implemented in hardware, then we would make a significant step toward understanding how to build brain-like processors.

There is an accumulating body of evidence that suggests that one such computational primitive consists of a recurrent network of neurons with a well defined excitatory/inhibitory connectivity pattern [43]. The neurons of this network cooperate through excitatory connections and compete through a global inhibitory neuron or a population of inhibitory neurons. An important property of this specific network is the ability to perform signal restoration. Signal restoration is a crucial attribute of a computing system, since it provides reliability of computation. In digital computers, signal restoration is performed locally on the output physical variable of each node, where each state variable is restored to a binary value. The process of computation is very different in biological systems. A neuronal system is analog, therefore there are no discrete values to which a state variable can be corrected. Small perturbations can easily cause the system to deviate from the correct computation. Therefore, analog computations are intrinsically more sensitive to noise. Despite this, biological systems perform highly reliable computation. I believe that the robustness of biological computation is achieved through cooperative-competitive interaction among elementary units of recurrent networks. In these systems, the output of each node is not only a function of the local input, but is also influenced by the activity of other nodes. If the output of a single node is affected by noise, its activity will be corrected by other nodes and signal restoration will be based on the *context* of the signal.

This thesis is about the analog VLSI implementation of an instance of such a cooperative neural system and the hardware/software infrastructure to operate it. The neuronal circuit I implemented in hardware consists of a VLSI network of integrate-and-fire (I&F) neurons and dynamic synapses. The connectivity within this network models the cooperative–competitive nature of connectivity observed in the cortex. The I&F neurons cooperate through local recurrent connections while a global inhibitory neuron is used for the competitive part of the computation. The VLSI circuit I developed is able to select relevant signals among distractors and noise, thus performing signal restoration.

#### **1.2** Outline of this Thesis

This thesis is divided into seven chapters. In this chapter I gave some introductory remarks on the motivation for building a programmable multi-chip VLSI system for exploring the computational capabilities of cooperative competitive networks. In chapter 2 I introduce the Address–Event Representation (AER) for inter–chip communication, review different access topologies for Address–Event communication channels and present a PCI–AER hardware infrastructure for building event–based multi–chip systems. Chapter 3 provides an introduction to the devices and the basic analog circuits required to understand the neuromorphic circuits used throughout the thesis. Also, I describe the I&F silicon neuron and the adaptive silicon synapses implemented in my VLSI neural network. In chapter 4 I discuss the origins of cooperative-competitive network models and the analytical methods used to characterize them. I then introduce the specific architecture implemented in the context of this thesis and present simulation results. The VLSI implementation of this particular cooperative-competitive spiking network (the IFRON<sup>2</sup> chip) and the results obtained by testing its behavior in response to well-controlled artificial stimuli are described in chapter 5. Both the software simulation and the hardware implementation show that the spiking version of the cooperative competitive neural network exhibits the key features present in previously proposed continuous models. In particular, the original results obtained with the IFRON chip show the robustness of these features to real-world conditions. This robustness and the reliability of the complete hardware infrastructure are further demonstrated in the experiment described in chapter 6: using my VLSI neural network, the hardware inter-chip communication infrastructure and a silicon retina (designed by Patrick Lichtsteiner under the supervision of Dr. Tobias Delbruck) we implemented a multi-chip system for modeling orientation selectivity tuning of neocortical cells. I conclude the thesis by summarizing the results achieved and discussing ideas about further work and outlook in chapter 7.

<sup>&</sup>lt;sup>2</sup>IFRON stands for I&F Ring of Neurons.

## Chapter 2

# The Address–Event Representation and Event–Based Neuromorphic Systems

To build complex neuromorphic systems with significant computational power and high flexibility we need to resort to multi-chip systems. For example, a common strategy is to separate the sensing stage (silicon retinas, silicon cochleas) from further computing stages (spiking neural networks), transmitting signals between chips. In this case, the main advantages are the possibility of achieving higher density in the sensing stage, allowing convergence of the output of multiple sensors to a single processing stage, divergence from one sensor to multiple processing modules, and constructing hierarchical processing stages using multiple instances of the same chip. However, in these systems the inter-chip connectivity across chip boundaries is severely limited by the small number of input-output connections available with standard chip packaging technology (of the order of a few hundreds pins). One strategy for overcoming this problem is to use *time-division multiplexing*. The activity of analog VLSI neurons, as for biological neurons, is sparse, from a few Hz to a couple of hundred Hz. The speed of digital buses (tens of megahertz) can be traded for connectivity among spiking networks by sharing a few wires to communicate (infrequent) events. If the signals to be transmitted across chips are encoded by *spikes* (i.e. stereotyped non-clocked digital pulses), as it is the case for most neuromorphic devices, the most efficient communication protocol that can be used is based on the Address-Event Representation (AER) [20, 37, 77, 84]. In this representation, input and output signals are real-time, digital events that carry analog information in their temporal structure (inter-spike intervals).

In this chapter I first review the different access topologies that have been proposed for AE communication channels, and then describe the specific AER hardware infrastructure and the supporting software developed and used for the research project described in this thesis.

## 2.1 The Address–Event Representation

The AER uses binary–encoded words to represent address events:  $log_2(N)$ –bit packets that uniquely identify one of N sources. Each word encodes the address of the sending node (see

Fig. 2.1). Events generated by sending nodes are communicated through the channel to one or more external receivers. Different approaches are available for the transfer of the data between the transmitting array of neurons and the channel. The *access technique* refers to the algorithm describing the behavior of the *access circuit*, which is the part of the sending chip that allows the transfer of the data to the channel. When more than one sending node attempts to transmit their addresses at the same time, an event collision occurs. We can distinguish two classes of access technique considering how the algorithm deals with event collisions: arbitrated and non–arbitrated AER.

In arbitrated AER [15, 37, 77, 84], an arbiter decides which of a number of colliding events has the right to access the transmission channel and queues the losers of this competition. This method introduces distortions in the temporal structure of events when collisions occur. Distortions can be minimized by improving the arbitration technology and shortening the time needed to process a single event. The arbitrated AER communication protocol was first introduced by Mahowald [84]. In her PhD thesis, she described a neuromorphic visual system composed of three subsystems: a *silicon retina*, a *stereocorrespondence chip* and a *silicon optic nerve*. The silicon optic nerve implements an inter–chip communication protocol that takes advantage of the pulse coding of the silicon retina. A self–timed digital multiplexing technique using an AER takes care of sending pulses from the silicon retina to the stereocorrespondence chip. The stereocorrespondence chip is designed to use the AER communications framework to receive data from two retina chips and estimate the location of objects in depth using the bilateral retinal input.

Another line of research has concentrated on non-arbitrated AER schemes [22, 92, 93]. Mortara et al. [92, 93] proposed a transmission circuit and algorithm that perform error detection to discard colliding events (event loss). This approach simplifies the encoding hardware, reducing the transmission time and therefore the probability of collisions. However, this is a lossy encoding of the neural activity, since colliding events will be thrown away. Brajovic [22] proposed a lossless address-event encoding which provides the identity of up to t ( $t \ge 2$ ) colliding events. If there are more than t simultaneous events, then their addresses are not recoverable and they are lost. The number t is determined by the size of the encoder.

In this work I used the arbitrated AER protocol originally proposed by Mahowald [84]. My choice in favor of preventing data loss is supported by the availability of good arbitration technology, which allows us to assume that distortions introduced in the temporal structure of events are negligible.

## 2.2 Analysis of Time Multiplexing Techniques

A comparative study of access topologies for AE communication channels has been presented by Culurciello and Andreou in [33]. In this section I summarize their analysis and results, and emphasize the results that support my choice of using arbitrated AER.

The design of a communication channel to implement point-to-point connectivity among neuromorphic chips has to deal with several specifications. The channel *capacity* is

**Figure 2.1:** Schematic diagram of an AER chip-to-chip communication example (adapted from [37]). The address event bus transmits the encoded address of a sending node on the source chip as soon as it generates an event. On the receiver chip, the incoming address events are decoded and transmitted to the corresponding receiving node.

defined as the maximum transmission rate (inverse of the minimum communication cycle period). The mean time required for coding and decoding the event from the sending node to the receiving node is called *latency* and its standard deviation is called *temporal dispersion*. With conventional polling techniques, nodes are sequentially invited to transmit and latency increases proportionally with the number of sending nodes. When an event–driven transmission is implemented, latency is proportional to the number of active neurones, which is usually much smaller than the total number of neurons due to the infrequent nature of neural activity. Temporal dispersion can be minimized giving priority to new events. Event queuing leads to a temporal dispersion proportional to the cycle time.

The *integrity* of the channel is defined as the fraction of events delivered to the correct receiving node. This is related to the problem of event collisions. As already mentioned in section 2.1, there are two possible ways of dealing with collisions: arbitrated coding and non–arbitrated collision–detection coding. In the first technique, originally proposed by Mahowald [84], arbitration schemes are used to handle event collisions. An arbitration binary tree is used to select the event transmitted on the Address Event (AE) bus; colliding events are queued and transmitted after the current event. Since collisions are resolved through queuing, distortions are introduced in the temporal structure of events when collision–detection coding [93]. In this case the AE transmitted is valid only in absence of collisions. When a collision occurs, the AE is not valid and should be discarded by the receiver. This approach, compared with arbitration, decreases the probability of collisions which makes the sampling of the events simpler, however it has the disadvantage of event loss due to collisions (lower integrity).

Let us consider how the AEs are transferred from the transmitting nodes to the channel. I will discuss four different access techniques and corresponding access circuits. A quality metric Q is defined to estimate the best access technique:

$$Q = \max_{f_{AC}} \left( \frac{S(G, f_{AC})}{P_c(G, f_{AC}) \mu_{sys}(G, f_{AC})} \right)$$

$f_{AC}$  is the function performing the mapping from the sequence of events generated in the spiking network to the sequence of multiplexed data transmitted by the channel; the best access technique is the one which maximizes Q with respect to  $f_{AC}$ . G is the normalized offered load. S,  $P_c$  and  $\mu_{sys}$  are functions of  $f_{AC}$  and G. They are defined as the normalized throughput of the channel (usable portion of the channel capacity), the power used by the access system, and the average latency, respectively. S and G are normalized by the transmission time  $T_{chan}$ , the inverse of the channel rate  $F_{chan}$ .

Using this metric Culurciello and Andreou compare throughput and theoretical expected latency for the following four access algorithms: (1) sequential scanning, (2) the ALOHA–based algorithm, (3) a priority encoder and (4) an arbitration tree.

#### 2.2.1 Sequential Scanning

In the sequential scanning case the activity of the array is sequentially and repeatedly sampled, and the events of each active node are transmitted in a predetermined sequence. This is a synchronous approach, controlled by an external clock, which does not adapt to the activity of the sending nodes (e.g. video signals). It is particularly suited to transmit uniformly distributed events. Two consecutive scans of the same sending node are performed with a mean time interval

$$T_{sr} = T_{chan}N$$

where N is the number of nodes in the array. The variability of  $T_{sr}$  is, in general, very small, as well as the variability of the latency between requests and acknowledges from the receiver (handshaking signals) producing a practically deterministic statistic of the scanning registers. Collisions in access to the channel are not possible using this approach. Only the selected node can transmit its activity; events generated by other nodes are queued until the scanning process reaches the active nodes. A slow channel can still be considered to induce collisions since it does not transmit events fast enough, causing data saturation. Collision probability increases with increasing number of sending nodes N (constant capacity), and decreases for increasing capacity of the channel (constant N).

The maximum throughput, S, is given by

$$S = G = \frac{T_{sr}}{T_{event}} = N f_{event} T_{chan}$$

where  $T_{event} = 1/f_{event}$  gives the average array inter-event time, and  $f_{event}$  is the event rate. S increases linearly with the number of sending nodes, until data loss occurs when it saturates to the bandwidth of the channel.

An estimation of the average latency is given by half of the mean time between two scans of the same sending node:

$$\mu_{sys} = \frac{T_{sr}}{2} = \frac{T_{chan}N}{2}$$

As for the throughput, the average latency increases linearly with an increasing number of nodes.

The high throughput of scanning is subject to the condition that the activity of the array is adapted to the scanning frequency. Neuromorphic systems usually generate signals with a very high dynamic range, which would be truncated if adaptation or automatic gain control was used to reduce the firing rate. Therefore, sequential scanning is not a suitable access algorithm if data loss cannot be tolerated.

#### 2.2.2 ALOHA Access Protocol

The ALOHA access protocol [113] is the simplest asynchronous access algorithm. The ALOHA network was an early computer networking design, created at the University of Hawaii in 1970 under the leadership of Norman Abramson and Franklin Kuo. In this event driven type of access, the active node sends an event as soon as the event is generated.

Let us assume that each sending node produces Poisson distributed events (a reasonable hypothesis for neuromorphic chips). The activity of the whole array will have a Poisson distributed sum of Poisson point processes. For a generic Poisson train of events with mean firing rate, f, the probability P(k, T) of obtaining k events in the observation window T is:

$$P(k,T) = \frac{(fT)^k}{k!}e^{-fT}$$

In our case, f is the inverse of the average array inter–event time ( $f = 1/T_{event} = f_{event}$ ). We are interested in the observation window given by  $T_{chan}$ , the inverse of the channel rate  $f_{chan}$ :

$$P(k,G) = \frac{G^k}{k!}e^{-G}$$

where  $G = T_{chan}/T_{event}$ . An event is transmitted without a collision if the previous event occurs at least  $T_{chan}$  seconds earlier, and the next event occurs at least  $T_{chan}$  seconds later: no other events should occur in a time window of  $2T_{chan}$  seconds centered around the current event. Given the Poisson distribution of input events, the probability of an event to be transmitted without a collision is  $p(0, 2G) = e^{-2G}$ , therefore the probability of an access collision is:

$$p_{coll}(T_{chan}) = 1 - p(0, 2G) = 1 - e^{-2G}$$

The throughput, S, of the channel is given by the load, G, multiplied by the probability of a successful transmission,  $p(0, 2G) = e^{-2G}$ , and can be expressed as a function of the collision probability:

$$S = Ge^{-2G} = \frac{1 - p_{coll}}{2} ln\left(\frac{1}{1 - p_{coll}}\right)$$

The latency,  $\mu_{sys}$ , is a function of the collision rate:

$$\mu_{sys} = \frac{1}{1 - p_{coll}} T_{chan} \tag{2.1}$$

The ALOHA access protocol generates data loss, and should be used when the probability of collision is sufficiently low to guarantee a low rate of event losses.

#### 2.2.3 Priority Encoder

The Priority Encoder (PE) algorithm is similar to the ALOHA access protocol. It is an event-driven, asynchronous access protocol in which any cell (identified by an ordering number) can access the channel at any time, provided that the channel is free. In the case of a collision, only the cell identified by the lowest number (fixed priority) can access the channel, while requests from cells generating the colliding events are queued. Depending on the implementation of the PE channel, different behaviors can occur in response to a collision. If there is no buffering between the PE and the asynchronous channel, when a collision occurs the higher PE cell wins and accesses the channel for communication, even if a lower priority cell is already waiting for the acknowledge from the receiver. In this case the receiver either randomly gets one of the two addresses and the other event is lost, or it gets the logical OR of the two addresses (both events are lost). To improve the response to collisions, buffering of inputs can be used to disable any change in the buffer until the current handshaking cycle is terminated. This implementation excludes the possibility of randomly discarding one of two colliding events, but spurious events might be detected if the receiver is fast enough to detect glitches at the output of the PE during its settling time. The unbuffered PE is analogous to an ALOHA access protocol when events are sparse and the probability of collisions is low. The collision probability and the channel throughput, S, have the following expressions:

$$p_{coll}(T_{chan}) = 1 - p(0, 2G) = 1 - e^{-2G}$$

$S = Ge^{-2G}$

For buffered PE access, the channel throughput is given by:

$$S = \min\left(1, G\right)$$

The latency of the system has the same expression as for the ALOHA access algorithm (see Eq. 2.1). Similarly to ALOHA, PE is not a suitable access algorithm if data loss cannot be tolerated. Furthermore, the collision probability should be low to minimize the number of lost events.

#### 2.2.4 Arbitrated Access

Arbitrated access can be used to improve the efficiency of all asynchronous access algorithms. An event-driven arbitration scheme queues colliding events instead of discarding them, and thus obtains higher channel throughput. Latency is increased by the additional time required for the arbitration circuitry to identify the winning cell. Queuing and increased latency alter the inter-event time distribution of the array activity. In [15], Boahen presents an exhaustive analysis of arbitrated access which I summarize in the following. To derive latency and throughput of the channel, a well-known result from queuing theory is used: the Pollaczek-Khinchin mean value formula (see appendix A). It gives a compact expression for the average waiting time  $\overline{w}$  in the queue [73]:

$$\overline{w} = \frac{\lambda \overline{x^2}}{2(1-G)}$$

| Access     | Access      | Throughput | Throughput | Circuit    | Integrity |

|------------|-------------|------------|------------|------------|-----------|

| Туре       | Modality    | S (low N)  | S (high N) | Complexity |           |

| Sequential | Externally  | Low        | High       | Low        | $\leq 1$  |

| scanning   | driven      |            |            |            |           |

| ALOHA      | Self driven | Low        | Low        | Low        | $\leq 1$  |

| or PE      |             |            |            |            |           |

| Arbitrated | Self driven | Low        | High       | High       | 1         |

**Table 2.1:** Summary of the characteristics of four access algorithms for AE communication channels. Only arbitrated access guarantees no data loss (integrity equals 1), but it requires high circuit complexity.

where  $\lambda$  is the mean rate of incoming Poisson distributed events. In our case  $x = T_{chan}$ ,  $\lambda = G/T_{chan}$  and we assume that the service time x is always equal to  $T_{chan}$ , and therefore  $\overline{x^n} = T_{chan}^n$ . The mean of the number of cycles spent waiting is then given by:

$$\overline{m} = \frac{\overline{w}}{T_{chan}} = \frac{G}{2(1-G)}$$

Let us consider the activity of a neural population that is responding to a stimulus. The activity of the population is clustered at temporal locations where the stimulus is presented and it is clustered at spatial locations defined by the stimulus. It has also an unstructured stochastic component given by noise in the input and in the system. These statistically–defined clusters are called *neuronal ensembles*. We can express the latency of the channel as a function of the *neuronal latency*  $\mu$  of the ensemble  $\varepsilon$ . Let us assume that  $T_{chan}$  is short enough to transmit half the spikes in an ensemble in  $\mu$  seconds, that is:

$$\frac{\mu}{T_{chan}} = \frac{N_{\varepsilon}}{2G}$$

where  $N_{\varepsilon}$  is the number of spikes in the ensemble and 1/G is the average number of cycles used to transmit one spike. The latency  $\mu_{sys}$  of the channel or wait time can be expressed as a fraction of the neuronal latency  $\mu$ :

$$\mu_{sys} \equiv \frac{\left(\overline{m}+1\right)T_{chan}}{\mu} = \frac{G}{N_{\varepsilon}} \left(\frac{2-G}{1-G}\right)$$

Since every spike is eventually transmitted the throughput S is equal to the load G. When collisions occur the cost of the high throughput is represented by a longer latency. This access algorithm is used when event losses can not be tolerated. Fast arbitration circuitries has to be designed to minimize latency.

#### 2.2.5 Summary

Table 2.1 summarizes the characteristics of the four access algorithms described in this section. In Fig. 2.2, the merit criterion Q is plotted as a function of the number of sending nodes. Given the sparseness of neuromorphic systems' activity, sequential scanning is the least appropriate access algorithm for transmission of these type of data. A self driven

**Figure 2.2:** Merit criterion versus number of cells for three different access protocols (adapted from [33]). The plot shows that when the number of cells in the sending chip is low (smaller than  $10^5$ ), the ALOHA access protocol offers the best performance. When the number of cells is high (greater than  $10^5$ ), the probability of collisions increases. An increased number of collisions dramatically affects the performance of the ALOHA access protocol, reducing its throughput and increasing its latency. In this case the arbitrated access protocol is shown to be the most efficient.

access modality is certainly more efficient when the sending nodes are silent most of the time. Arbitrated access is preferable to ALOHA and priority encoder algorithms, if the timing skew introduced is negligible and loss of data cannot be tolerated by the system. For large numbers of sending nodes, arbitrated access shows the best performances. Typical numbers of sending nodes in the most recent neuromorphic implementations range from hundreds, to hundreds of thousands of nodes, arranged in one or two dimensional arrays, encouraging the choice of arbitrated AER. Arbitrated circuitry has a large overhead in terms of circuit and layout design, compared with non–arbitrated schemes. But as standard CMOS technology improves and we begin to design arrays with large number of neurons, the proportion of the arbiter layout with respect to the rest of the system becomes smaller and smaller. For example, in a 0.35  $\mu$ m chip with 256 neurons and  $\approx$  10000 synapses, the core of the chip occupies an area of 6.8  $mm^2$  whereas the arbiter layout area is 0.4  $mm^2$  (about 6% of the core area).

### 2.3 Arbitrated AER for Multi–chip Systems

The AER protocol originally proposed by Mahowald [84] is for single sender, single receiver systems. This is known as the Point-to-Point (P2P) AER protocol [1]. The process

**Figure 2.3:** Point–to–Point handshake protocol. A node within the sender chip initiates a handshake cycle by prompting the sender to make a request (initiation signal). After making a request, the sender puts the data on the address event bus. Since the address lines may take different amounts of time to stabilize a *data valid* line is used to signal when the data on the address bus are set. The receiver acknowledges receipt of the data and the initiation signal is reset to let the sender drop the request and complete the handshake cycle.

**Figure 2.4:** SCX handshake protocol. A node within the sender chip initiates a handshake cycle by prompting the sender to make a request. The sender can write the data on the AE bus only after the receiver acknowledges. The handshake cycle is complete only when both request and acknowledge are reset.

of sending events from one chip to the other is regulated by a *handshake* (see Fig. 2.3). A simple handshake involves two chips: a *sender* chip and a *receiver* chip. A node in the sender chip initiates an event by activating a *request* signal. The receiver chip must answer the request by activating an *acknowledge* signal, after which it reads the data on the address–event bus. After the *acknowledge* signal is activated, the sender chip removes the request to let the receiver chip removes the acknowledge signal. The handshake cycle is completed when the acknowledge signal is removed by the receiver chip, and another cycle can be initiated by a node in the sender chip.

Systems containing more than two AER chips can be assembled using additional, offchip arbitration. These off-chip arbiters can also use lookup-tables and processing elements to remap, time-stamp and perform digital operations on address-events [34, 37]. The P2P protocol is not suitable for multi-chip systems because the sender drives the address bus, shared by all senders in this case, as a consequence of activating the request. In a multi-chip system only the acknowledged sender should drive the address bus, to prevent data corruption in case two senders attempt to send an event at the same time.

In 1998, Deiss et al. [37] proposed the SCX-1 Local Address-Event Bus (LAEB) for

multi-chip AER systems (SCX stands for *Silicon Cortex*, see section 2.4). The authors presented a communication protocol for multiple senders and multiple receivers on the same address bus. Each chip connected to the local address bus has a dedicated pair of request and acknowledge lines. The handshake protocol is represented in Fig. 2.4.

A recent successful evolution of the AER is the burst-mode "word-serial" addressevent link proposed by Boahen [16, 17, 18]. This design uses address-events to communicate between cells in the same or in different bidimensional arrays. Row and column addresses are not transmitted in parallel, as in previous designs, but serially. The loss in speed due to serial transmission is compensated by not retransmitting the row address if the next event is from the same row: row activity is encoded in a burst consisting of the row address followed by a column address for each active cell. Multi-chip systems can be build in a chain extending the single-transmitter-single-receiver link using merges and splits<sup>1</sup> (see [30] for an example of such architecture).

### 2.4 AER Hardware Infrastructures

The hardware infrastructure is an essential instrument to fully characterize neuromorphic prototype chips. This infrastructure has to provide ways to stimulate and monitor the activity of a single chip. In addition, it has to be able to interface several chips and dynamically define the connectivity among them, implementing complex multi–chip systems. Furthermore, it should allow logging of data from all chips, allowing off–line analysis.

Different approaches can be pursued to build neuromorphic multi-chip systems: dedicated full-custom circuits can be implemented to support specific AER devices, or a general-purpose full-custom architecture can be designed to host any AER device compliant to a certain standard. Several multi-chip systems have been implemented with both approaches. Examples of dedicated full-custom multi-chip systems are described in [30, 57]. These systems comprise EPROMs or FPGAs for remapping of the addresses, but they do not include any device to store the activity of the AER chips (requiring a separate acquisition instrument, usually a logic analyzer, to look at the system behavior) or to stimulate the chips with synthetic trains of spikes.

More general architectures have been proposed [34, 37, 106] to interconnect, monitor and stimulate several AER devices. The first example of a general–purpose multi–sender multi–receiver communication framework for AER devices, called *Silicon Cortex* (SCX), is the one proposed in 1998 by Deiss et al. [37]. SCX is a fully–arbitrated AE infrastructure which can support up to six AER chips; larger systems can be assembled by linking together multiple boards. SCX provides a method of building a distributed network of local busses sufficient to build an indefinitely large system, co–ordinating the activity of multiple sender/receiver chips on a common bus. The user can configure arbitrary connections between neurons, set analog parameters and monitor the activity of the neurons.

The most recent communication frameworks [34, 106] follow two different strategies.

<sup>&</sup>lt;sup>1</sup>The merge circuit combines the address events at its input with address events generated by the neuron array and sends them off chip via a transmitter. The split circuit makes two copies of the AER events appearing at its input.

In the context of the CAVIAR project<sup>2</sup>, Serrano–Gotarredona et al. [106] proposed a distributed system in which a USB–AER board can be programmed to perform one of five different functions: (1) mapping of addresses, (2) capture of timestamped AEs, (3) reproduction of time–stamped sequences of AEs in real time, (4) transformation of sequence of frames into AEs in real time, (5) histogram AEs into sequences of frames in real time. Additional PCBs are used to record AE traffic on the AER bus; split one AER bus into 2, 3 or 4 busses; merge 2, 3 or 4 AER busses into a single bus; and capture time–stamped AEs to a computer.

The hardware infrastructure described in this chapter, originally conceived and built by Vittorio Dante in Rome at the Physics Laboratory of the Italian Institute of Health [34], follows a different approach. It consists of a single full–custom general–purpose PCI board (the PCI–AER board) hosted in a workstation, that allows connection of up to four sender and four receiver chips, building a multi–chip system with arbitrary intra– and inter–chip connectivity, stimulating receiver chips with synthetic trains of spikes, monitoring and log-ging the activity of the sender devices. AER systems built using the PCI–AER board require a workstation in the loop and therefore are not as portable as the CAVIAR system, nevertheless these systems are more convenient for rapid prototyping tests, data analysis, and on–line reconfigurability.

This board and its supporting software are the unique result of a team effort of several researchers from different institutions over several years. The Linux driver for the PCI–AER board was written by Adrian Whatley at INI. I contributed by writing library and test code for using the board, by debugging the setup, and by acting as the first beta–tester with a VLSI AER multi–neuron chip (described in chapter 5).

### 2.5 The PCI–AER Hardware Infrastructure

#### 2.5.1 The PCI–AER Board

The need for a custom device to easily interact with neuromorphic chips with spiking neural networks quickly increased with the emergence of the AER protocol as a standard for communication between these chips. In 2000, at the Physics Laboratory of the Italian Institute of Health (Rome, Italy) the PCI–AER project was started to provide flexible and easy interaction between a standard personal computer and an interconnected system of possibly heterogeneous AER chips. The PCI–AER board provides real–time routing between neuromorphic chips, with programmable connectivity, monitoring and stimulation of up to four chips and a communication bridge between AER and the PCI bus. The PCI-AER board takes the form of a 33MHz, 32-bit, 5V PCI bus add-in card (see Fig. 2.5) installed in a host personal computer. A 68-way cable is used to connect the PCI–AER board to a small header board (see Fig. 2.6) which can be conveniently located on the benchtop, and provides connectors for up to four AER receivers and four AER senders. The header board also electrically buffers the signals to and from the receivers and senders. Senders must use

<sup>&</sup>lt;sup>2</sup>CAVIAR is the acronym of the European funded project IST–2001–34124: Convolution AER Vision Architecture for Real Time.

**Figure 2.5:** PCI–AER board. The devices involved in the implementation of the three major functional blocks (see Fig. 2.7) are highlighted: MONITOR, MAPPER, and SEQUENCER FIFOs, FPGA1, and FPGA2. The SRAM is used to hold the mapper's look-up table. A 68 pin cable connector is used to connect to the header board (see Fig. 2.6). The PCI interface manages the communication with the host personal computer through the PCI bus.

**Figure 2.6:** PCI–AER header board. The header board is connected to the PCI–AER board through a 68-way cable and it can be conveniently located on the benchtop. The header board provides connectors for up to four AER receivers and four AER senders plus the SEQUENCER connector. The external board has five LEDs, three yellow and four red. Close to the 68 pin connector there is the Power ON LED. Next to it there are FIFO Full alert LEDs for the MAPPER, MONITOR and SEQUENCER respectively. The yellow LEDs are used to indicate the status (LED on means enabled) of the three functional blocks (SEQUENCER, MONITOR, and MAPPER respectively).

the SCX multi-sender AER protocol [36], in which request and acknowledge signals are active low, and the bus may only be driven while the acknowledge signal is active. Receivers may use either this SCX protocol, or they may choose to use a P2P protocol [1] in which request and acknowledge are active high and the bus is driven while request is active. Which protocol is generated by the board may be selected under software control.

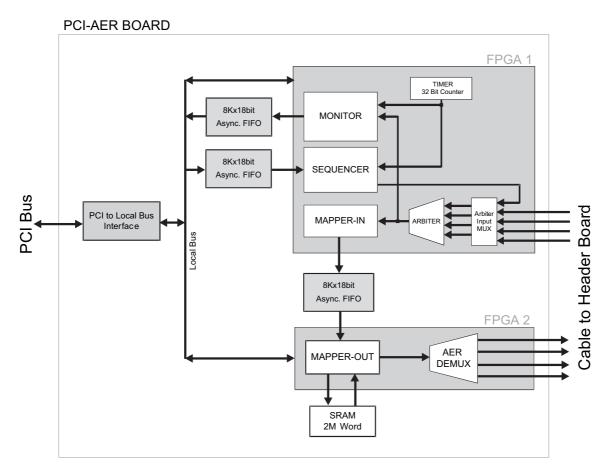

As illustrated in Fig. 2.7, the PCIAER board can perform three functions which are executed by blocks we refer to as the monitor, sequencer, and mapper. These blocks are controlled by two FPGAs (FPGA1 and FPGA2 in Fig. 2.5) on the board.

The PCI-AER board has four main components:

- **Arbiter** Up to four sender chips can be connected to the PCI–AER board. The on board arbiter implements arbitration of events generated by the different sender chips. This allows multiple sender devices to access the AE bus.

- **Monitor** Arbitrated events generated by the sender chips are time-stamped and recorded by the monitor. Stored events can be then accessed from the personal computer via the PCI bus. This is useful for logging data, and it allows the user to analyze the activity of the connected devices off-line, without affecting the performance of the system.

- **Sequencer** Using the sequencer, up to four receiver chips can be stimulated with predefined spike trains. Synthetic spike trains can be generated using the personal computer and downloaded to the board via the PCI bus.

- **Mapper** The connectivity pattern between up to four sender chips and up to four receiver chips is implemented by the mapper. Transceiver chips can be connected as sender

**Figure 2.7:** Block diagram of the PCI–AER interface board showing its three major functional blocks, i.e. the MONITOR, the SEQUENCER, and the MAPPER (divided into MAPPER–IN and MAPPER–OUT). These (and other blocks) are implemented in two FPGAs on the PCI–AER board. Also shown are the FIFOs, the interface to the PCI bus, the SRAM used to hold the mapper's look– up table, the cable buffers, and the interconnecting buses.

and receiver at the same time, using the PCI–AER to externally configure their "internal" connectivity. Arbitrary network topologies can therefore be implemented and reprogrammed on–line.

Using these components the board implements the functions described below.

#### Monitoring

The PCI–AER board can monitor the spiking activity of up to four sender chips. The monitor captures and timestamps events coming from the attached AER senders via an arbiter, and makes those events available to the personal computer for further processing. A timer is implemented in one of the FPGAs, and when an incoming address–event is read, a timestamp is stored along with the address in an 8KWord First–In First–Out (FIFO) memory. This FIFO decouples the management of the incoming address–events from read operations on the PCI bus, the bandwidth of which must be shared with other peripherals in the personal computer such as the network card. Interrupts to the host personal computer can be generated when the FIFO becomes half–full and/or full, and in the ideal case, the driver will read time stamped address–events from the monitor FIFO whenever the host

CPU receives a FIFO half-full interrupt at a rate sufficient that the FIFO never fills or overruns, given the rate of incoming address-events. Each event is stored in the form of three successive 18 bits words. The two most significant bits of the word encode the type of information stored in the other 16 bits. A word can contain four different type of information: AE, Time High (16 most significant bits of the 32 bits word encoding the time-stamp), Time Low (16 less significant bits of the 32 bits word encoding the time-stamp), Error or Control code. The time resolution can be set to four different values: 1, 10, 50 or 100  $\mu$ s. The AE is coded differently depending on the number of sender chips:

- 1 sender chip 16 bit address word.

- **2 sender chips** The most significant bit of the AER address encodes the chip label. The address word is encoded by the remaining 15 less significant bits.

- **4 sender chips** The two most significant bits of the AER address encode the chip label. The address word is encoded by the remaining 14 less significant bits.

#### Stimulating

The PCI–AER board can be used to stimulate receiver chips using synthetic trains of AEs. This function is implemented by the sequencer. These events may for example represent a pre–computed buffered stimulus pattern, but they might also be the result of a real time computation. This allows, for instance, software simulations of VLSI devices to provide input to real VLSI hardware while the former VLSI devices are still under development. As soon as the real device is available, the software simulation can be seamlessly replaced. Like the monitor, the sequencer is decoupled from the PCI bus using an 8KWord FIFO. The host writes an interleaved sequence of words representing addresses and time delays to the sequencer FIFO. The sequencer then reads these words one at a time from the FIFO and either emits an address–event or waits the indicated number of microseconds. The events generated can be transmitted on any of the four output channels.

#### Mapping

Events coming from sender chips can be mapped to receiver chips using the PCI–AER board. The use of a transceiver chip combined with this function allows programmable connectivity between neurons on the same chip. Different chips can also be interfaced by defining a connection table among their neurons. The mapper can operate in three different modes:

Pass-through The input address events are simply replicated on the output.

**One-to-one** The input address events are used as pointers to a look-up table stored in the mapper SRAM. The retrieved content of the table for each input address is the target address on the output.

**One-to-many** Each input address event generate multiple output events to different targets. The input address is used as a pointer to the first memory location (in the mapper SRAM) of a list of targets.

The mapper has a FIFO which decouples the asynchronous reception of the incoming address events from the generation of outgoing address events. Once configured and after the look–up table has been filled with the required mappings, the mapper operates entirely independent of the host personal computer. All of the necessary operations, including table look–up, are performed by one of the FPGAs on the PCI–AER board.

#### 2.5.2 Supporting Software

Low level control of the PCI–AER board is carried out by a Linux software driver which allows the operating system to access and modify the status of the board. The driver supports up to four PCI–AER boards in one machine. The logically separate functions of the Mapper, Monitor and Sequencer are supported by three minor devices for each board. The separation of Mapper, Monitor, and Sequencer has the advantage of giving the desired degree of granularity of control over simultaneous use policy (not more than one process may open each minor device, but separate processes may be used for reading, writing and mapping control). The Linux driver for the PCI–AER board was developed by Adrian M. Whatley at the Institute of Neuroinformatics (University and ETH Zurich).

A user of the hardware infrastructure should not need to understand and use the driver interface to be able to test neuromorphic chips. Instead of accessing a particular configuration register to set the appropriate value for using a defined functionality of the board, the user should be able to simply use the desired functionality through more high level software functions. For this purpose a library of C functions was implemented.

The PCI–AER library is a set of low/intermediate level functions useful for accessing and controlling the PCI–AER board. They can be used in spike train generation code, in data–logging code and in other programs that need to access the PCIAER board. Specifically, library calls allow the user to easily perform all operations supported by the PCI–AER board and driver. For example, the following sequence of operations can be executed to read and store the activity of all senders connected to the PCI–AER board:

- 1. Open Monitor.

- 2. Read n AEs (where n is an arbitrary number).

- 3. Close Monitor.

These high level commands open the driver and call a set of low level routines to perform the required operation. Many other high level commands are included in the library and App. B contains a detailed description of all library calls. I initially developed most of these commands under the supervision of Adrian Whatley and participated in the debugging of the library. The code has been further debugged and enhanced by Adrian Whatley and other collegues.

All the software is implemented in C language and can be easily used with a Matlab interface to develop an user-friendly access system to the chips through the PCI-AER board.

# **Chapter 3**

# Analog Circuits for Implementing Spike Based Processing Models

Neuromorphic engineering makes use of analog very–large–scale–integrated (VLSI) circuits to implement biologically–inspired processing systems. Analog circuits perform massively parallel real–time computation with many orders of magnitude less power than general–purpose computers.

In this Chapter, I will introduce some basic analog circuits necessary for understanding the neuromorphic circuits I used as building blocks in my system. I start with a quick review of the *Metal–Oxide–Semiconductor Field Effect Transistor* (MOSFET) device [81, 88], move on to two transistor circuits that are basic blocks for the silicon synapses, describe the transconductance amplifier used in the silicon neuron, the neuron circuit itself and an adaptive synapse circuit, able to model short–term depression and facilitation effects. Since almost all the neuromorphic circuits I used in my system are operated in the subthreshold regime, in the next section I will discuss the MOSFET device and the analog circuits always referring to this regime.

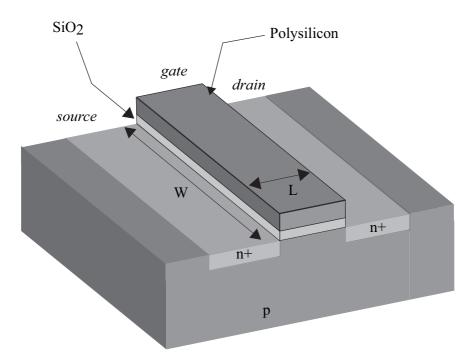

### 3.1 Subthreshold MOSFET Characteristic

The MOSFET is composed of a *Metal–Oxide–Semiconductor* (MOS) structure (*gate*) and two diffusions (*drain* and *source*). A schematic drawing of the structure of an *n*-type MOS transistor is shown in Fig. 3.1. The *substrate* is *p*-type (holes are the majority carriers). The *drain* and *source* diffusions are heavily doped *n*-type (electrons are the majority carriers). The *channel* is the region underneath the *gate* and between the *drain* and *source* diffusions. The charge in the channel is carried by electrons. The *p*-type MOS has an *n*-type channel where the charge is carried by holes supplied from the *p*-type source and drain regions.

**Figure 3.1:** Schematic drawing of the physical structure of an *n*-type MOS transistor. Two *n*+ diffusions in the *p* substrate implement the *drain* and *source* regions. The *gate* is implemented by a polysilicon layer isolated from the channel by a SiO<sub>2</sub> layer.

In a CMOS process, the *n*-FETs and *p*-FETs are fabricated on the same substrate. In the process I used, *n*-FETs are implemented in the common  $p^-$  substrate and *p*-FETs in an *n*-well within the substrate.

The MOS transistor has four terminals (MOSFET symbols for both n and p-type transistors are shown in Fig. 3.2): the source (S), the drain (D), the gate (G) and the bulk (B).

The expression for the current that flows between drain and source is

$$I_{ds} = I_0 e^{\frac{qV_g}{KT}} \left( e^{-\frac{qV_s}{KT}} - e^{-\frac{qV_d}{KT}} \right)$$

(3.1)

where

$$I_0 = q D N_0 e^{-q \frac{\Phi_0}{KT}} \frac{W}{L}$$

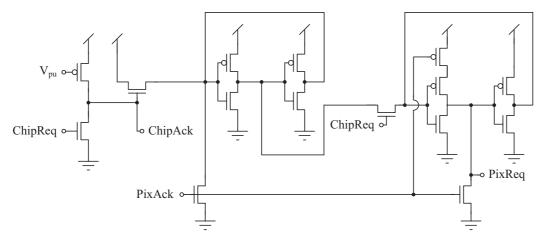

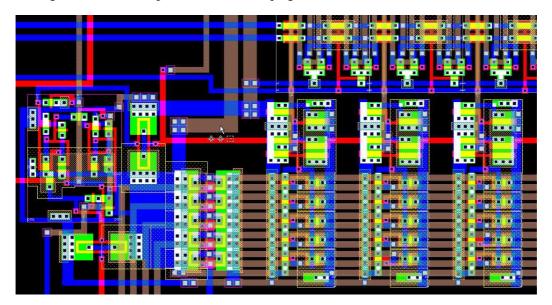

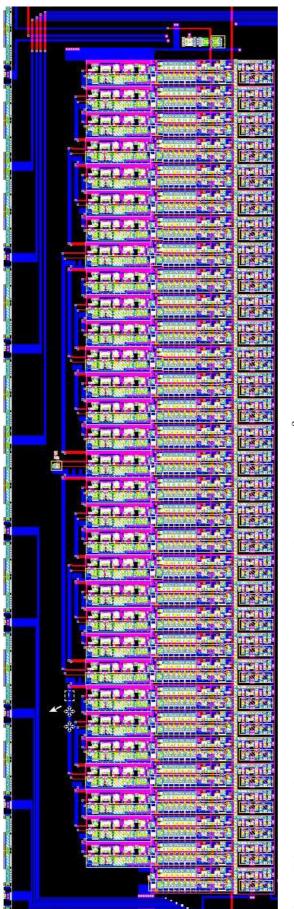

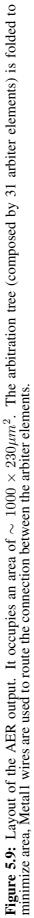

is the *dark* or *leak* current. In the derivation of the  $I_{ds}$  current, the Early effect and the fact that only part of the voltage applied to the gate is present on the channel are neglected [81]. Taking into account these two effects and using  $V_{ds}$  for  $V_d - V_s$ , we can write: