# DISS. ETH NO. 26410

# DATA MOVEMENT OPTIMIZATION FOR HIGH-PERFORMANCE COMPUTING

A dissertation submitted to attain the degree of DOCTOR OF SCIENCES of ETH ZURICH (Dr. sc. ETH Zurich)

presented by

TOBIAS GYSI Dipl. Informatik-Ing. ETH ETH Zurich

born on the 7th of July 1980 citizen of Buchs AG, Switzerland

accepted on the recommendation of

Prof. Dr. Torsten Hoefler, examiner Prof. Dr. Thomas C. Schulthess, co-examiner Dr. Albert Cohen, co-examiner

Tuning codes to make efficient use of high-performance computing systems is known to be hard. Programmers have to schedule their computations to thousands of compute cores having the compute and data movement costs in mind. The necessary code transformations – for example, to overlap computation and inter-node communication – are well known. But the complex interplay of hardware and software often prevents programmers from identifying performance bottlenecks and selecting good code transformations. This dissertation introduces compilation frameworks, performance tools, and programming models to tackle these programmability challenges.

Over the last decades, the compute performance improved at a much faster pace than memory performance. Data-movement optimizations to reduce the communication and memory access costs thus became much more pressing. We address the problem by automating the selection of data-locality transformations (ABSINTHE) and by adapting the programming model (DCUDA) to overlap computation and inter-node communication automatically. The performance models needed to automate the tuning (ABSINTHE and HAYSTACK) also provide the programmers with valuable insights when optimizing codes manually.

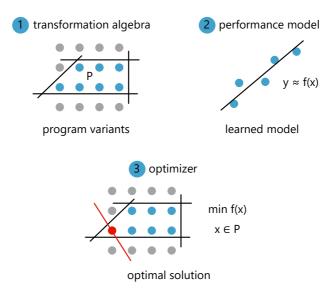

An important algorithmic motif in high-performance computing is the sequential execution of multiple but different stencils. Our compilation framework (ABSINTHE) automates the selection of data-locality transformations for such stencil programs. It has three main components: 1) a transformation algebra, 2) a performance model, and 3) an optimizer. The transformation algebra (MODESTO) defines the space of possible code transformations and the learned performance model (ABSINTHE) guides the selection of good code transformations.

In summary, this dissertation contributes compilation frameworks, performance tools, and programming models to foster the application of data movement optimizations in high-performance computing. In particular, we automate the selection of data-locality transformations for stencil programs. We believe our work lays the foundation for future compilation frameworks that support even broader application domains.

Es ist bekannt, dass die Optimierung von Codes zur effizienten Nutzung von Hochleistungsrechnern schwierig ist. Programmierer müssen, unter Berücksichtigung von Rechenaufwand und Datenübertragungskosten, ihre Berechnungen auf Tausende von Rechenkernen verteilen. Die notwendigen Code-Transformationen – zum Beispiel zur Überlappung der Kommunikation zwischen den Rechenknoten mit den Berechnungen – sind allgemein bekannt. Das komplexe Zusammenspiel von Hardware und Software hindert Programmierer jedoch häufig daran, Performance-Probleme zu identifizieren und gute Code-Transformationen auszuwählen. In dieser Dissertation werden Kompilierungs-Frameworks, Performance-Tools und Programmiermodelle vorgestellt, um die Programmierbarkeit von Hochleistungsrechnern zu verbessern.

In den letzten Jahrzehnten hat sich die Rechenleistung deutlich schneller verbessert als die Speicherleistung. Optimierungen zur Reduzierung der Kommunikations- und Speicherzugriffskosten wurden daher dringlicher. Wir gehen das Problem an, indem wir die Auswahl von Transformationen zur Verbesserung der Datenlokalität automatisieren (ABSINTHE) und das Programmiermodell anpassen (DCUDA), um die Kommunikation zwischen den Rechenknoten automatisch mit den Berechnungen zu überlappen. Die zur Automatisierung erforderlichen Performance-Modelle (ABSINTHE und HAYSTACK) bieten den Programmierern zudem wertvolle Einblicke bei der manuellen Code Optimierung.

Ein wichtiges algorithmisches Motiv im Hochleistungsrechnen ist die sequentielle Ausführung mehrerer, aber unterschiedlicher Stencil Berechnungen. Unser Kompilierungs-Framework (ABSINTHE) automatisiert die Auswahl von Code-Transformationen zur Verbesserung der Datenlokalität von Stencil Programmen. Es besteht aus drei Hauptkomponenten: 1) einer Transformations-Algebra, 2) einem Performance-Modell und 3) einem Optimierer. Die Transformations-Algebra (MODESTO) definiert den Raum möglicher Code-Transformationen und das erlernte Performance-Modell (ABSINTHE) steuert die Auswahl guter Code-Transformationen.

Zusammenfassend leistet diese Dissertation einen Beitrag zur Entwicklung von Kompilierungs-Frameworks, Performance-Tools und Programmiermodellen, um die Anwendung von Datenlokalitätsoptimierungen im Hochleistungsrechnen zu fördern. Insbesondere automatisieren wir die

Optimierung von Stencil Programmen. Wir glauben, dass unsere Arbeit den Grundstein für zukünftige Kompilierungs-Frameworks legt, die noch breitere Anwendungsbereiche unterstützen.

#### ACKNOWLEDGEMENTS

I want to thank Torsten Hoefler for supervising my Ph.D. studies here at ETH Zurich. His scientific guidance was essential to address the right research questions and helped to widen the scope of my work. I am also grateful to Torsten Hoefler and Thomas Schulthess for providing me with the opportunity to return to academia after spending multiple years in the industry. I furthermore want to thank my co-examiners, Albert Cohen and Thomas Schulthess, for their effort and their valuable feedback. Special thanks go to Tobias Grosser who was co-supervising my Ph.D. studies and contributed key ideas to my research.

I value the contributions of all my co-authors, collaborators, and students. I especially enjoyed working with Tobias Grosser, Jeremia Bär, Laurin Brandner, Grzegorz Kwasniewski, Aditya Konduri, Siddharth Bhat, and Alain Denzler on published and yet to be published works. The contributions of my co-authors were essential for the success of my projects.

I also want to thank the entire group for the fun birthday parties at the lake and many other memorable moments. Last but not least, I want to thank my family for their support and my dance friends for many good moments and great dances that were a welcome change to my research work.

### **PUBLICATIONS**

Publications that form the basis of this thesis:

- Tobias Gysi, Tobias Grosser, and Torsten Hoefler.

"MODESTO: Data-centric Analytic Optimization of Complex Stencil Programs on Heterogeneous Architectures."

ICS 2015. [1].

- Tobias Gysi, Tobias Grosser, and Torsten Hoefler.

"Absinthe: Learning an Analytical Performance Model to Fuse and Tile Stencil Codes in One Shot."

PACT 2019. [2].

- Tobias Gysi, Tobias Grosser, Laurin Brandner, and Torsten Hoefler.

"A Fast Analytical Model of Fully Associative Caches."

PLDI 2019. [3].

- Tobias Gysi, Jeremia Bär, and Torsten Hoefler.

"dCUDA: Hardware Supported Overlap of Computation and Communication."

SC 2016. [4].

Additional publications not part of this thesis:

- Tobias Gysi, Carlos Osuna, Oliver Fuhrer, Mauro Bianco, and Thomas C. Schulthess.

- "STELLA: A Domain-specific Tool for Structured Grid Methods in Weather and Climate Models." SC 2015. [5].

- Oliver Fuhrer, Carlos Osuna, Xavier Lapillonne, Tobias Gysi, Ben Cumming, Mauro Bianco, Andrea Arteaga, and Thomas C. Schulthess.

"Towards a Performance Portable, Architecture Agnostic Implementation Strategy for Weather and Climate Models."

Supercomputing Frontiers and Innovations. April 2014. [6].

# CONTENTS

| - | TATE | DODIIG                                   | TION 1                             |  |  |  |  |

|---|------|------------------------------------------|------------------------------------|--|--|--|--|

| 1 |      | RODUC                                    |                                    |  |  |  |  |

|   | 1.1  | Automatic Data-Locality Optimization 2   |                                    |  |  |  |  |

|   | 1.2  | User-Guided Data Movement Optimization 4 |                                    |  |  |  |  |

|   |      | _                                        | ortance of the Programming Model 7 |  |  |  |  |

|   | 1.4  | Thesis                                   | Contributions 7                    |  |  |  |  |

| 2 | A ST | A STENCIL ALGEBRA 9                      |                                    |  |  |  |  |

|   | 2.1  | Stencil                                  | l Algebra 10                       |  |  |  |  |

|   |      | 2.1.1                                    | Definition of a Stencil Program 10 |  |  |  |  |

|   |      | 2.1.2                                    | Example 11                         |  |  |  |  |

|   |      | 2.1.3                                    | Data Locality Transformations 13   |  |  |  |  |

|   |      | 2.1.4                                    | Stencil Algebra Definition 15      |  |  |  |  |

|   |      | 2.1.5                                    | Performance Modeling 17            |  |  |  |  |

|   |      | 2.1.6                                    | Stencil Program Analysis 19        |  |  |  |  |

|   | 2.2  | Case S                                   | Study 28                           |  |  |  |  |

|   |      | 2.2.1                                    | STELLA 28                          |  |  |  |  |

|   |      | 2.2.2                                    | Stencil Program Optimization 30    |  |  |  |  |

|   | 2.3  | Evalua                                   | ation 31                           |  |  |  |  |

|   | 2.4  | Relate                                   | d Work 34                          |  |  |  |  |

|   | 2.5  | Summ                                     | ary of the Approach 35             |  |  |  |  |

| 3 | A LI | EARNEI                                   | D PERFORMANCE MODEL 37             |  |  |  |  |

|   | 3.1  | Background 39                            |                                    |  |  |  |  |

|   |      | 3.1.1                                    | Architecture Overview 39           |  |  |  |  |

|   |      | 3.1.2                                    | Stencil Sequences 40               |  |  |  |  |

|   |      |                                          | Data-Locality Transformations 40   |  |  |  |  |

|   | 3.2  | Model                                    | ling 41                            |  |  |  |  |

|   |      | 3.2.1                                    | Stencil Sequences 43               |  |  |  |  |

|   |      | 3.2.2                                    | Data-Locality Transformations 44   |  |  |  |  |

|   |      |                                          | Performance Model 45               |  |  |  |  |

|   |      | 3.2.4                                    | Learning the Performance Model 49  |  |  |  |  |

|   | 3.3  |                                          | ization 51                         |  |  |  |  |

|   |      | 3.3.1                                    | Linearizing Multiplications 51     |  |  |  |  |

|   |      | 3.3.2                                    | Modeling Stencil Groups 52         |  |  |  |  |

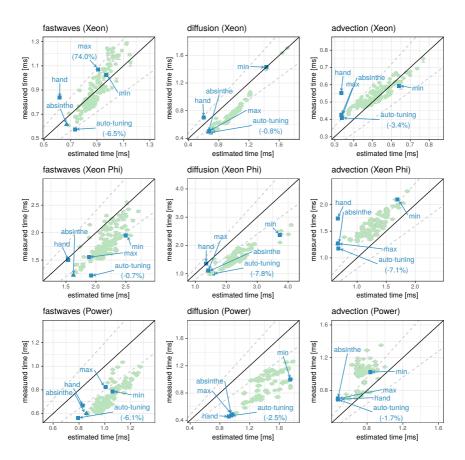

|   | 3.4  | Evalua                                   |                                    |  |  |  |  |

|   | - •  |                                          | Setup & Methodology 53             |  |  |  |  |

|   |      |                                          | Implementation 55                  |  |  |  |  |

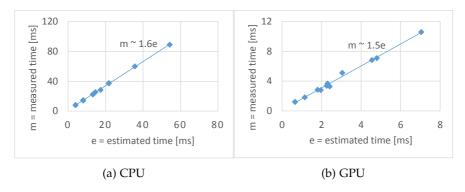

|   |     | 3.4.3  | Learning the Target Systems 55         |

|---|-----|--------|----------------------------------------|

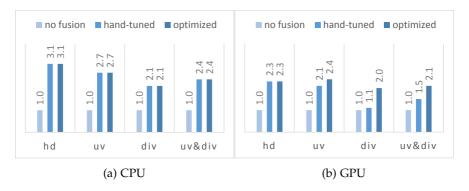

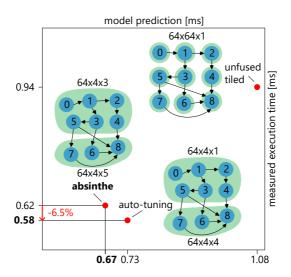

|   |     | 3.4.4  | Tuning the Application Kernels 58      |

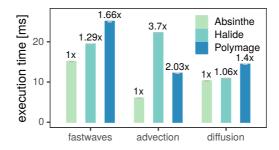

|   |     | 3.4.5  | Comparison with Halide and Polymage 61 |

|   | 3.5 | Relate | ed Work 62                             |

|   | 3.6 | Sumn   | nary of the Approach 63                |

| 4 | AN  | ANALY  | TICAL CACHE MODEL 65                   |

|   | 4.1 | Backg  | round 67                               |

|   |     | 4.1.1  | Hardware Model 67                      |

|   |     | •      | Cache Misses 67                        |

|   |     |        | Integer Sets and Maps 68               |

|   |     | 4.1.4  | Static Control Programs 69             |

|   | 4.2 |        | Model 70                               |

|   |     | 4.2.1  | Computing the Stack Distance 71        |

|   |     | 4.2.2  | 0 1 ,                                  |

|   |     | 4.2.3  |                                        |

|   |     | 4.2.4  |                                        |

|   |     | 4.2.5  | 1 1                                    |

|   | 4.3 | Evalu  |                                        |

|   |     | 4.3.1  | Setup and Methodology 84               |

|   |     | 4.3.2  |                                        |

|   |     | 4.3.3  | Performance Overview 87                |

|   |     | 4.3.4  | Comparison to PolyCache and Dinero 92  |

|   |     | 4.3.5  | Performance for Tiled Codes 92         |

|   | 4.4 |        | ed Work 93                             |

|   | 4.5 |        | nary of the Approach 95                |

| 5 | A C |        | NICATION-HIDING PROGRAMMING MODEL 9    |

|   | 5.1 | _      | amming Model 98                        |

|   |     | 5.1.1  | Distributed Memory 99                  |

|   |     | 5.1.2  |                                        |

|   |     | 5.1.3  |                                        |

|   |     | 5.1.4  | · · · · · · · · · · · · · · · · · · ·  |

|   | 5.2 |        | mentation 105                          |

|   |     | -      | Architecture Overview 105              |

|   |     | _      | Communication Control 107              |

|   |     | 5.2.3  |                                        |

|   |     | 5.2.4  | Discussion 110                         |

|   | 5.3 | Evalu  |                                        |

|   |     | 5.3.1  | Experimental Setup & Methodology 111   |

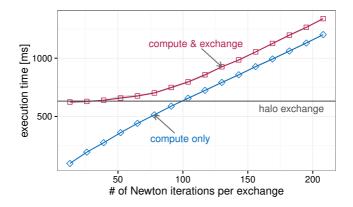

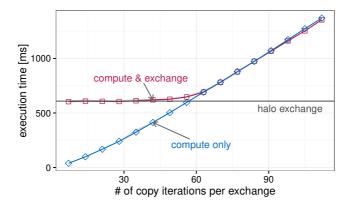

|   |     | 5.3.2  | Microbenchmarks 112                    |

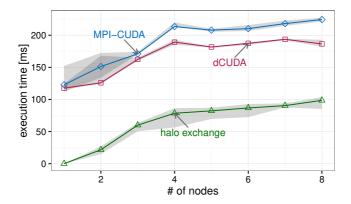

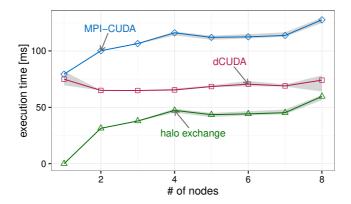

|   |      | 5.3.3 Mini-applications 114                  |

|---|------|----------------------------------------------|

|   | 5.4  | Discussion 119                               |

|   | 5.5  | Related Work 120                             |

|   | 5.6  | Summary of the Approach 121                  |

| 6 | CON  | ICLUSIONS AND FUTURE WORK 123                |

|   | 6.1  | Future Work 123                              |

|   |      | 6.1.1 Automatic Performance Model Design 124 |

|   |      | 6.1.2 Scaling to Real-World Applications 125 |

|   |      | 6.1.3 Cache Optimal Programs 125             |

|   |      |                                              |

|   | віві | LIOGRAPHY 127                                |

#### INTRODUCTION

Over time the cost of data movement steadily gained importance and started to dominate the overall computational cost – both in terms of execution time and energy consumption. Analyzing and reducing the cost of data movement became an important concern in high-performance computing [7]. But applying data movement optimizations [8–10] increases the code complexity and often requires non-trivial parameterization. Domain-specific tools [5, 11–13] or compilers [14, 15] may hide the increased code complexity, but choosing optimal parameters remains hard. Examples for the necessary parameterization are tile size and fusion choices or the ratio of the inner to the outer domain when overlapping computation and inter-node communication.

The hardware landscape in high-performance at the same time got much more diverse. Heterogeneous systems equipped with accelerators more and more supersede the previously dominating multi-core machines. The resulting diversity complicates the development of single source code that performs well on today's and tomorrow's systems. Especially since datalocality transformations are very much system-specific. As a result, the model of having expert programmers that in a heroic effort tune the codes for every new hardware generation does not scale anymore.

In this thesis, we use the COSMO atmospheric model [16] as our primary motivational example. The code is used for operational weather forecasting [17] and climate modeling [18]. COSMO consists of more than 300,000 lines of code that mostly implement stencil computations (finite-differences). Its low arithmetic intensity in combination with the sheer size makes the real-world application a good testbed for data-locality transformations.

The current version of COSMO already targets both CPU and GPU systems [6] using a single source code. To this end, the dynamical core of COSMO was rewritten in the domain-specific language STELLA [5] that implements target specific data-locality transformations for both CPU and GPU. STELLA automates the code generation but still requires manual interventions to select the tile sizes and to fuse stencils. The goal of this thesis is to enable the development of domain-specific languages that provide true performance portability by automatically selecting good data-locality transformations.

1

Auto-tuning is the swiss-army knife for the selection and parameterization of good code transformations. It relies on the empiric evaluation of different implementation variants to select good code transformations. Existing auto-tuning frameworks [19–22] implement ready-to-use search strategies that enable the efficient search space exploration. Yet, compiling and running different implementation variants requires target system access during compilation and can become prohibitively expensive depending on the size of the search space.

An alternative are optimization frameworks [13, 23–25] relying on heuristics and analytical models. In this thesis, we focus on the development of analytical performance models and optimization strategies for selecting data-locality transformations. We show that analytical performance models enable the fast search space exploration while being accurate enough to guide the optimization. Model-based optimization is a promising approach that in many cases provides a good set of initial transformations that if required may be further refined using auto-tuning.

#### 1.1 AUTOMATIC DATA-LOCALITY OPTIMIZATION

All programming models and domain-specific languages that aim at performance portability have to apply target system-specific code transformations. Loop fusion and tiling [8, 26, 27] are examples of important data-locality transformations in high-performance computing. The fusion space alone is exponential in the number of loop nests, and for every fused loop nest, a range of possible tile sizes exists. The large search space and the interdependence of the parameter choices – fusion and tile size need to be considered in tandem – make the optimization challenging.

An automatic optimization framework has to formalize the space of possible code transformations and select the most beneficial ones. Several approaches to describe the search space for polyhedral programs [28–30], high-level programs written using algorithmic skeletons [31], and domain-specific programs [12, 32, 33] exist. Possible techniques to select code transformations are heuristics [34], performance models [24, 35], and empiric evaluation [19, 20]. We focus on the performance model guided selection of data-locality transformations. The mathematical structure and the fast evaluation of a well-designed performance model can considerably accelerate the search space exploration compared to empirical tuning. A downside of the model-based approach is the limited model accuracy that prevents us from guaranteeing optimality for the selected code transformations.

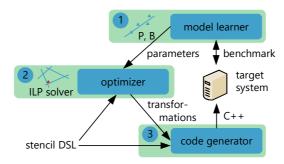

Figure 1.1: An optimization problem that implements transformation algebra and performance model enables the automatic selection of data-locality transformations.

Data-locality transformations adapt the program schedule to improve the spatial and temporal locality of the computation. After the optimization computations that access the same data are ideally scheduled to the same compute core and the shared data is stored in cache or registers. At the same time, increasing data-locality often reduces the available parallelism. We thus need to balance data-locality and parallelism [36, 37] while scheduling the computations.

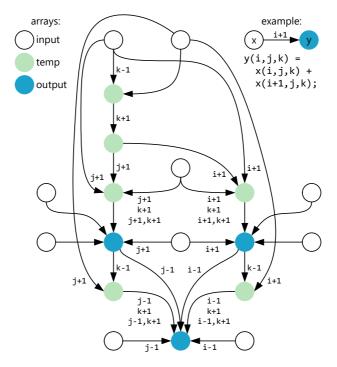

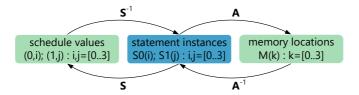

Figure 1.1 shows the main components of a typical automatic optimization framework: 1) an algebra that defines the space of possible code transformations, 2) a performance model to evaluate the effects of the selected code transformations, and 3) an optimizer to explore the search space. All components need to interface with the code generation to automate the optimization process.

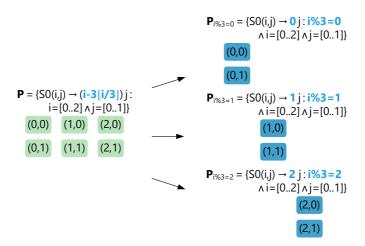

TRANSFORMATION ALGEBRA The core of every automatic optimization framework is a transformation algebra that formalizes the space of possible code transformations. We defined the stencil algebra MODESTO to enumerate the space of possible data-locality transformations for stencil

programs. The algebra specifies the execution order and the fusion and tile size choices for all stencils of the program. Every element of the algebra represents a program variant that performs the same computation but has different performance characteristics.

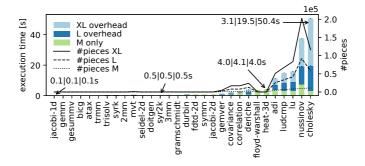

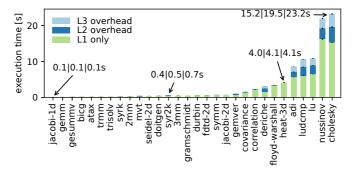

PERFORMANCE MODEL The performance model estimates the cost of the different program variants. We developed the stencil program optimizer ABSINTHE and the analytical cache model HAYSTACK. Both of them can be used to select code transformations. ABSINTHE models the latency and throughput of the stencil loop nests. The simple linear model enables the efficient program optimization using linear integer programming. HAYSTACK models fully associative caches with a least recently used replacement policy. The model is more complex but can compute the cache misses for arbitrary polyhedral programs.

OPTIMIZER An automatic optimization framework searches the program variant that minimizes the cost, for example, by integrating the transformation algebra and the performance model into a single optimization problem. Absinthe uses linear integer programming to select optimal code transformations with respect to the performance model. We thereby rely on an existing state-of-the-art solver [38] that is guaranteed to find the optimal solution.

In general, data-locality transformations such as tiling and fusion are interdependent. For example, the optimal tile size of a fused loop nest typically decreases due to the larger memory footprint after fusion. The optimization problem formulated by ABSINTHE performs single shot fusion and tile size choices to account for the interdependence of the different data-locality transformations. The simplicity of both transformation algebra and performance model additionally enables the formulation of a linear optimization problem that can be solved efficiently. We thus believe the development of an automatic optimization framework requires a holistic view of transformation algebra, performance model, and optimization method.

#### 1.2 USER-GUIDED DATA MOVEMENT OPTIMIZATION

Automatic tuning is only available for some application domains, and the results may be suboptimal. In these cases, programmers have to fall back to manual optimization. But the large space of possible data-locality

```

gysit@tobias-pc: ~/Repos/haystack/examples

File Edit View Search Terminal Help

gysit@tobias-pc:~/Repos/haystack/examples$ haystack -f gemm.c

> setting up cache levels

- 32kB with 64B cache lines

- 512kB with 64B cache lines

-> done

-> start processing...

-> done after (114.90ms)

______

relative number of cache misses (statement)

_______

8 #pragma scop

for (int i = 0; i < D; i++) {

10

for (int j = 0; j < D; j++)

C[i][j] *= beta;</pre>

11

ref type comp[%] L1[%]

L2[%] tot[%] reuse[ln]

C[i][j] rd

C[i][j] wr

0.00153 0.00000 0.00000 0.02440

0.00000 0.00000 0.00000 0.02440

for (int k = 0; k < D; k++)

12

13

for (int j = 0; j < D; j++)

14

C[i][j] += alpha * A[i][k] * B[k][j];

L2[%]

гef

type comp[%]

L1[%]

tot[%]

reuse[ln]

C[i][j] rd

A[i][k] rd

24.98780 11,14

24.98780 14

гd

0.00000

0.00000

0.00000

0.00153

0.00000

0.00000

B[k][j] rd

0.00153

1.56021

1.56021

24.98780 14

C[i][j] wr

0.00000

0.00000

0.00000

24.98780 14

15

16 #pragma endscop

-----

absolute number of cache misses (SCOP)

_______

compulsory:

196'608

67'043'328

67'043'328

capacity (L1):

capacity (L2):

4'297'064'448

total:

gysit@tobias-pc:~/Repos/haystack/examples$

```

FIGURE 1.2: Screenshot of HAYSTACK analyzing matrix multiplication.

transformations and the complexity and heterogeneity of the available hardware architectures make the manual tuning challenging. Tools that help programmers to identify performance bottlenecks and to evaluate the effectiveness of their code transformations are thus an important concern.

Almost all modern processors rely on caches to reduce data movement and to hide memory access latencies. Caches not only improve performance but unfortunately also make understanding the memory access cost hard. Hence, programmers need to know the state of the cache to estimate the memory access cost. As a result, the cost of data movement depends on global state and does not compose.

The state of the cache depends on the exact memory access history. Minor changes of the memory access history can have significant effects on the cache efficiency. Let us assume a least recently used replacement policy. If a program implements two identical loop nests that access an array with the size of the cache, then all access of the second loop nest are cache hits. But if the program performs an additional memory access between the two loop nests, then all memory accesses of the second loop nest are cache misses. This example illustrates that understanding the cache state requires an exact rather than an approximate understanding of the memory access history.

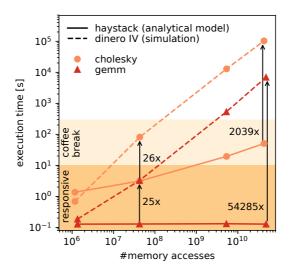

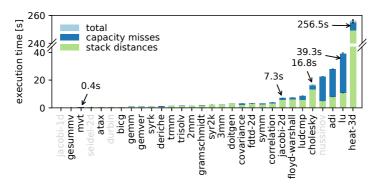

Programmers may have a notion of the relative cost of different implementation variants. But having the exact memory access history in mind is hard. We thus developed the analytical cache model HAYSTACK that computes exact cache miss information to provide programmers the means to estimate the cost of data movement.

The screenshot in Figure 1.2 shows the output of HAYSTACK for generalized matrix multiplication. The tool analyzes the cache misses for every memory access of the program and prints the percentage of compulsory and capacity misses relative to the total number of memory accesses. This fine-grained analysis allows programmers to estimate the memory access cost of individual loop nests and statements. The tool also computes the total number of compulsory and capacity misses. These absolute numbers are helpful when comparing different implementation variants. For example, we may determine if a tiling is effective by running the tool on a tiled and an untiled implementation variant of the same program.

#### 1.3 IMPORTANCE OF THE PROGRAMMING MODEL

A high-performance computing programming model ideally abstracts low-level implementation details of the target system to improve performance portability. At the same time, the programming model should provide the necessary control to attain optimal performance. These two targets are conflicting and sometimes result in design choices that make specific hardware features inaccessible.

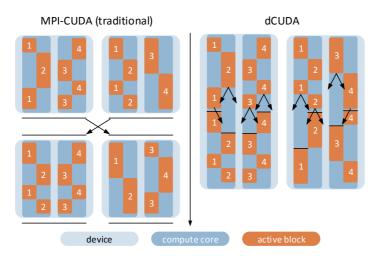

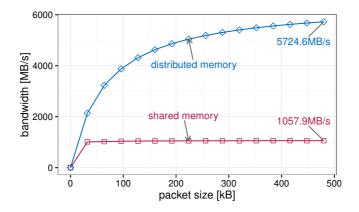

Overlapping computation and inter-node communication [10, 39] is an important data movement optimization in distributed memory computing. We can manually implement it by splitting the compute domain of every node into an inner and an outer domain. We may then overlap the inter-node communication with the computation on the inner domain. The manual application of this optimization is tedious, and its effectiveness depends on the size of the two domains. The computation on the inner domain has to take long enough to overlap the communication. At the same time, both the inner and the outer domain have to be large enough to avoid performance penalties due to the reduced parallelism.

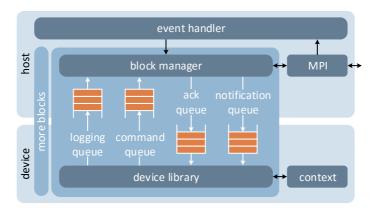

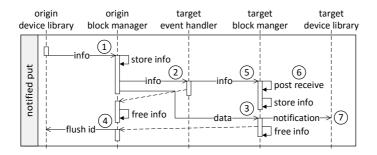

In GPU computing, sufficient amounts of parallelism are a prerequisite to attain optimal performance [40]. Splitting the compute domain to overlap computation and inter-node communication may thus harm the overall performance. Instead, it seems desirable to use the built-in hardware latency hiding – over-subscription and hardware threading – to hide the inter-node communication. But the existing GPU programming models do not provide communication primitives that benefit from this hardware latency hiding.

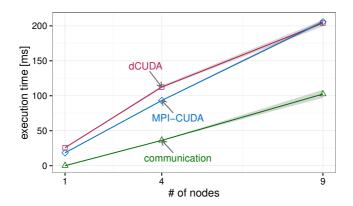

We developed the DCUDA programming model that implements deviceside communication primitives to take advantage of the hardware latency hiding. If a thread waits for incoming data, the GPU immediately proceeds with the execution of another thread that is ready for execution and thus automatically hides the inter-node communication latency. The project demonstrates the importance of an expressive programming model that provides access to all relevant hardware features.

#### 1.4 THESIS CONTRIBUTIONS

This thesis makes the following main contributions:

• In Chapter 2, we present the stencil algebra MODESTO that defines the space of possible data-locality transformations for stencil programs. A

stencil program executes a sequence of different stencils that depend on each other.

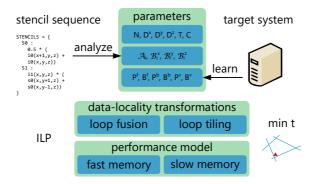

- In Chapter 3, we introduce the stencil program optimizer ABSINTHE that learns a performance model to select good data-locality transformations. A single integer linear program optimizes loop fusion and loop tiling in tandem.

- In Chapter 4, we discuss the analytical cache model HAYSTACK that

computes the cache misses for polyhedral programs. The model provides both programmers and compilers with exact cache miss information to support the choice of suitable data-locality optimizations.

- In Chapter 5, we introduce the programming model DCUDA that enhances the CUDA programming model with device-side internode communication. This extension enables the automatic overlap of communication and computation.

We believe that optimizing the data movement of high-performance computing codes requires better tools, compilers, and programming models. This thesis contributes to all three domains and also motivates further research. The ultimate goal is the development of code generators that learn the performance of the target system and then lower domain-specific code to optimized code that makes optimal use of the hardware. ABSINTHE demonstrates the feasibility of this vision for the stencil domain.

#### A STENCIL ALGEBRA

Stencil computations on regular domains are one of the most important algorithmic motifs in embedded, high-performance, and scientific computing. Applications range from climate modeling [41], seismic imaging [42], fluid dynamics, heat diffusion and electromagnetic simulations [43] through image processing [12] to machine learning. Given their importance, numerous optimization strategies [44–46] and domain-specific languages [11, 12, 22] exist. Yet, most of these schemes consider the optimization of a single stencil in isolation. Many applications, however, require nested stencils [35] that are applied in succession. The data dependencies of these nestings can form complex directed acyclic *stencil graphs* where multiple stencils need to be optimized in tandem to achieve highest performance.

Stencils programs perform element-wise computations on a fixed neighborhood called the stencil. Such stencils often have low arithmetic intensity because they have a fixed number of operations per loaded value. The biggest challenge is to map stencil programs to modern architectures with a growing gap between memory and compute bandwidth. Such architectures require *data-centric optimizations* that arrange data accesses to efficiently use the available memory bandwidth. Complex stencil graphs can be optimized using various techniques such as loop fusion, tiling, and various communication strategies on subgraphs. We model all possible combinations of optimizations for a particular stencil program (graph) using a *stencil algebra* and apply mathematical optimization techniques to find the best combination specific to an abstract hierarchical machine model.

Since typical stencil programs contain hundreds of stencils arranged in paths with dozens of stages and several input arrays, manual tuning of all options is infeasible. In fact, the number of stencil program variants is usually exponential in the number of stencils. In addition, the optimal stencil program variant is specific to each architecture. We show how to fully automate the optimization and implement it in our open-source tool MODESTO, a model driven stencil optimization framework. We demonstrate the efficacy of our method using the real-world application COSMO [41], a numerical weather prediction and regional climate model used by more than 10 national weather services and many other institutions. The dynamical core of COSMO, a central part of its implementation, applies more than

150 stencils, each operating on 13 arrays on average. This most performance-critical code has been rewritten using the STELLA library and was carefully tuned by experts for optimal performance. Modesto-optimized stencil graphs match or improve upon the expert-tuned code by a factor of 1.0-1.8x. This demonstrates how our technique enables next generation stencil libraries that completely abstract optimizations from the library interface. Hence, we are able to improve usability as well as performance portability compared to state-of-the-art stencil libraries such as STELLA [6] or Halide [12]. In summary, we make the following contributions:

- We introduce a set of data-centric code transformations, an algebraic formulation of the transformation space, and a compile-time performance model that enables the automatic optimization of complex stencil programs.

- We evaluate our approach by modeling the optimization of stencil codes written using the STELLA library and successfully tune kernels of a real-world application.

- We formulate the automatic tuning of stencil programs as a mathematical optimization problem and solve it using dynamic programming techniques.

#### 2.1 STENCIL ALGEBRA

Although the stencil motif appears in a wide range of codes from various application domains, common patterns can be identified. Using them, we introduce a stencil algebra that formalizes stencil computations and facilitates their analysis and optimization.

# 2.1.1 Definition of a Stencil Program

The following core elements describe a stencil program:

A *field* F defines a dense, multi-dimensional and commonly hyperrectangular set of data values, which can be read and modified.

A *stencil* S is a computation that derives a value located in an output field from a set of input field values located within bounded distance to the output value. It is described by the triple (*ops*, *out*, *in*). The first element, *ops*, specifies the (possibly approximated) computational cost of executing this stencil. The second element, *out*, is the output field of the

stencil. The third element, in, is a set that defines the input elements of the stencil. The elements of the input set are so-called "named vectors" that are named according to the field the input is read from and the vector itself describes the location of the input element as a relative offset to the position of the element the stencil computes. The set of input elements in is not allowed to contain elements of the output field. We define an example stencil s that computes the value  $F_0(i,j)$  from the inputs  $F_1(i,j)$ ,  $F_1(i,j+1)$  and  $F_2(i,j)$  with 5 computational operations using the following notation:  $s := (5, F_0, \{F_1(0,0), F_1(0,1), F_2(0,0)\})$

A *stencil program*  $P = T \cup O$  consists of a set of temporary stencils T as well as a set of output stencils O, where the results computed by the output stencils form the result of the stencil program, but the results of the temporary stencils are not made available outside of the stencil program. All stencils and fields have the same dimensionality.

The program definition just introduced is formulated minimalistic way and with a strong focus on stencil graphs. As a consequence, it omits aspects that in the context of this work are of limited importance, e.g., boundary conditions, variable input field dimensionality, as well as complex dynamic control flow. However, programs that use such concepts can, in many cases, still be modeled. For example, stencils with varying input sets, due to the use of special boundary conditions, can often be modeled with an overapproximated input set and iterative stencil computations can be modeled by (partially) unrolling the relevant time loop.

## 2.1.2 Example

We now present an example stencil program which is derived from a horizontal diffusion kernel used by the COSMO atmospheric model [41]. We define the stencil program  $P_{hd}$  in terms of the temporary stencils  $s_{lap}$ ,  $s_{fli}$ , and  $s_{flj}$  necessary to evaluate the output stencil  $s_{out}$ . A data dependency either refers to an input field loaded by the stencil program, such as in or

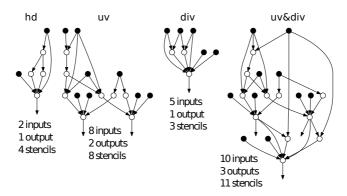

FIGURE 2.1: Horizontal diffusion dependency graph annotated with stencil (*c*) and stencil program (*a*, *b*, and *d*) access patterns

*wgt*, or to a temporary field computed by the corresponding temporary stencil, such as *fli*, *flj*, or *lap*:

$$\begin{split} s_{lap} &:= (5, lap, \{in(-1,0), in(1,0), in(0,-1), in(0,1), in(0,0)\}) \\ s_{fli} &:= (1, fli, \{lap(1,0), lap(0,0)\}) \\ s_{flj} &:= (1, flj, \{lap(0,1), lap(0,0)\}) \\ s_{out} &:= (5, out, \{fli(-1,0), fli(0,0), flj(0,-1), flj(0,0), wgt(0,0)\}) \\ P_{hd} &:= \{s_{lav}, s_{fli}, s_{fli}\} \cup \{s_{out}\} \end{split}$$

Figure 2.1 illustrates the data flow of the stencil program using a directed graph, whose black and white nodes represent input fields and stencils, respectively. Arrows that do not point to a node and consequently exit the stencil graph model the outputs of the stencil program. A directed edge in the graph corresponds to a flow dependency between two nodes. We annotate each incoming edge of a stencil with the access pattern necessary for a single stencil evaluation. For instance, a single evaluation of the *lap* stencil accesses the *in* field at the five offsets shown by c. In addition, we annotate all outgoing edges of a stencil or an input field with the accumulated access pattern necessary to evaluate the out stencil at a single position. E.g., the lap stencil is evaluated at the positions defined by the union of the sets a and b. We compute the accumulated in field access pattern *d* as the Minkowski sum  $d = (a \cup b) \oplus c$ , with  $a \oplus b = \{a' + b' \mid a \oplus b = a' + b' \mid a \oplus b$  $a' \in a, b' \in b$ }. Figure 2.2 shows a naive implementation of the horizontal diffusion kernel, which executes each stencil using a separate loop nest. While such an implementation may be straightforward to write, it is not efficient in terms of data locality, memory usage, or parallelism.

```

// allocate temporary storage

2 Field[double] lap(ibegin,iend), fli(ibegin,iend), flj(ibegin,iend);

// apply the lap stencil

for(int i=ibegin-1; i<iend+1; ++i)</pre>

for(int j=jbegin-1; j<jend+1; ++j)</pre>

6

lap(i,j) = -4.0 * in(i,j) +

in(i-1,j) + in(i+1,j) + in(i,j-1) + in(i,j+1);

7

// apply the fli stencil

for(int i=ibegin-1; i<iend; ++i)</pre>

9

for(int j=jbegin; j<jend; ++j)</pre>

10

fli(i,j) = lap(i+1,j) - lap(i,j);

11

// apply the flj stencil

12

for(int i=ibegin; i<iend; ++i)</pre>

13

for(int j=jbegin-1; j<jend; ++j)</pre>

14

flj(i,j) = lap(i,j+1) - lap(i,j);

// apply the out stencil

16

for(int i=ibegin; i<iend; ++i)</pre>

17

for(int j=jbegin; j<jend; ++j)</pre>

18

out(i,j) = wqt(i,j) *

19

(fli(i-1,j) - fli(i,j) + flj(i,j-1) - flj(i,j));

20

```

Figure 2.2: Naive implementation of the simplified horizontal diffusion example used by the COSMO [41] atmospheric model

## 2.1.3 Data Locality Transformations

To improve the data locality of stencil programs, we discuss code transformations that combine loop tiling and loop fusion. While tiling sub-divides the loop domain into typically hyperrectangular tiles of limited size, fusion substitutes a sequence of loops by a single loop. Applied to stencil codes, we divide the stencil evaluation domain into tiles and apply multiple stencils tile-by-tile. Consequently, we can store temporary values in smaller buffers that hold the working set of a single tile instead of the full evaluation domain.

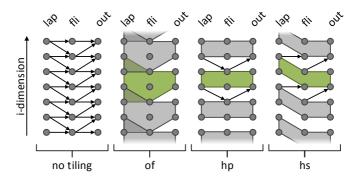

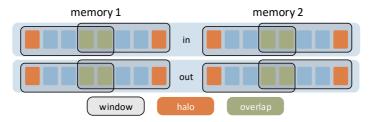

While tiling increases the data locality, it causes additional synchronization efforts at the tile boundaries. As shown in Figure 2.1, a single stencil evaluation depends on one or more input or temporary fields accessed in a local neighborhood. When combining multiple stencils the neighborhoods grow depending on the stencil access patterns and the longest path in the dependency graph. We call all dependencies outside of the tile domain the *halo points* of a tile. In addition, we suggest three halo strategies that trade off parallelism against computation. Figure 2.3 shows the iteration space

Figure 2.3: Tile shapes (shaded) for different tilings applied to a subset of the horizontal diffusion example projected to the *i*-dimension

of one dependency path in the horizontal diffusion example, once without any tiling and then with different tiles as they result from the suggested halo strategies. Shaded regions mark the points that belong to a specific tile.

COMPUTATION ON-THE-FLY (OF) satisfies all halo point dependencies using redundant computation at the tile boundaries. Hence, we load input fields and evaluate temporary stencils in an extended domain covering the tile itself as well as its halo points. Using computation on-the-fly, we can update different tiles independently postponing synchronization at the cost of additional computation. As shown by Figure 2.3, computation on-the-fly results in overlapping tiles and is therefore often referred to as overlapped tiling [8, 9, 12].

HALO EXCHANGE PARALLEL (HP) satisfies all halo point dependencies using communication with neighboring tiles. More precisely, we update all tiles in parallel and perform at least one halo exchange communication per edge in the longest dependency chain of the stencil dependency graph. Hence, halo exchange parallel avoids redundant computation at the cost of additional synchronizations.

HALO EXCHANGE SEQUENTIAL (HS) modifies the tile shape such that all unsatisfied halo point dependencies point in one direction. By iterating over the tiles in reverse dependency direction, we can update all tiles sequentially using a single sweep. While halo exchange sequential in general applies to one-dimensional tilings only, we can complement it with other halo

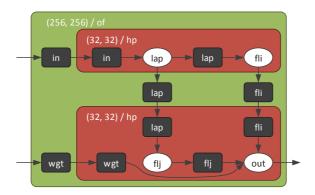

Figure 2.4: Stencil dependency graph of the horizontal diffusion example annotated with two tiling hierarchy levels.

strategies to support higher dimensional tilings. In summary, halo exchange sequential avoids redundant computation and synchronizations at the cost of being sequential.

As the surface to volume ratio decreases with increasing tile size, we preferably update small tiles using halo exchange communication and large tiles using computation on-the-fly. Depending on the hardware architecture high synchronization costs make computation on-the-fly attractive. Overall, choosing the optimal data locality transformations is not straight forward and motivates the use of a performance model.

# 2.1.4 Stencil Algebra Definition

Using the data locality transformations introduced in the previous section, we are able to generate a large number of stencil program implementation variants. In particular, we can repeatedly apply our tiling transformations to obtain a hierarchical tiling that leverages multiple levels of the memory hierarchy. By combining our data locality transformations, we are therefore able to cover most of the established stencil implementation techniques. Next, we formally define a stencil algebra whose elements express different stencil program implementation variants and show how to enumerate them. Figure 2.4 shows an implementation variant of the horizontal diffusion example, introduced in Section 2.1.2, annotated with two tiling hierarchy levels. Each white node corresponds to a stencil and each black node to a storage region that buffers either an input or a temporary field. We extend

the dependency graph with boxes that represent the tiling hierarchy. More precisely, the boxes form a tiling tree where each box corresponds to a tiling that executes all contained boxes respectively stencils. Finally, we annotate each box with the tile size and the halo strategy of the tiling. In Figure 2.4 we employ an on-the-fly tiling at the bottom of the tiling hierarchy with two nested halo exchange parallel tilings.

In order to specify an element of our stencil algebra, we initially define a tiling hierarchy. More precisely, we define a tile size  $t^l \in \mathbb{Z}^n$  for each level l of the tiling hierarchy. In case of the horizontal diffusion example we define two tiling hierarchy levels:

$$t_{hd}^1 = (256, 256)$$

$t_{hd}^2 = (32, 32)$

Next, we specify a stencil program implementation variant as a bracket expression. We put all stencils that correspond to a specific tiling hierarchy level into brackets. A hierarchical tiling thus results in a nested bracket expression with the outermost bracket term representing the bottom of the tiling hierarchy. We can define the horizontal diffusion implementation variant shown by Figure 2.4 using a twofold nested bracket expression.

$$\left[\left[s_{lap}, s_{fli}\right], \left[s_{flj}, s_{out}\right]\right]$$

In the following, we call each bracket term representing a tiling hierarchy a stencil group. A stencil group can be seen as a node of the tiling tree containing nested stencils or stencil groups that as a whole define the stencil program implementation variant.

Let *g* be a stencil group, then *g.child* is the set of all children of the stencil group *g*, where a child is either a stencil or a nested stencil group. In addition, *g.sten* is the set of all stencils in the subtree defined by the stencil group *g*. Finally, *g.in* and *g.out* define the input and output sets of a stencil group *g*, where an input and an output correspond to an incoming respectively to an outgoing data dependency. As an example, we provide the stencil properties of the horizontal diffusion example shown in Figure 2.4.

$$g_0 = [g_1, g_2]$$

$g_1 = [s_{lap}, s_{fli}]$   $g_2 = [s_{fli}, s_{out}]$

First, we define the tree properties.

$$g_0.child = \{g_1, g_2\}$$

$g_0.sten = \{s_{lap}, s_{fli}, s_{fli}, s_{out}\}$

Next, we define the external data dependencies.

$$g_0.in = \{in, wgt\}$$

$g_0.out = \{out\}$

We enumerate all stencil program implementation variants using two operations: 1) shuffle the stencils respecting their topological order and 2) group stencils on different tiling hierarchy levels.

## 2.1.5 Performance Modeling

In order to understand the performance characteristic of a stencil program implementation variant, we next introduce a performance model. Similar to the Roofline model [47], we estimate the execution time based on the peak compute and communication throughput of the target hardware. In addition, we do not only distinguish between cached and global memory accesses but model additional memory hierarchy levels.

To model our target hardware we use an abstract machine that is built around a processing unit that performs computations on a limited set of local registers. All data is by default stored in a global memory (e.g., DRAM) with limited bandwidth to the processing unit. Data is transferred from global memory to local registers before any computation is performed and the results of a computation are transferred back to global memory before becoming externally visible. Between global memory and local registers there is a set of additional hierarchically organized memory levels, each with limited size, but increasing bandwidth to the processing unit.

When mapping a parallel hardware architecture to our model, the bandwidth of a given memory hierarchy level is the combined bandwidth of all (possibly multiple) memories at this level. The size of a memory hierarchy level is not the combined size, but the size of an individual memory at this level. E.g., assuming there are multiple L1 caches, we consider the size of a single L1 cache. Finally, assuming sufficient parallelism to simultaneously use all processing resources, the compute throughput of our model is the combined peak compute throughput of the hardware architecture.

We now consider again Figure 2.4, an illustration of a stencil program implementation variant with two tiling hierarchy levels that was introduced in the previous section. Each tiling hierarchy targets one specific level of the memory hierarchy, such as the DDR memory or the L1 cache of a CPU. We assume all input and temporary values of a stencil group are stored in the associated memory hierarchy level. Whenever a stencil program communicates data from one tiling hierarchy level to the next higher one, we model the communication time using the bandwidth of the associated memory hierarchy level. Therefore, we define a communication bandwidth  $V^l \in \mathbb{R}$  as well as a memory capacity  $M^l \in \mathbb{Z}$  for each level

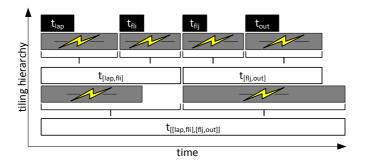

Figure 2.5: The time estimation for the horizontal diffusion example

l of the tiling hierarchy. In addition to this vertical communication, a stencil code might also perform lateral halo exchange communication between neighboring tiles of the tiling hierarchy. Hence, we define a lateral communication bandwidth  $L^l \in \mathbb{R}$  for each level l of the tiling hierarchy. Typical representatives of lateral communication links are interconnect networks or the scratch pad memory of a GPU. Finally, we define the compute throughput  $C \in \mathbb{Z}$  of the target architecture. Thereby, we define storage sizes in terms of floating point values instead of bytes. In case two nested tiling hierarchy levels are associated to the same memory hierarchy level, we set the vertical communication bandwidth to infinity. Just like the Roofline model, we assume that we can overlap communication and computation on all communication links respectively compute units of the system.

When modeling the performance of a stencil program, we assume that the arithmetic intensity remains constant during the execution of a single stencil. On the other hand, the arithmetic intensities of different stencils might vary. Figure 2.5 illustrates the time estimation for the horizontal diffusion implementation variant shown by Figure 2.4. At the top of the tiling hierarchy, black boxes denote the stencil execution times. Below, gray boxes (with flashes) denote the communication times between parents and children in the tiling hierarchy. Furthermore, white boxes denote the stencil group execution times computed as the sum of the maximum between stencil execution times and communication times.

In particular, we estimate the execution time  $t_s$  of a stencil s that performs  $c_s$  floating point operations as the time needed to compute the stencil without considering any communication cost.

$$t_s = c_s/C$$

Using the child execution time  $t_c$  of a child stencil or stencil group c that causes  $v_c$  vertical and  $l_c^1, \ldots, l_c^l$  lateral data movements, we compute the execution time  $t_g$  of a stencil group g that corresponds to level l of the tiling hierarchy as the sum of the maximum of the child execution times, the vertical communication between the stencil group and its children, and the lateral communication necessary to update the halo points of the temporary fields. We thereby optimistically assume the lateral communication overlaps with the child execution, which assumes the later communication is sufficiently balanced over the stencil group execution.

$$t_g = \sum_{c \in g.child} \max(t_c, v_c/V^l, l_c^1/L^1, \dots, l_c^l/L^l)$$

We model the performance of an entire stencil program as the estimated execution time of the stencil group at the bottom of the tiling hierarchy. Furthermore, we complement the performance estimation with a feasibility check that compares the storage requirements of the stencil program to the available memory capacity on all tiling hierarchy levels.

## 2.1.6 Stencil Program Analysis

In order to evaluate our performance model, we analyze stencil programs using the mathematical concept of affine sets and affine maps. In particular, we show how to count the number of floating point operations, data movements, and storage locations required during the stencil program execution. Using the performance model introduced in Section 2.1.5, our analysis finally allows us to estimate the execution time and the feasibility of a stencil program.

# 2.1.6.1 Affine Sets and Maps

An affine set  $S = \{\vec{i} \mid \vec{i} \in \mathbb{Z}^n \land \operatorname{cons}(\vec{i})\}$  is a set of n-dimensional integer vectors, where the elements of the set are constrained by a Presburger formula  $\operatorname{cons}(\vec{i})$ . Presburger formulas consist of comparisons  $(<, \leq, =, \neq, \geq, >)$  between expressions (quasi-)affine in vector dimensions and external parameters that are combined by Boolean operations  $(\land, \lor, \neg)$ . For affine sets set operations such as union, intersection, subtraction, projection as well as cardinality are defined.

An affine map  $M = \{\vec{i} \to \vec{j} \mid \vec{i} \in \mathbb{Z}^n, \vec{j} \in \mathbb{Z}^m \land \cos(\vec{i}, \vec{j})\}$  is a relation, that relates n-dimensional input (domain) vectors with m-dimensional output (range) vectors. The elements are again constraint by a Presburger formula

$\cos(\vec{i}, \vec{j})$ . Besides the normal set operations, there exist map-specific operations such as the application of a map m on a set s (m(s)), the composition of two maps ( $m_0 \circ m_1$ ), or the inverse of a map ( $m^{-1}$ ), which switches input and output of a map. We define the following set of important map operations in more detail.

The range product of two maps  $R_1$  and  $R_2$  is defined as:

$$R_1 \times_{\operatorname{ran}} R_2 = \{ \vec{i} \to (\vec{j}_1, \vec{j}_2) \mid \vec{i} \to \vec{j}_1 \in R_1 \land \vec{i} \to \vec{j}_2 \in R_2 \}$$

The range intersection of a map *R* with a set *S* is:

$$R \cap_{\operatorname{ran}} S = \{\vec{i} \to \vec{j} \mid \vec{i} \to \vec{j} \in R \land \vec{j} \in S\}$$

The range-projection of a map R projects the n output dimensions of a map onto the first k+1 output dimensions:

$$\mathcal{P}_{[0-k]}^{\text{ran}}(R) = \{ \vec{i} \to (j_0, \dots, j_k) \mid \exists x_{k+1}, \dots, x_{n-1} \in \mathbb{Z} : \\ \vec{i} \to (j_0, \dots, j_k, x_{k+1}, \dots, x_{n-1}) \in R \}$$

$R^+$  is the transitive closure of R:

$$R^{+} = \{\vec{i} \to \vec{j} \mid \exists m \ge 0 : \vec{j} = (\underbrace{R \circ \cdots \circ R}_{m \text{ times}})(\vec{i})\}$$

We use |S| to specify the cardinality of a set and |R| to specify the cardinality of a map, where the cardinality of a map is defined as the number of related domain and range pairs.

We also define named sets and named maps as affine sets and maps that contain so-called "named vectors". The elements of these sets can either be written as tuples of a string and a vector, for example  $\{("A",\vec{i}),("B",\vec{j})\mid \vec{i}\in\mathbb{Z}^n,\vec{j}\in\mathbb{Z}^m\}$ , or as named vectors  $\{A(\vec{i}),B(\vec{j})\mid \vec{i}\in\mathbb{Z}^n,\vec{j}\in\mathbb{Z}^m\}$ . Named sets (maps) allow differently named elements to have vectors of different dimensionality. On named sets and maps the operations introduced above are applied individually to subsets or submaps that share the same name and dimensionality. To extract a set from a named set S, we define a bracket operator  $S["x"] = \{("x",\vec{i})\mid ("x",\vec{i})\in S\}$ . The bracket operator applied on a map, filters the maps according to the name of their domains  $R["x"] = \{("x",\vec{i}) \rightarrow (name,\vec{j})\mid ("x",\vec{i}) \rightarrow (name,\vec{j})\in R\}$ .

Computations on integer sets can be performed with isl [48] and counting of integer sets is possible using the Barvinok algorithm [49].

## 2.1.6.2 Data Dependencies

Given a stencil program P the set of flow dependencies in P can be derived from the stencil data dependencies. To obtain them, we define for each stencil  $s \in P$  a map  $D_s$  that associates the stencil evaluations to the corresponding input data dependencies.

$$D_s = \{s.out(\vec{u}) \to d(\vec{u} + \vec{v}) \mid d(\vec{v}) \in s.in\}$$

Next, we define the union of all stencil data dependencies.

$$D = \bigcup_{s \in P} D_s$$

## 2.1.6.3 Stencil Tiling Maps

We model the tiling transformations discussed in Section 2.1.3 using affine maps that relate the stencil evaluation domain to the tile domain. More precisely, we define for each stencil a tiling map that maps each point in the *n*-dimensional stencil evaluation domain to an *n*-dimensional tile identifier, such that all points that belong to the same tile are associated with a common tile identifier. We initially consider only a single tiling level and later generalize the concept to nested tilings.

Given a multi-dimensional tile size vector  $\vec{t} = (t_0, \dots, t_{n-1}) \in \mathbb{Z}^n$ , we define a hyperrectangular tiling of a single stencil s as a named map  $T_s^{\square}$  that associates each point  $\vec{i} = (i_0, \dots, i_{n-1}) \in \mathbb{Z}^n$  of the stencil evaluation domain with exactly one tile identifier.

$$T_s^{\square} = \{(s, \vec{i}) \rightarrow (\lfloor i_0/t_0 \rfloor, \dots, \lfloor i_{n-1}/t_{n-1} \rfloor)\}$$

Depending on size and alignment of tiles and stencil evaluation domains, such a tiling may yield truncated tiles at the stencil evaluation domain boundaries. In case a given dimension of the stencil evaluation domain should not be tiled (indicated by tile size  $\infty$ ), the corresponding dimension of the tile identifiers is set to zero.

We represent the tiling of a stencil group g by computing a named map that contains a tiling map for each stencil of the stencil group. We distinguish here between the three halo strategies introduced in Section 2.1.3.

Computation on-the-fly satisfies halo point dependencies using redundant computation. The corresponding tiling map is therefore a relation which maps the halo point stencil evaluations at the tile boundaries to multiple overlapping tiles. Given a stencil group g, we construct a tile map  $T_g$

in two steps. First, all output stencils of g are tiled with a rectangular tiling map. This does not yet introduce any redundant computation. Next, we compute for each tile all stencil evaluations that are required to compute the output points already assign to this tile. We do this by first defining the set of data dependencies  $D_g$  that are local to g and then composing the inverse transitive hull of  $D_g$  with the tiling map already defined for the output stencils. The resulting map connects the temporary stencil evaluations via the dependent output stencil evaluation to the corresponding tile identifier. This map may now possibly relate one temporary stencil evaluation to multiple tiles and can consequently introduce redundant computation.

$$T_g = \bigcup_{s \in g, out} T_s^{\square} \circ (D_g^+)^{-1}$$

Halo exchange parallel satisfies halo point dependencies using communication. We therefore assign each point in the stencil evaluation domain to exactly one tile and use tiles of identical size, shape and alignment for all stencils in our stencil group. The tiling map  $T_g$  describes such a tiling for a stencil group g.

$$T_g = \bigcup_{s \in g.sten} T_s^{\square}$$

Halo exchange sequential is a variant of halo exchange parallel, whose tiling map is constructed accordingly. In contrast to halo exchange parallel, we shift the stencil tiling maps such that all unsatisfied halo point dependencies between tiles point in one direction. Figure 2.3 illustrates the tile shape of shifted stencil tiling maps and their halo point dependencies. We define a shifted tiling map by subtracting the shift offset form the stencil evaluation domain before computing the associated tile identifiers.

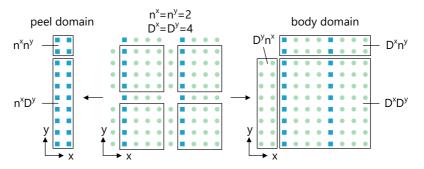

NESTED TILINGS We now describe the construction of nested tilings, tilings that result from recursively applying the previously introduced tiling transformations. To give a first intuition of such tilings, Figure 2.6 shows the different nested tilings that can be constructed from combining on-the-fly and halo exchange parallel tiling on two tiling levels. It shows for each combination one full outer tile, one full inner tile, and, using dashed lines, the remaining inner tiles placed inside the outer tile. Most combinations are rather straightforward, but it is interesting to note, that in case of on-the-fly tiling being nested inside halo exchange parallel tiling, the redundant computation of the on-the-fly tiles may require the computation of points located outside of the surrounding tile.

Figure 2.6: Tile shapes (shaded) for a nested tiling applied to a subset of the horizontal diffusion example projected to the *i*-dimension

$$T_{g,s} = T_p[s] \times_{ran} T_s^{\square}$$

When computing the tiling map of a nested stencil group  $T_g$ , we adapt the previously introduced on-the-fly and halo exchange tiling maps to use  $T_{g,s}$  instead of  $T_s^{\square}$ . The resulting tiling maps for halo exchange parallel and on-the-fly tiling are

$$T_g = \bigcup_{s \in g.sten} T_{g,s}$$

and  $T_g = \bigcup_{s \in g.out} T_{g,s} \circ (D_g^+)^{-1}$ .

We can now define for each stencil a tiling map  $T_s$  that maps each evaluation of this stencil to a tile identifier with  $l \cdot n$  dimensions, that identifies for all levels of the tiling hierarchy the tiles the stencil evaluation is assigned to.

We obtain  $T_s$  by extracting the tile map that corresponds to s from the tile map of the stencil group g at the top of the tiling hierarchy that contains s.

$$T_s = T_g[s]$$

When constructing hierarchical tilings that involve halo exchange sequential, we inherit the shift offsets introduced by the sequential execution to all nested tiling hierarchy levels. Thereby, we align the nested tiles to the parent tile boundaries.

## 2.1.6.4 I/O Maps

While the tiling maps alone allow the analysis of computational aspects, we introduce auxiliary maps that support the analysis of data movements and storage usage.

First, we define for each stencil s an input map  $I_s$  that relates a set of inputs (stencil evaluations or input fields) used by a certain evaluation of s to the tile(s) this evaluation is assigned to. The construction of  $I_s$  is similar to the construction of the on-the-fly tiling. We compose the stencil tiling map  $T_s$  with the reversed stencil data dependencies  $D_s^{-1}$ . Furthermore, we define the input map of an entire stencil group g as the union of all nested stencil input maps.

$$I_s = T_s \circ D_s^{-1}$$

$I_g = \bigcup_{s \in g.sten} I_s$

Second, we define for each child stencil or stencil group c an output map  $O_c$  that relates the set of outputs written by the child to the tiles they are assigned to. In case the parent stencil group applies halo exchange communication, we define the output map  $O_c$  as the union of the child output stencil tiling maps.

$$O_c = \bigcup_{s \in c.out} T_s$$

In case the parent stencil group applies computation on-the-fly, we compute the output map by following the data dependencies starting from the parent stencil group output stencils. While this construction is similar to the computation of the on-the-fly stencil evaluation tiling map, it differs by the fact that we only consider the data dependencies of the stencils executed after the child stencil or stencil group. Thereby, we make sure we do not consider internal dependencies between the output stencils of the

child stencil group. Initially, we define the partial input map  $I_{p,c}$  of a parent stencil group p and a child stencil or stencil group c considering all input dependencies of children executed after the child c.

$$I_{p,c} = \bigcup_{\substack{c_i \in p.child \\ c < c_i}} I_{c_i}$$

Then the output map  $O_c$  of a child stencil or stencil group is the union of all partial input and parent output dependencies.

$$O_c = \bigcup_{s \in c.out} \left( I_{p,c}[s] \cup \left( \bigcup_{o \in p.out} T_{p,o} \right) [s] \right)$$

### 2.1.6.5 Tile Selection

We analyze the characteristics of a stencil program by counting stencil evaluations, data movements, or storage requirements on a limited domain. As we are interested in the relative rather than the absolute performance and as our performance model does not consider low hardware utilization due to strong scaling, we can choose an arbitrary but limited domain size. We therefore perform our analysis on the origin tile of the lowest tiling hierarchy level. Assuming m tiling hierarchy levels, we select the origin tile of the lowest tiling hierarchy level using the tile selection set S that contains all tile identifiers with the first n-dimensions fixed to zero.

$$S = \{(x_0, \dots, x_{n-1}, y_n, \dots, y_{nm}) \mid x_i = 0 \land y_i \in \mathbb{Z}\}$$

When analyzing the storage requirements, we want to make sure a single tile fits the memory capacity of the corresponding memory hierarchy level. We thus define an additional tile selection set  $S^*$  that selects the origin tile on all levels of the tiling hierarchy.

$$S^* = \{(x_0, \ldots, x_{nm}) \mid x_i = 0\}$$

In order to limit the domain of a tiling map, we finally intersect the range of the tiling map with a selection set.

# 2.1.6.6 Analysis

Relying on the previously introduced stencil program formulation, we now discuss the analyses we use to obtain the program properties needed for

evaluating the performance model introduced in Section 2.1.5. Using the previously introduced maps, we count the points that correspond to the number of stencils evaluations, the amount of data moved, and the amount of storage used when evaluating a given stencil program on a limited domain.

COMPUTATION In order to analyze the amount of computation performed by a stencil program, we count the stencil evaluations associated to the origin tile of the lowest tiling hierarchy level. We obtain these evaluations by intersecting the range of the stencil evaluation tiling map with the origin tile selection set S. We then count all stencil evaluations associated to the remaining tile identifiers. Hence, we define the amount of computation  $c_s$  performed by a stencil s as the cardinality of the constraint tiling map times the number of floating point operations performed by a single stencil evaluation.

$$c_s = |T_s \cap_{\text{ran}} S| \cdot s.ops$$

VERTICAL COMMUNICATION As discussed in Section 2.1.5, vertical communication refers to the data movements between a parent stencil group and its child stencils or stencil groups. We therefore analyze the number of loads and stores performed by a child stencil or stencil group when executed by a parent stencil group. We analyze the vertical communication on a restricted domain that corresponds to the origin tile of the lowest tiling hierarchy level.

In order to compute the number of loads performed by a stencil or stencil group c, we count the elements in the constraint input map of c. More precisely, we intersect the range with the origin tile selection set and project out any dimension above the parent stencil group tiling hierarchy level l. Due to the projection, the points in the resulting map describe all elements loaded by the child stencil or stencil group not considering redundant stencil evaluations on nested tiling hierarchy levels. Hence, we define the number of loads  $r_c$  performed by a child stencil or stencil group c as the cardinality of the constraint and projected child input map.

$$r_c = \sum_{s \in c.in} |\mathcal{P}_{[0-nl]}^{\text{ran}}(I_c[s] \cap_{\text{ran}} S)|$$

Accordingly, we define the number of stores  $w_c$  performed by a child stencil or stencil group c as the cardinality of the constraint and projected child output map.

$$w_c = \sum_{s \in c.out} |\mathcal{P}_{[0-nl]}^{\text{ran}}(O_c[s] \cap_{\text{ran}} S)|$$

Finally, we define the total amount of vertical communication of a child stencil or stencil group c as the sum of its loads and stores.

$$v_c = r_c + w_c$$

LATERAL COMMUNICATION Lateral communication refers to the halo exchange communication between neighboring tiles of the same tiling hierarchy level. We therefore compute the lateral communication performed by a stencil group as the difference between the amount of computed and the amount of consumed temporary values, which corresponds to the unsatisfied halo point dependencies between the children of the stencil group. We analyze the lateral communication on a restricted domain that corresponds to the origin tile of the lowest tiling hierarchy level.

We compute the amount of lateral communication necessary to update the outputs of a child stencil or stencil group, as the difference of the elements used by subsequent children and the elements written by the child itself. We thus intersect the range of this difference with the origin tile selection set and project out any dimensions above the parent stencil group tiling hierarchy level l. Hence, we define the amount of halo points  $l_c$  communicated by a child stencil or stencil group c as the cardinality of the difference between the projected and constraint partial input and output maps.

$$l_c = \sum_{s \in cont} |\mathcal{P}_{[0-nl]}^{\mathrm{ran}}((I_{p,c}[s] \setminus O_c[s]) \cap_{\mathrm{ran}} S)|$$

In case multiple nested tiling hierarchy levels employ halo exchange communication, we possibly run lateral communication on all these levels. By projecting out one level after the other, we assign the lateral communication to the different levels of the tiling hierarchy. Thereby, we get the sum of the lateral communication on the remaining tiling hierarchy levels not yet projected out. By computing the difference of adjacent levels, we finally get the lateral communication assigned to exactly one level.

STORAGE REQUIREMENTS We analyze the feasibility of a stencil program by computing an upper bound for the storage necessary in order to execute a single tile on each level of the tiling hierarchy. We therefore analyze the storage requirements on a restricted domain that corresponds to the origin tile on all levels of the tiling hierarchy. In case the upper bound exceeds the capacity of one memory hierarchy level, we say a stencil program is infeasible.

We compute the storage requirement of a stencil group as the amount of storage necessary to evaluate the stencil group on a single tile. As shown by Figure 2.4, we reserve storage for each input and temporary field used during the evaluation of the stencil group. In contrast, output fields are immediately written to storage managed outside of the stencil group. We overestimate the storage requirement, for example, since the lifetime of some fields might allow sharing a common buffer. We evaluate the storage requirements using the input map intersected with the tile selection set  $S^*$ . Furthermore, we project out any dimension above the parent stencil group tiling hierarchy level l. Hence, we define the amount of storage  $m_p$  required by a parent stencil group p as the cardinality of the constraint and projected input maps.

$$m_p = \sum_{c \in p. child} \sum_{s \in c. in} |\mathcal{P}_{[0-nl]}^{\mathrm{ran}}(I_p[s] \cap_{\mathrm{ran}} S^*)|$$

In order to determine the feasibility of a stencil program, we compare the memory requirements of each stencil group to the available memory capacity.

#### 2.2 CASE STUDY

We evaluate our approach using the real-world application COSMO. Its dynamical core was recently rewritten using the STELLA [6] stencil library, which exposes the possibility to manually fuse or split stencils on multiple tiling hierarchy levels. In this case study we show how to automatically tune STELLA programs.

#### 2.2.1 *STELLA*

STELLA is a domain-specific embedded language for finite difference methods that is designed to separate the stencil specification from the hardware architecture specific implementation strategy. When executing a stencil program STELLA uses two levels of parallelism: 1) coarse-grained parallelization that decomposes the stencil evaluation domain into blocks executed on different processing units and 2) fine-grained parallelization that executes the individual blocks on a single processing unit possibly using vectorization and hardware threads. STELLA supports stencil fusion on three different tiling hierarchy levels. We can apply consecutive stencils using a single loop over a block, using multiple separate loops over a block, or using multiple separate loops over the full domain.

| Hierarchy | Vertical | Tile Size      | Strategy |

|-----------|----------|----------------|----------|

| 1         | DDR      | (256, 256, 64) | of       |

| 2         | L2       | (8, 8, 64)     | of       |

TABLE 2.1: CPU tiling hierarchy

| Hierarchy | Vertical/Lateral  | Tile Size             | Strategy |

|-----------|-------------------|-----------------------|----------|

| 1         | GDDR/-            | (256, 256, 64)        | of       |

| 2         | GDDR/-            | (64, 4, 64)           | of       |

| 3         | Register/Register | $(\infty, \infty, 1)$ | hs       |

| 4         | Register/Shared   | (1,1,1)               | hp       |

TABLE 2.2: GPU tiling hierarchy

At compile-time, STELLA generates target architecture specific loop code using C++ template meta-programming. With two available backends, STELLA can currently target CPU and GPU architectures using the OpenMP and CUDA programming models, respectively. Thereby, STELLA employs a fixed but platform specific tiling hierarchy, which we will model using our stencil algebra.

We model the CPU backend of STELLA using the two tiling hierarchy levels shown by Table 2.1. As discussed in Section 2.1.6, we compute all stencil program performance characteristics for the origin tile of the base tiling hierarchy level. Therefore, we introduce a first tiling hierarchy level that represents the stencil program evaluation domain. A second tiling hierarchy level models the coarse-grained parallelism of STELLA. Currently, the CPU backend does not implement fine-grained parallelism. Hence, there is no need to model the third tiling hierarchy level of STELLA.

We model the GPU backend of STELLA using the four tiling hierarchy levels shown by Table 2.2. Just as in the case of the CPU backend, we introduce two tiling hierarchy levels to model the stencil program evaluation domain and the coarse-grained parallelism. We also add two additional tiling hierarchy levels to represent the fine-grained parallelism. The GPU backend allocates one thread per *ij*-position (tiling hierarchy level 4) that iterates over all points in the *k*-dimension (tiling hierarchy level 3). The different threads communicate via shared memory, while consecutive loop

iterations executed by the same thread communicate via registers. Tile size infinity indicates that there is no tiling in the corresponding dimension.

## 2.2.2 Stencil Program Optimization

When implementing a stencil program using STELLA, we have multiple degrees of freedom. As discussed in Section 2.1.4, we can change the stencil evaluation order and fuse or split the execution of successive stencils on multiple levels of the tiling hierarchy. We therefore split the optimization in two steps and apply different optimization methods: 1) we optimize the stencil evaluation order using brute force search 2) we optimize the tiling for a given stencil evaluation order using dynamic programming. During our optimization we do not consider tile size choices, but rely on the tile sizes that are used by COSMO and have proven robust for a wide range of stencil programs and their implementation variants.

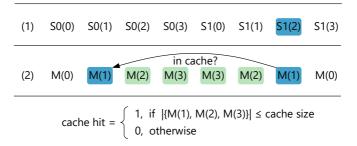

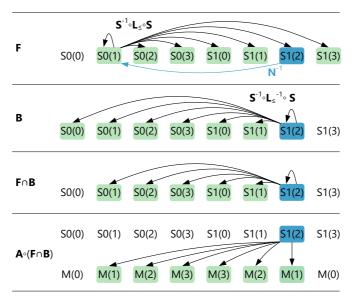

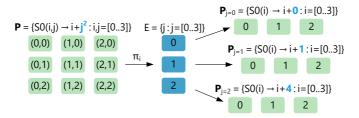

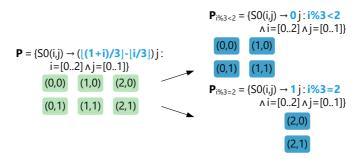

In order to optimize the stencil evaluation order, we enumerate all topological sorts of the stencil dependency graph using brute force search. In general, a graph may have up to  $\mathcal{O}(n!)$  valid topological orders. However, due to its data dependency chains a typical stencil dependency graph has less topological orders resulting in a much smaller search space.