#### DISS. ETH NO. 29662

# CCKit: FPGA acceleration in symmetric coherent heterogeneous platforms

A thesis submitted to attain the degree of

DOCTOR OF SCIENCES of ETH ZURICH

(Dr. sc. ETH Zurich)

presented by

#### ABISHEK RAMDAS

Master of Science in Computer Engineering, NYU

born on 01.10.1988

citizen of India

accepted on the recommendation of

Prof. Dr. Gustavo Alonso (ETH Zurich), examinerProf. Dr. Timothy Roscoe (ETH Zurich), co-examinerDr. Alberto Lerner (University of Fribourg), co-examinerProf. Dr. Ryan Stutsman (University of Utah), co-examiner

2023

# Abstract

FPGA-based accelerators are becoming pervasive in the cloud and data centers due to their architectural flexibility (they are used in many different configurations) and functionality (they can be reconfigured and reprogrammed at runtime). At the same time, standards like CXL raise questions of how a cache coherence protocol should be presented to heterogeneous applications running on, for example, a closely-coupled FPGA-based accelerator. To address these questions, we present CCKit, an open-source toolkit comprising a complete cache coherency stack for FPGAs with software support, and enabling interesting and novel designs beyond simple coherence or, indeed, any requirement for caching on the FPGA. We describe the implementation of CCKit in detail, show through benchmarks that it is highly competitive with hardware-based implementations, but also, critically, that it enables important use-cases for CPU-FPGA coherence beyond those supported by emerging standards.

# Zusammenfassung

FPGA-basierte Beschleuniger sind in der Cloud und in Rechenzentren aufgrund ihrer architektonischen Flexibilität (sie werden in vielen verschiedenen Konfigurationen verwendet) und ihrer Funktionalität (sie können zur Laufzeit neu konfiguriert und neu programmiert werden) immer beliebter geworden. Gleichzeitig werfen Standards wie CXL die Frage auf, wie ein Cache-Kohärenzprotokoll heterogenen Anwendungen präsentiert werden sollte, die beispielsweise auf einem eng gekoppelten FPGA-basierten Beschleuniger laufen. Um diese Fragen zu beantworten, stellen wir CCKit vor, ein Open-Source-Toolkit, das einen vollständigen Cache-Kohärenz-Stack für FPGAs mit Softwareunterstützung umfasst und interessante und neuartige Designs ermöglicht, die über einfache Kohärenz oder überhaupt jede Anforderung für Caching auf dem FPGA hinausgehen. Wir beschreiben die Implementierung von CCKit im Detail, zeigen anhand von Benchmarks, dass es im Vergleich zu hardwarebasierten Implementierungen äußerst konkurrenzfähig ist, aber vor allem auch, dass es wichtige Anwendungsfälle für die CPU-FPGA-Kohärenz ermöglicht, die über die von neuen Standards unterstützten hinausgehen.

# Acknowledgments

I am deeply indebted to my advisor and chair of my committee Dr. Gustavo Alonso for giving me this opportunity and for his invaluable patience and feedback. I would like to express my deepest gratitude to my defense committee, Prof. Dr. Timothy Roscoe, Dr. Alberto Lerner and Prof. Dr. Ryan Stutsman, for generously providing their expertise and enthusiasm. Special thanks to Dr. David Cock and Adam Turowski for their insights and guidance that enabled a lot of work presented in this thesis.

I am also grateful to Dr. Ghislain Fourny for his kindness and our tea-time discussions. Thanks should also go to my colleagues, Daniel, Michael G., Andrea, Michal F., Michal W., Zhenhao, Dario, Monica, Fabio, Anastasiia, Wenqi, Lukas, Melissa, Nora, Ben, Tom, Roman, Jasmin, and Marko, for making the Systems Group such a wonderful place to work at. Many thanks to the administrators Simonetta, Nadia, Jena and Natasha for organizing amazing retreats and their help in general.

Finally, I would be remiss not mentioning my spouse Alena, son Roman and my parents for their unconditional love and support.

# Contents

| 1        | Intr | Introduction |                                    |    |  |

|----------|------|--------------|------------------------------------|----|--|

|          | 1.1  | Backg        | round and Motivation               | 3  |  |

|          |      | 1.1.1        | Symmetric vs. asymmetric protocols | 3  |  |

|          |      | 1.1.2        | The evolution of interconnects     | 4  |  |

|          |      | 1.1.3        | Coherence in MPSoCs                | 5  |  |

|          |      | 1.1.4        | FPGA operating systems             | 6  |  |

|          | 1.2  | Appro        | ach and Design                     | 7  |  |

|          |      | 1.2.1        | Target platform and assumptions    | 7  |  |

|          |      | 1.2.2        | Coherence protocol specification   | 8  |  |

|          |      | 1.2.3        | High-level architecture            | 8  |  |

|          |      | 1.2.4        | FPGA-side interface                | 9  |  |

|          |      | 1.2.5        | CPU-side interface                 | 11 |  |

|          |      | 1.2.6        | CCKit acceleration model           | 11 |  |

|          | 1.3  | Relate       | ed Work                            | 12 |  |

|          | 1.4  | Contri       | ibutions                           | 14 |  |

|          | 1.5  | Struct       | sure of the Dissertation           | 14 |  |

| <b>2</b> | Prir | ner on       | a Cache Coherence                  | 17 |  |

|          | 2.1  | Introd       | uction                             | 17 |  |

|          | 2.2  | Baseli       | ne Multicore System without Caches | 18 |  |

|   | 2.3 | Baselin | ne Multicore System with Caches                                            | 19 |

|---|-----|---------|----------------------------------------------------------------------------|----|

|   |     | 2.3.1   | Problem of incoherence                                                     | 19 |

|   |     | 2.3.2   | Shared memory consistency                                                  | 20 |

|   |     | 2.3.3   | Coherence vs consistency                                                   | 21 |

|   |     | 2.3.4   | Coherence invariants                                                       | 21 |

|   |     | 2.3.5   | Cache line                                                                 | 22 |

|   |     | 2.3.6   | Maintaining coherence invariants                                           | 22 |

|   |     | 2.3.7   | Coherence protocol design space                                            | 27 |

|   |     | 2.3.8   | MSI, MESI, MOESI protocol                                                  | 28 |

|   |     | 2.3.9   | Scaling: Snooping vs Directory based protocols                             | 28 |

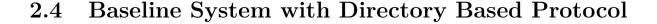

|   | 2.4 | Baselii | ne System with Directory Based Protocol                                    | 29 |

|   |     | 2.4.1   | Maintaining coherence invariants in directory based protocol $\ . \ . \ .$ | 30 |

|   | 2.5 | Direct  | ory Based Coherence in NUMA Systems                                        | 34 |

|   |     | 2.5.1   | Symmetric vs Asymmetric coherent platforms                                 | 35 |

| 3 | CC  | Kit Ba  | seline System Model and Enzian                                             | 37 |

|   | 3.1 | Introd  | uction                                                                     | 37 |

|   | 3.2 | CCKit   | Baseline System Model                                                      | 38 |

|   |     | 3.2.1   | CCKit target platform assumptions                                          | 39 |

|   |     | 3.2.2   | CCKit fundamental design choices                                           | 40 |

|   | 3.3 | Enziar  | 1                                                                          | 41 |

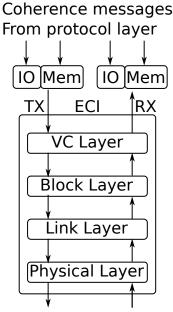

|   |     | 3.3.1   | Enzian Coherent Interconnect (ECI)                                         | 42 |

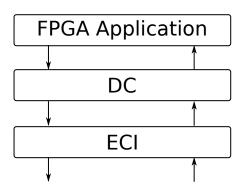

|   | 3.4 | CCKit   | protocol layers                                                            | 45 |

|   |     | 3.4.1   | Two components of a protocol layer                                         | 47 |

|   |     | 3.4.2   | DC protocol state machine design space on Enzian                           | 48 |

|   | 3.5 | Summ    | ary                                                                        | 48 |

| 4        | Dir                                                | ectory                           | Protocol Modeling and Specification                     | 49 |  |  |

|----------|----------------------------------------------------|----------------------------------|---------------------------------------------------------|----|--|--|

|          | 4.1                                                | Introduction                     |                                                         |    |  |  |

|          | 4.2                                                | Direct                           | ory Protocol Model                                      | 52 |  |  |

|          | 4.3                                                | Rules                            | of CPU-DC Interaction                                   | 54 |  |  |

|          |                                                    | 4.3.1                            | Rules of event reordering by the interconnect           | 56 |  |  |

|          | 4.4                                                | Coher                            | ence Messages                                           | 57 |  |  |

|          |                                                    | 4.4.1                            | Coherence message classes                               | 64 |  |  |

|          | 4.5                                                | Memo                             | ry Transactions, Events and Message Classes             | 66 |  |  |

|          | 4.6 Specifying Coherence Transactions              |                                  | ying Coherence Transactions                             | 67 |  |  |

|          |                                                    | 4.6.1                            | State equation representation of coherence transactions | 67 |  |  |

|          |                                                    | 4.6.2                            | Specification of coherence transactions                 | 68 |  |  |

|          |                                                    | 4.6.3                            | Effect of scrambler on state equations                  | 69 |  |  |

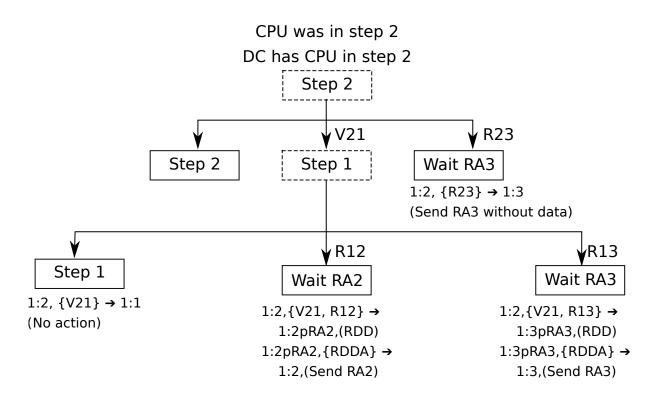

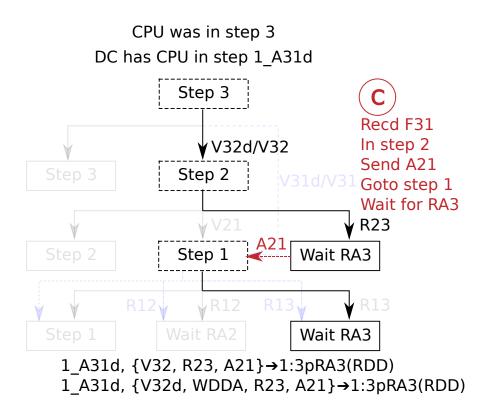

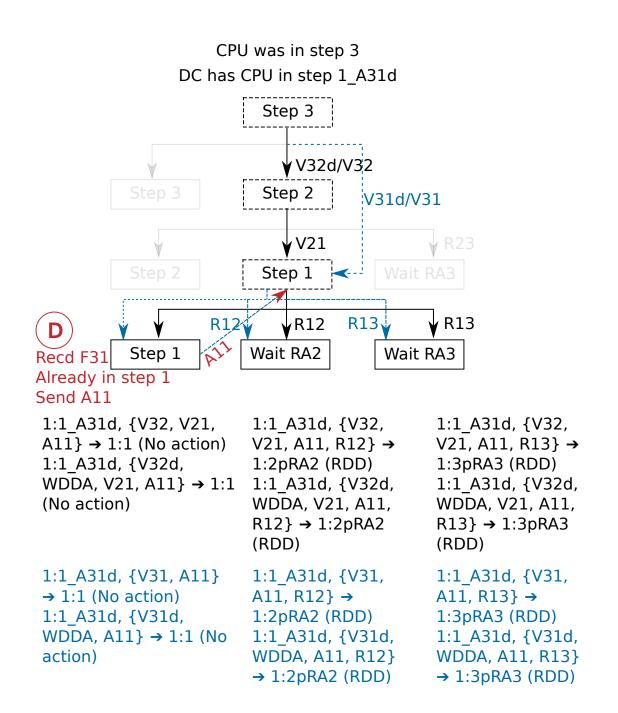

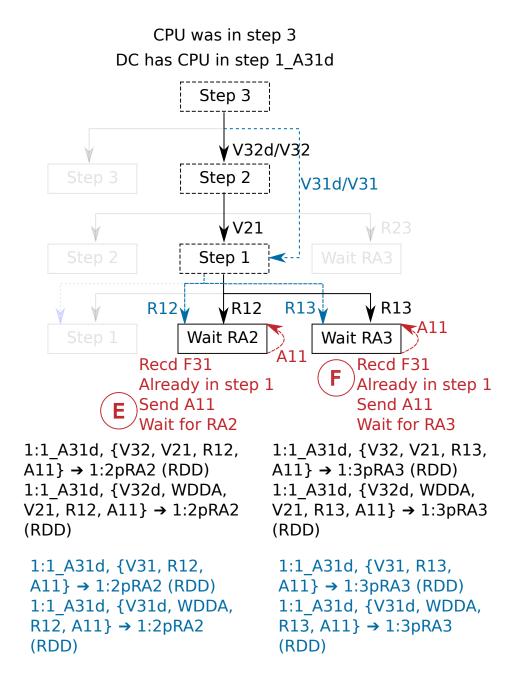

|          |                                                    | 4.6.4                            | DC protocol state machine design choices                | 71 |  |  |

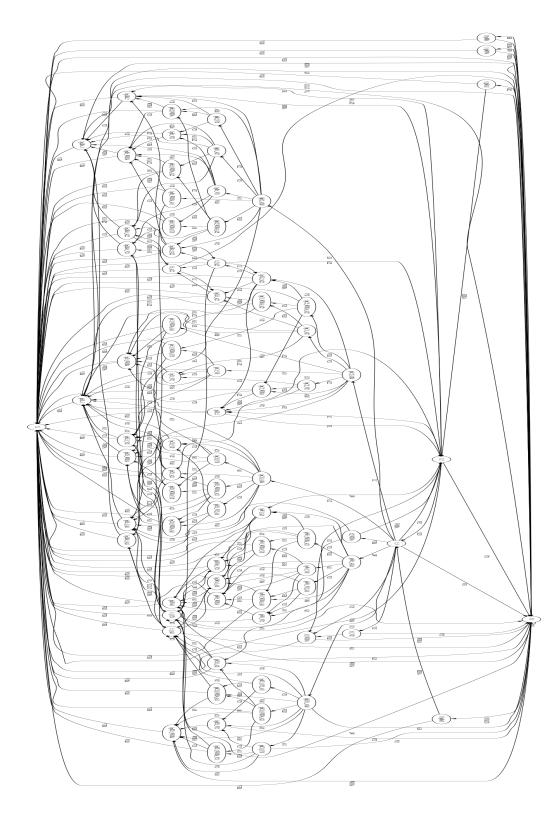

|          | 4.7                                                | State                            | Space Exploration Tool                                  | 73 |  |  |

|          |                                                    | 4.7.1                            | Operators on state equations                            | 73 |  |  |

|          |                                                    |                                  | 4.7.1.1 Substitution operator                           | 75 |  |  |

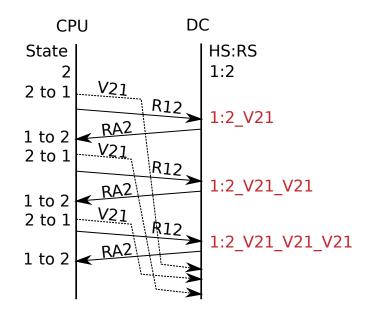

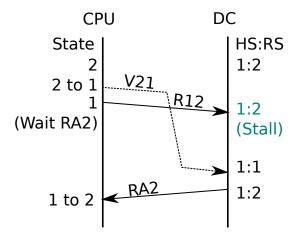

|          |                                                    |                                  | 4.7.1.2 Stall operator for reordering state equations   | 78 |  |  |

|          |                                                    |                                  | 4.7.1.3 Create operator to create intermediate state    | 79 |  |  |

|          | 4.8                                                | Summ                             | nary                                                    | 80 |  |  |

| <b>5</b> | Specifying Coherence Transactions Initiated by CPU |                                  |                                                         |    |  |  |

|          | 5.1                                                | Introd                           | luction                                                 | 81 |  |  |

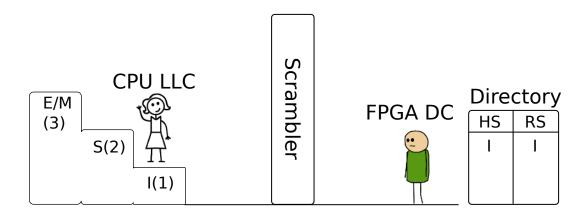

|          | 5.2                                                | Initial Conditions               |                                                         | 83 |  |  |

|          | 5.3                                                | Maintaining Coherence Invariants |                                                         |    |  |  |

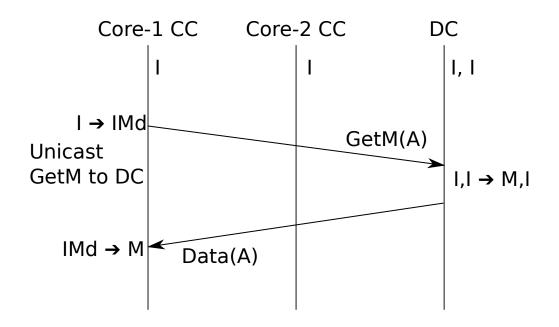

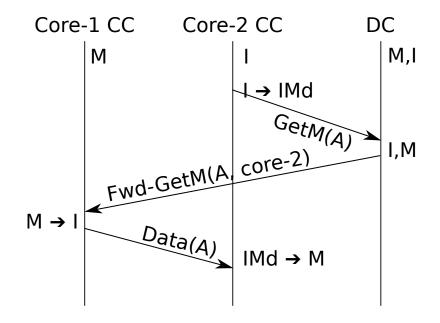

|          | 5.4                                                | 4 CPU State: I, DC State: I:I    |                                                         |    |  |  |

|          |                                                    | 5.4.1                            | CPU pathways                                            | 84 |  |  |

|          |                                                    | 5.4.2                            | Specification and maintaining coherence invariants      | 85 |  |  |

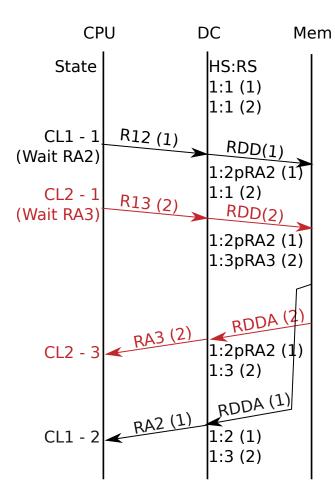

|          |                                                    | 5.4.3                            | Reordering effects and maintaining coherence invariants | 87 |  |  |

|   |            | 5.4.4                                                                           | Building the state machine                                                                                                                                                                                                                                                                         |

|---|------------|---------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | 5.5        | CPU S                                                                           | State: I, DC State: I:S                                                                                                                                                                                                                                                                            |

|   |            | 5.5.1                                                                           | CPU pathways                                                                                                                                                                                                                                                                                       |

|   |            | 5.5.2                                                                           | Specification and maintaining coherence invariants                                                                                                                                                                                                                                                 |

|   |            | 5.5.3                                                                           | Reordering effects and maintaining coherence invariants 94                                                                                                                                                                                                                                         |

|   |            | 5.5.4                                                                           | Building the state machine                                                                                                                                                                                                                                                                         |

|   | 5.6        | CPU s                                                                           | state: E, DC State: I:E                                                                                                                                                                                                                                                                            |

|   |            | 5.6.1                                                                           | CPU pathways                                                                                                                                                                                                                                                                                       |

|   |            | 5.6.2                                                                           | Specification and maintaining coherence invariants                                                                                                                                                                                                                                                 |

|   |            | 5.6.3                                                                           | Reordering effects and maintaining coherence invariants 105                                                                                                                                                                                                                                        |

|   |            | 5.6.4                                                                           | Building the state machine                                                                                                                                                                                                                                                                         |

|   | 5.7        | Summ                                                                            | ary                                                                                                                                                                                                                                                                                                |

| 6 | Spe        | aifuina                                                                         | coherence Transactions Initiated by DC 117                                                                                                                                                                                                                                                         |

| 0 | -          |                                                                                 | •                                                                                                                                                                                                                                                                                                  |

|   | 6.1        | Introd                                                                          | uction $\ldots \ldots \ldots$                                                                                                                                                      |

|   | 6.2        | Forwa                                                                           | rd-Downgrade Transactions                                                                                                                                                                                                                                                                          |

|   |            |                                                                                 |                                                                                                                                                                                                                                                                                                    |

|   | 6.3        |                                                                                 | Conditions                                                                                                                                                                                                                                                                                         |

|   | 6.3<br>6.4 | Initial                                                                         | -                                                                                                                                                                                                                                                                                                  |

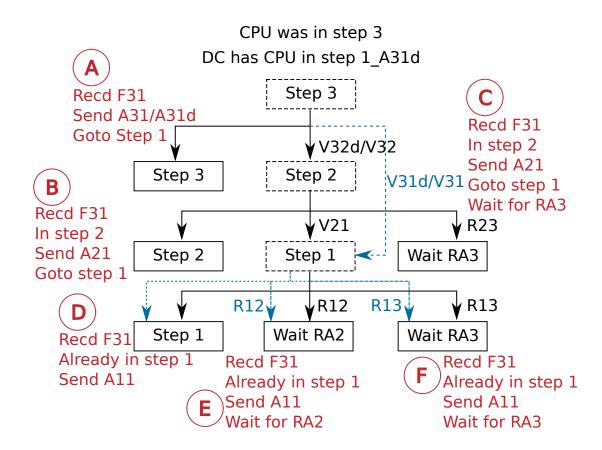

|   |            | Initial                                                                         | Conditions                                                                                                                                                                                                                                                                                         |

|   |            | Initial<br>DC St                                                                | Conditions                                                                                                                                                                                                                                                                                         |

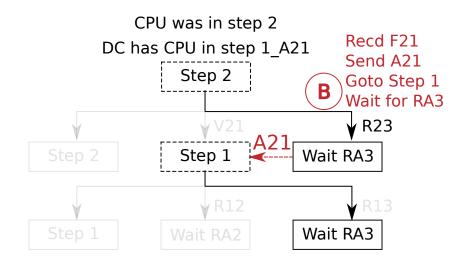

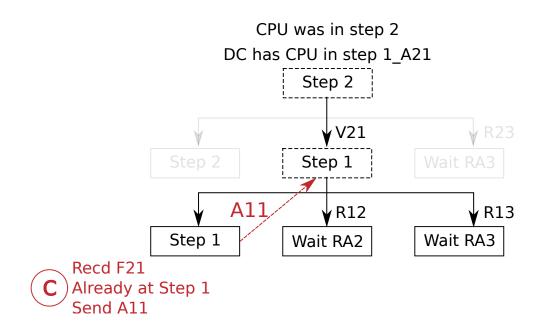

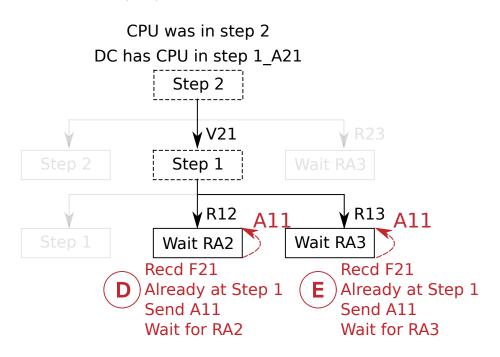

|   |            | Initial<br>DC St<br>6.4.1                                                       | Conditions       119         sate: I:S, DC Issues F21       119         CPU pathways       120                                                                                                                                                                                                     |

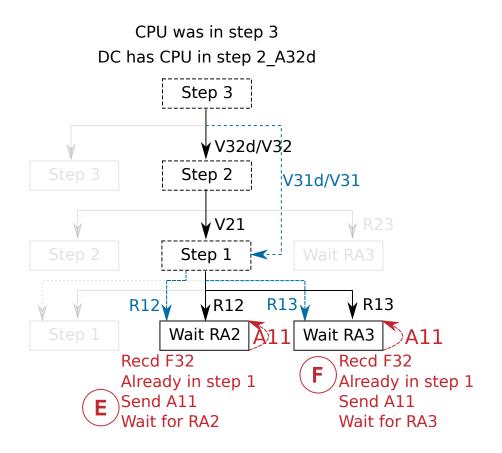

|   |            | Initial<br>DC St<br>6.4.1<br>6.4.2<br>6.4.3                                     | Conditions       119         sate: I:S, DC Issues F21       119         CPU pathways       120         Specification and maintaining coherence invariants       125                                                                                                                                |

|   | 6.4        | Initial<br>DC St<br>6.4.1<br>6.4.2<br>6.4.3                                     | Conditions       119         cate: I:S, DC Issues F21       119         CPU pathways       120         Specification and maintaining coherence invariants       125         Building the state machine       127                                                                                   |

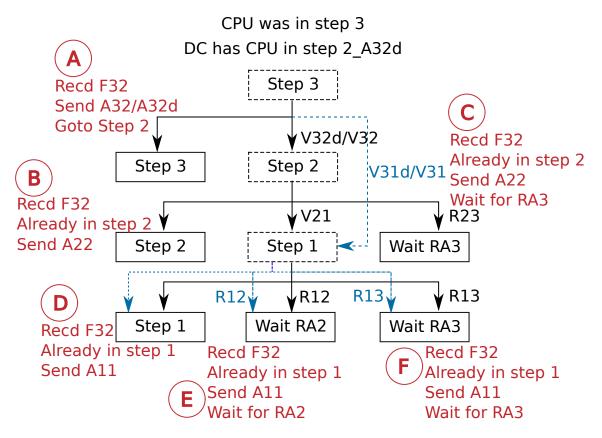

|   | 6.4        | Initial<br>DC St<br>6.4.1<br>6.4.2<br>6.4.3<br>DC St                            | Conditions119cate: I:S, DC Issues F21119CPU pathways120Specification and maintaining coherence invariants125Building the state machine127cate: I:E, DC Issues F32127                                                                                                                               |

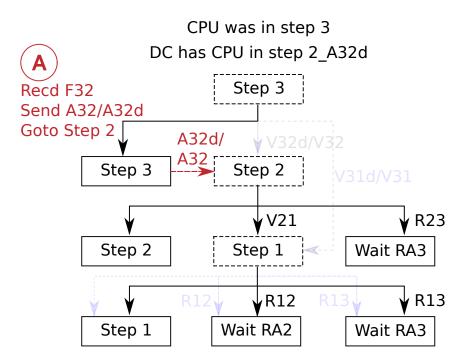

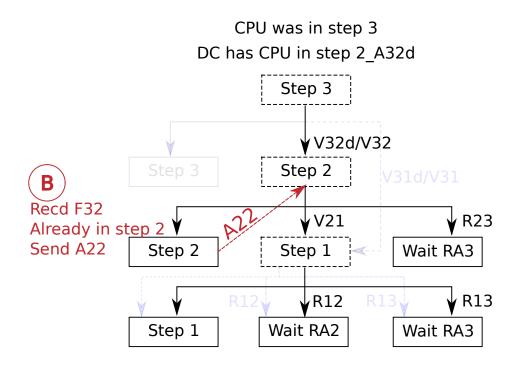

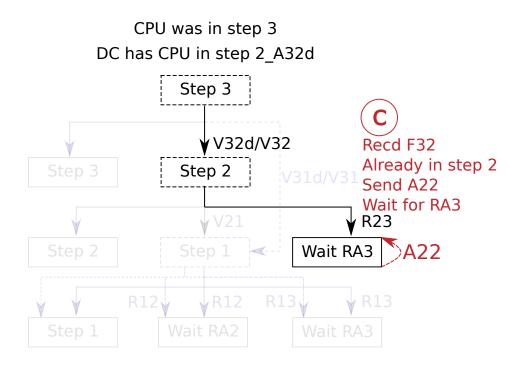

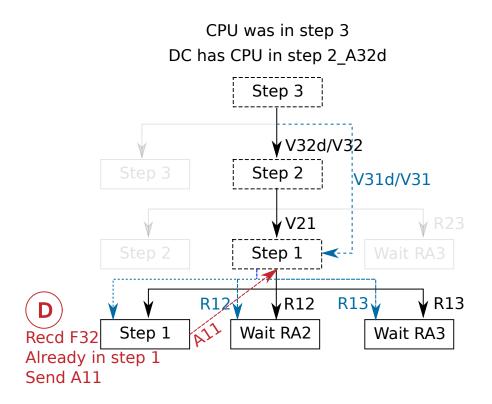

|   | 6.4        | Initial<br>DC St<br>6.4.1<br>6.4.2<br>6.4.3<br>DC St<br>6.5.1                   | Conditions119cate: I:S, DC Issues F21119CPU pathways120Specification and maintaining coherence invariants125Building the state machine127cate: I:E, DC Issues F32127CPU pathways128                                                                                                                |

|   | 6.4        | Initial<br>DC St<br>6.4.1<br>6.4.2<br>6.4.3<br>DC St<br>6.5.1<br>6.5.2<br>6.5.3 | Conditions119sate: I:S, DC Issues F21119CPU pathways120Specification and maintaining coherence invariants125Building the state machine127sate: I:E, DC Issues F32127CPU pathways128Specification and maintaining coherence invariants128                                                           |

|   | 6.4        | Initial<br>DC St<br>6.4.1<br>6.4.2<br>6.4.3<br>DC St<br>6.5.1<br>6.5.2<br>6.5.3 | Conditions119cate: I:S, DC Issues F21119CPU pathways120Specification and maintaining coherence invariants125Building the state machine127cate: I:E, DC Issues F32127CPU pathways128Specification and maintaining coherence invariants128Building the state machine136Building the state machine139 |

| <b>7</b> | Spe  | cifying                                          | Coherence Transactions Initiated by Applications                       | 143 |  |  |

|----------|------|--------------------------------------------------|------------------------------------------------------------------------|-----|--|--|

|          | 7.1  | 7.1 Introduction                                 |                                                                        |     |  |  |

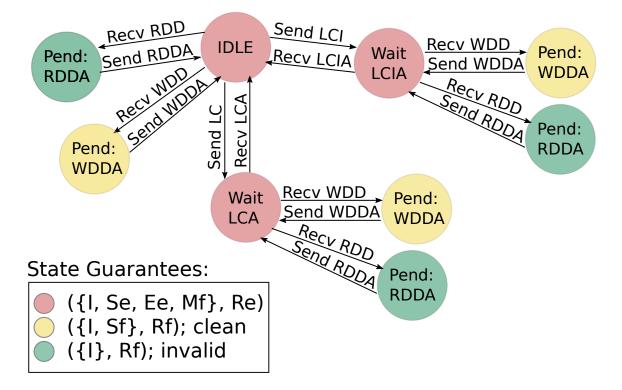

|          | 7.2  | Local Coherence Transactions                     |                                                                        |     |  |  |

|          | 7.3  | Local Coherence Messages                         |                                                                        |     |  |  |

|          | 7.4  | Local Coherence Message Classes                  |                                                                        |     |  |  |

|          | 7.5  | .5 Specification of Local Coherence Transactions |                                                                        |     |  |  |

|          |      | 7.5.1                                            | Effective remote state                                                 | 150 |  |  |

|          | 7.6  | Guara                                            | ntees Provided at DC's Application Interface                           | 150 |  |  |

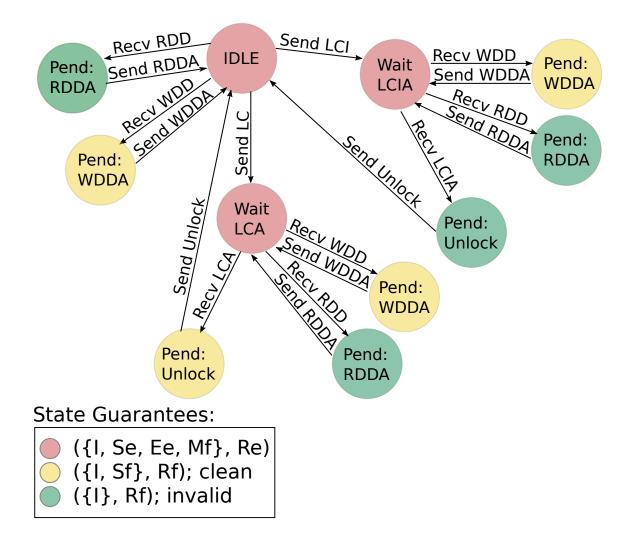

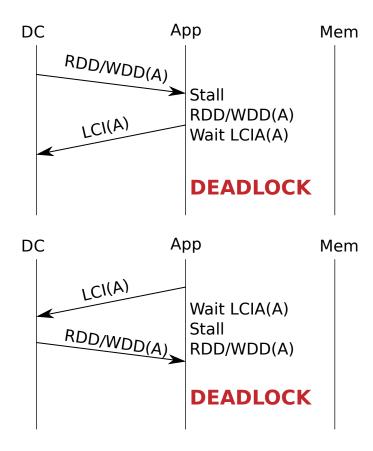

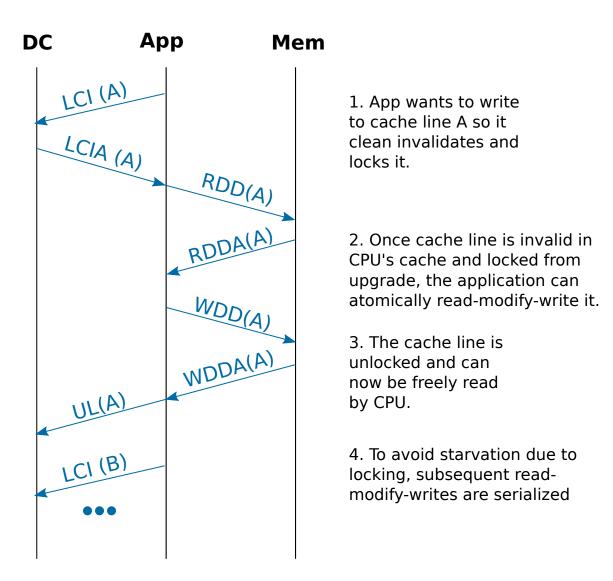

|          | 7.7  | Modify                                           | ving DC's Application Interface For Locking Capabilities               | 153 |  |  |

|          |      | 7.7.1                                            | Local coherence messages for locking capabilities                      | 154 |  |  |

|          |      | 7.7.2                                            | Local coherence message classes for locking capabilities               | 154 |  |  |

|          |      | 7.7.3                                            | Specification of local coherence transactions for locking capabilities | 155 |  |  |

|          |      | 7.7.4                                            | Guarantees provided at DC's modified application interface             | 156 |  |  |

|          |      | 7.7.5                                            | Starvation in the modified DC interface                                | 156 |  |  |

|          | 7.8  | Applic                                           | ation Layer on top of DC Protocol Layer                                | 158 |  |  |

|          | 7.9  | Directo                                          | bry Maintenance Operations                                             | 161 |  |  |

|          |      | 7.9.1                                            | Specification of ICI transaction                                       | 162 |  |  |

|          | 7.10 | Miscel                                           | laneous Local Coherence Transactions                                   | 163 |  |  |

|          | 7.11 | Local                                            | Events Packet Formats                                                  | 163 |  |  |

|          |      | 7.11.1                                           | LC and LCI request packet formats                                      | 163 |  |  |

|          |      | 7.11.2                                           | LCA and LCIA responses packet formats                                  | 165 |  |  |

|          |      | 7.11.3                                           | Unlock (UL) response packet format                                     | 165 |  |  |

|          | 7.12 | Summ                                             | ary                                                                    | 166 |  |  |

| 8        | Dist | ribute                                           | d Directory Controller                                                 | 169 |  |  |

|          | 8.1  | Introd                                           | uction                                                                 | 169 |  |  |

|          | 8.2  | DC Int                                           | terfaces                                                               | 170 |  |  |

|          | 8.3  | Overvi                                           | ew of DC Architecture                                                  | 172 |  |  |

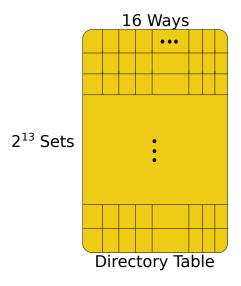

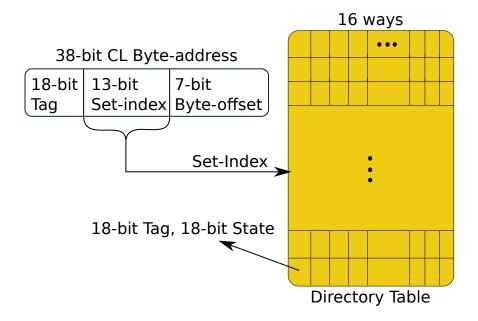

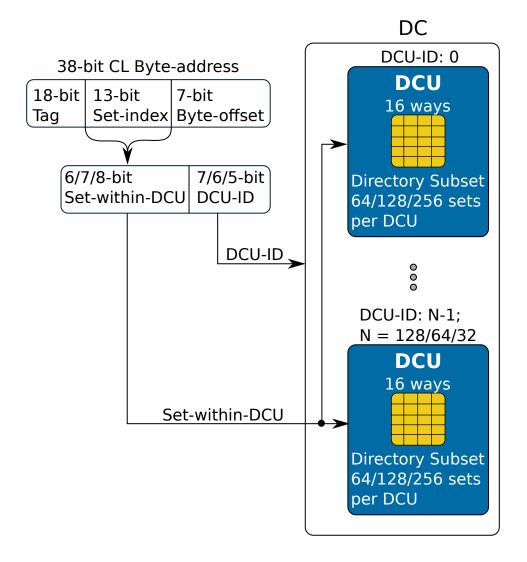

|     | 8.3.1   | DC directory sizing                                                                                  |

|-----|---------|------------------------------------------------------------------------------------------------------|

|     | 8.3.2   | Indexing into the DC directory                                                                       |

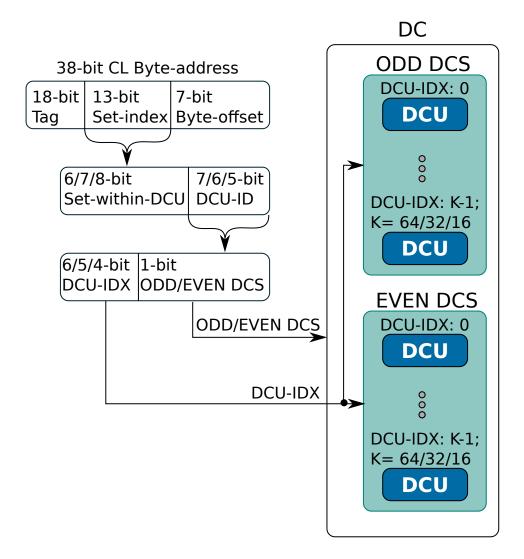

|     | 8.3.3   | Directory controller units and slices                                                                |

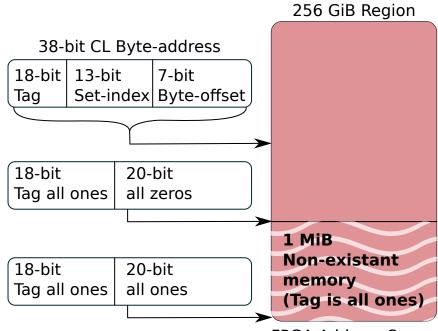

|     | 8.3.4   | Non-existent memory in address space exposed by DC 178                                               |

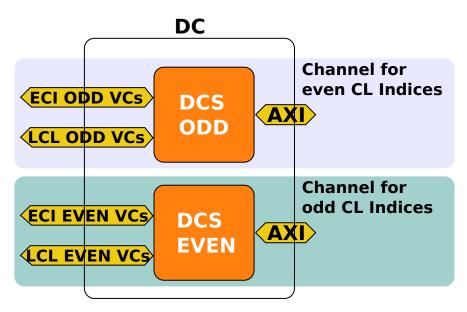

|     | 8.3.5   | DC architecture top level                                                                            |

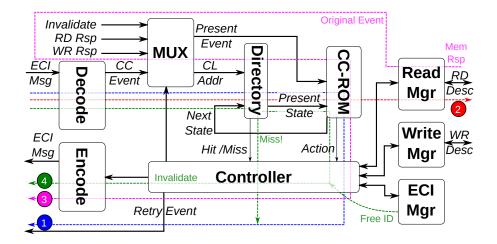

| 8.4 | Direct  | ory Controller Slice (DCS) Architecture                                                              |

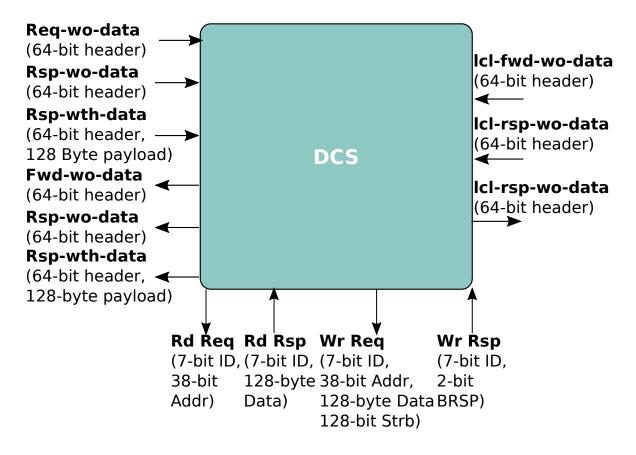

|     | 8.4.1   | DCS interface                                                                                        |

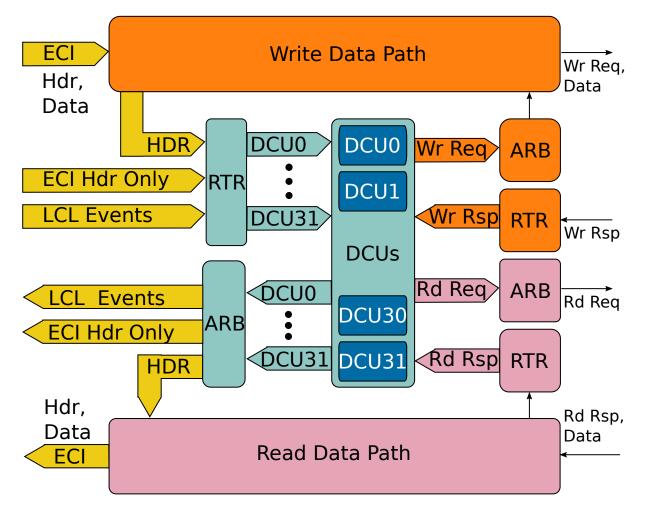

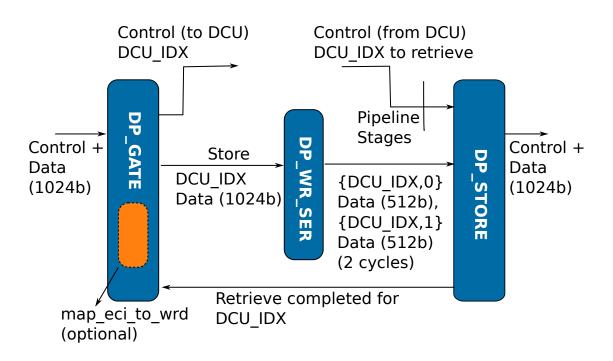

|     | 8.4.2   | DCS control and data-paths                                                                           |

|     | 8.4.3   | Memory descriptor interface to AXI interface                                                         |

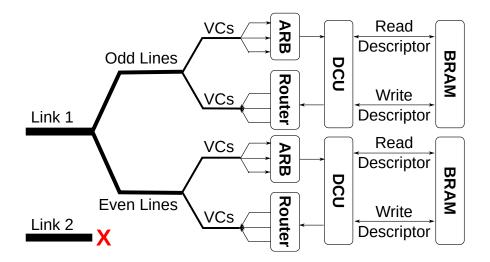

|     | 8.4.4   | Saturating ECI transmit bandwidth                                                                    |

|     | 8.4.5   | Saturating ECI receive bandwidth                                                                     |

| 8.5 | Direct  | ory Controller Unit (DCU) Architecture                                                               |

|     | 8.5.1   | Interface and basic operation                                                                        |

|     | 8.5.2   | Design considerations                                                                                |

|     | 8.5.3   | DCU interface with DCS                                                                               |

|     | 8.5.4   | Design of DCU                                                                                        |

|     | 8.5.5   | Protocol scenarios and DCU pathways                                                                  |

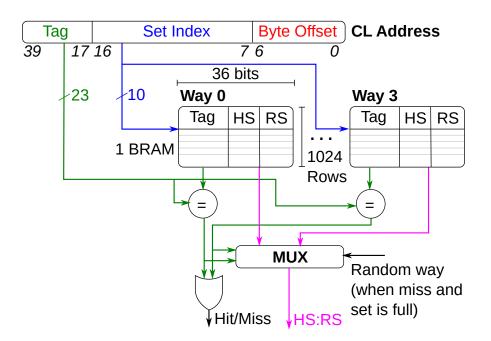

|     | 8.5.6   | Design of DCU's directory: Tag State Unit (TSU)                                                      |

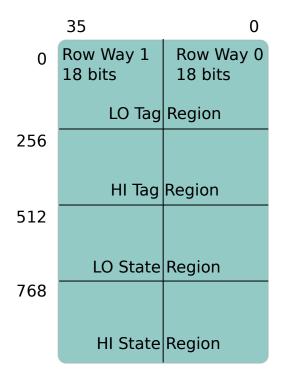

|     |         | 8.5.6.1 Tag state ram (TSR)                                                                          |

|     |         | 8.5.6.2 Why non-existent memory $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 202$ |

|     |         | 8.5.6.3 Building TSU with TSRs                                                                       |

|     |         | 8.5.6.4 Optional registering outputs of TSR                                                          |

| 8.6 | Custor  | mizing the Protocol State Machine                                                                    |

| 8.7 | Summ    | ary                                                                                                  |

| Eve | luation | n & Applications 207                                                                                 |

|     |         |                                                                                                      |

| 9.1 |         |                                                                                                      |

| 9.2 | Interfa | acing FPGA Application to DC                                                                         |

9

|              | 9.3  | Advan   | tages of symmetric protocols over asymmetric protocols $\ldots \ldots \ldots$                    | 210 |

|--------------|------|---------|--------------------------------------------------------------------------------------------------|-----|

|              | 9.4  | DC Ca   | ache Line Addressing                                                                             | 211 |

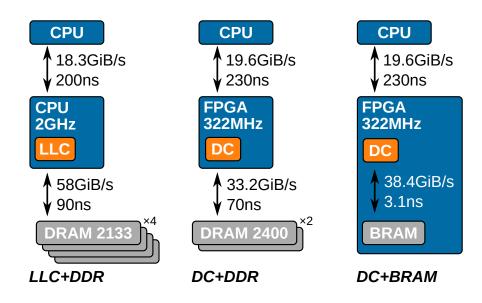

|              | 9.5  | Perform | mance Evaluation of CCKit's DC                                                                   | 212 |

|              |      | 9.5.1   | Implementation details                                                                           | 212 |

|              |      | 9.5.2   | Experimental setup                                                                               | 212 |

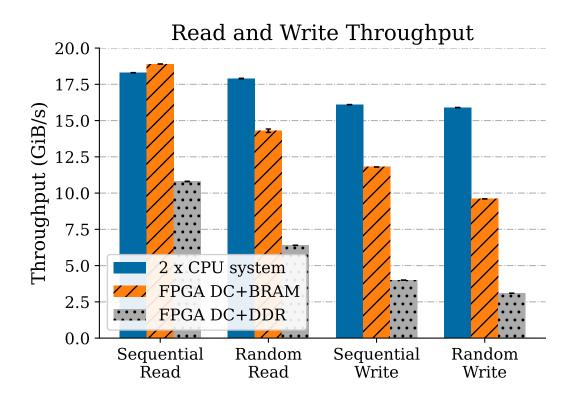

|              |      | 9.5.3   | Directory Controller (DC) read-write throughput and latency                                      | 214 |

|              |      | 9.5.4   | DC clean-invalidate throughput and latency                                                       | 216 |

|              | 9.6  | Applic  | ations                                                                                           | 218 |

|              |      | 9.6.1   | Steps to consider when developing applications                                                   | 218 |

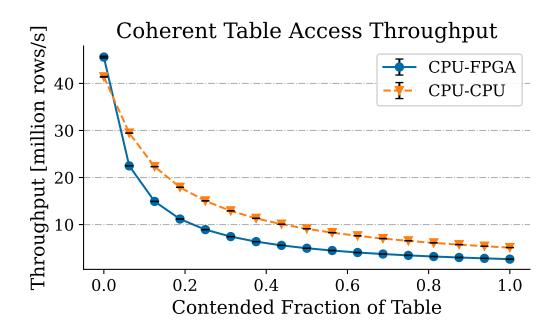

|              |      | 9.6.2   | Concurrent access to shared data structures                                                      | 220 |

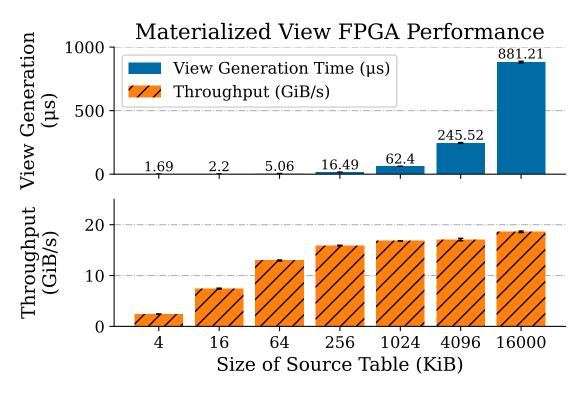

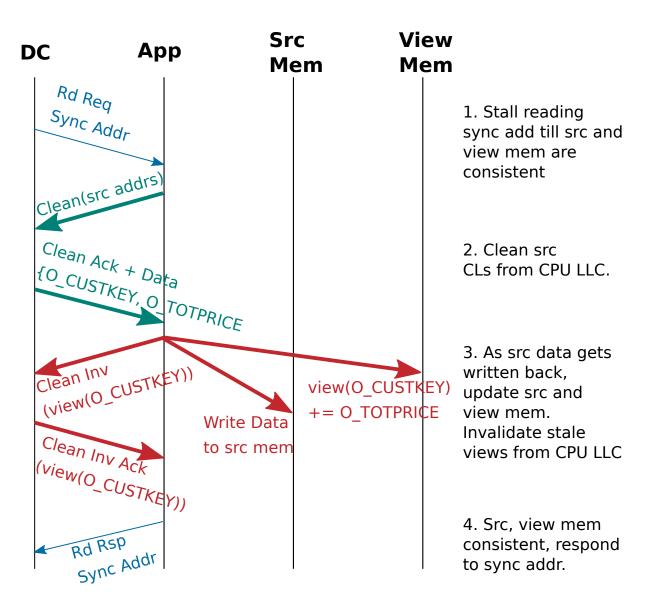

|              |      | 9.6.3   | Maintenance of materialized database views                                                       | 221 |

|              |      | 9.6.4   | Implementation details                                                                           | 225 |

|              | 9.7  | Summ    | ary                                                                                              | 228 |

| 10           | Com  | clusior |                                                                                                  | 220 |

| 10           |      |         |                                                                                                  | 229 |

|              |      |         | ary                                                                                              |     |

|              | 10.2 |         | ions for Future Work                                                                             |     |

|              |      | 10.2.1  | Fixing issues with the current work                                                              | 231 |

|              |      | 10.2.2  | Formally specifying and verifying the protocol                                                   | 232 |

|              |      | 10.2.3  | Relaxing fundamental design choices                                                              | 232 |

|              |      | 10.2.4  | Explore applications                                                                             | 232 |

| $\mathbf{A}$ | Mis  | cellane | ous Specifications and State Diagrams                                                            | 233 |

|              |      |         |                                                                                                  |     |

| В            | Not  |         | tributed Directory Controller                                                                    | 243 |

|              | B.1  | Introd  | uction $\ldots$ | 243 |

|              |      | B.1.1   | Insights                                                                                         | 244 |

|              | B.2  | DC Ar   | chitecture                                                                                       | 245 |

|              |      | B.2.1   | Directory Controller Unit (DCU)                                                                  | 246 |

|     | B.2.2  | Directory implementation       | 248 |

|-----|--------|--------------------------------|-----|

|     | B.2.3  | Action handlers implementation | 250 |

| B.3 | Perfor | mance and Resource Consumption | 251 |

# Introduction

There is increasing interest in extending cache coherence, long regarded as essential for parallel programming on homogeneous multiprocessors, to other parts of a computer system and in opening up hardware coherence protocols for other uses. The main trend driving this renewed interest in coherence protocols is the rise of heterogeneous hardware in the form of Systems-on-Chip (SoCs), and accelerators such as GPUs, FPGAs, TPUs, etc. Such a shift in hardware design is in turn driven by performance scaling [CCP<sup>+</sup>16, FPM<sup>+</sup>18], parallel machine learning workloads [CFO<sup>+</sup>18], and specialization [TS21]. When a computer is a collection of heterogeneous processing elements of equal standing, the question arises as to how much of the system should be coherent.

The proliferation of accelerators has also driven innovation in the interconnects linking them to the CPU. Because PCI Express (PCIe) lacks the necessary features to support increasingly sophisticated and powerful accelerators, new proposals like CCIX [CCI19], GenZ [Gen20], and OpenCAPI [SSI<sup>+</sup>18] emerged. These have now converged and been merged into CXL [CXL20a] which seems to have become the agreed upon standard for future interconnects. Similar, more specialized developments exist for GPUs (NVIDIA NVLink [FD17, LSC<sup>+</sup>20], AMD's Infinity Fabric [BWPN18]), and RISC-V processors and embedded systems (TileLink [Ber22]). Interestingly, all these efforts provide cache coherence and/or coherent memory access in ways unavailable before. While traditional coherence used proprietary interconnects between parts from a single vendor, it is now closer in spirit to network protocols (see, e.g., [LBH<sup>+</sup>23]). These emerging interconnects enable innovative architectural designs exploiting coherence, such as disaggregated memory [CIP<sup>+</sup>21] or crash consistency for persistent memory [BTP<sup>+</sup>22]. Some even argue that cache coherence protocols should be tailored to the application [MHEH<sup>+</sup>19, ZGK<sup>+</sup>21] rather than offered as a black box. However, this requires the tools and sufficiently high-level interfaces to allow applications to interact with the hardware cache protocol. Working with coherence protocols, even those designed with interoperability in mind, is highly challenging. Real coherence protocols are complex, with hundreds of transient states and many potential race conditions [NSHW20a]. Implementing a coherent endpoint as part of an application is difficult and time-consuming. Reusing an implementation is even harder, particularly when the protocol is being used non-traditionally.

Simulation fares poorly in these scenarios: either the simulator is painfully slow, making it hard to derive meaningful results in the presence of I/O and real-world interactions, or it achieves better performance by simplifying the protocol, potentially losing critical, real-world practical issues.

To address this, we present CCKit, an open-source, server-grade, modular, reusable, and highly flexible coherence protocol design and implementation. We focus on Field Programmable Gate Arrays (FPGAs) as their reconfigurable nature is ideal both for exploring the design space and meeting the performance requirements of CPU interaction at such a low level. Many of the proposals taking advantage of coherent interconnects are based on FPGAs [CPK<sup>+</sup>19, CIP<sup>+</sup>21, BTP<sup>+</sup>22] and some compare already patenting use-cases based on cache coherent FPGAs [CGKS20a, CGKS20b]. FPGAs are also a standard component in the cloud (Microsoft [PCC<sup>+</sup>14], Amazon [Ama23], Alibaba [CLL<sup>+</sup>18]), with novel applications in, e.g., acceleration of database engines [ZWC<sup>+</sup>20, PMR<sup>+</sup>23] that would greatly benefit from using a cache coherent FPGA.

Prototyping with CCKit is fast and faithful: its first implementation already runs natively on a real hardware platform [CRS<sup>+</sup>22], and includes a performant coherence implementation matching the speed of the CPU. CCKit is also flexible: it exposes to applications much more about protocol events than emerging standards do. Crucially, it is also much easier to use, abstracting most of the state machine complexity of the real coherence protocol while still exposing enough low-level access to allow a wide range of use-cases. To ensure flexibility, CCKit is built as an intermediate layer between the raw coherency messages delivered from the interconnect and the application logic and offers high level and well-defined interfaces, making it portable to future standards providing symmetric coherence such as CXL 3.0.

We show the performance and versatility of CCKit through micro-benchmarks and a range of acceleration use cases. The former demonstrate that CCKit on an FPGA has performance in the same range as a CPU, despite the lower clock frequency on the FPGA. Our use cases explore (a) the implementation of a custom pre-fetcher on the FPGA (doubling the throughput when reading the FPGA memory from the CPU versus no pre-fetching, 17.4 GiB/s vs. 7.8 GiB/s for 4 threads); (b) the maintenance of database views with update propagation from base tables to an aggregated view (running at the interconnect speed of 19.5 GiB/s); and (c) synchronous RPC from CPU to FPGA based on the CCKit directory controller that outperforms both programmed I/O and Direct Memory Access (DMA) with a null RPC time of 1.2  $\mu$ s.

## **1.1** Background and Motivation

In this section we briefly discuss the hardware trends behind CCKit to pose the two questions we aim to answer with this thesis. First, how to explore the design space of coherent accelerators without the limitations of simulation – essentially, how to *implement* FPGA applications that interact with a CPU over a coherent interconnect? Second, by taking a wider perspective on the integration of accelerators in the overall architecture, what is the appropriate application *interface* to this interconnect from FPGAs?

#### 1.1.1 Symmetric vs. asymmetric protocols

A crucial aspect in cache coherence protocols is who controls the protocol. In this regard, models of cache coherence broadly fall into two categories [NSHW20b].

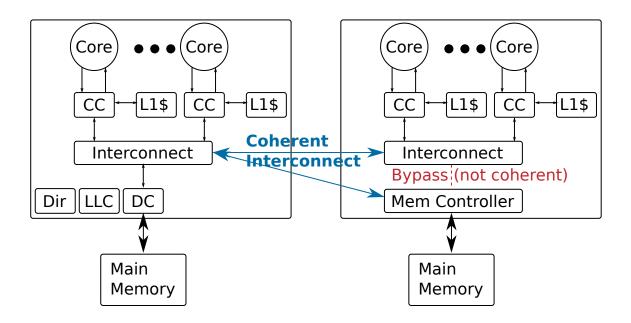

Asymmetric protocols preserve the host-device relationship between CPU and accelerator: both sides can implement caching agents (and cache data), but only the CPU implements a home agent which tracks ownership of cache lines. This simplifies accelerator implementation but limits scalability and flexibility as well as significantly affecting performance: to access areas of its local memory marked as shared with the CPU, an accelerator must make a request to the CPU. The rationale is that, in the common case, data is copied in bulk to the accelerator in advance of computing on it, as with traditional GPUs (see below). In such a model, the underlying idea is that the data in the accelerator is, from the start, a copy and there is no notion of the accelerator actually owning data that the CPU could be caching as well.

In contrast, *symmetric* protocols have home agents on both CPU and accelerator, essentially as in a homogeneous NUMA system. While more complex to implement, they provide seamless integration between the CPU and accelerator as full coherence protocols. Less obviously, they also allow the accelerator to participate in the protocol in more unconventional ways. Rather than just observing transactions on the CPU cache and be notified of these actions by the CPU, the accelerator can actively generate its own notifications and manage its own memory independently. More details can be found in subsection 2.5.1.

Most of the protocols used to date in accelerators are asymmetric. While CCKit can also support them, our main goal is to support symmetric protocols as they are more powerful and open up far more possibilities. Symmetric protocols also seem to be the direction in which current standards are going, making CCKit the first readily available stack that can be used as a means to explore cache coherence in accelerators in general and *symmetric coherence* in particular, as well as a tool to exploit cache coherence at the application level.

#### 1.1.2 The evolution of interconnects

Until recently, accelerators like GPUs used a "host-device" computational model based on PCIe where the host CPU manages external accelerator resources. Data is offloaded in bulk for processing and the results copied back to the host. This is the model used by CUDA [NBGS08], OpenCL [SGS10], and modern accelerators such as TPUs [JYP<sup>+</sup>17] and VCUs [RSC<sup>+</sup>21]. It arose in part from the lack of cache coherence between host and device, and favors highly structured workloads that can be expressed as offloaded batches. This model implicitly assumes the accelerator takes a copy of the input data, performs a task, and returns results without engaging in any complex exchange or interaction with the CPU [OSC<sup>+</sup>11].

As accelerators have become more powerful (in some cases, many CPUs are needed to feed a single accelerator [ZAB<sup>+</sup>22]) the lack of PCIe bandwidth has led to better PCIe standards with much higher bandwidths. However, the underlying principals of PCIe have remained unchanged, despite its limitations in terms of protocol and features, and the proliferation and diversity of accelerators emerging recently.

Early attempts at better ways to integrate accelerators into the system were Intel HARPv2 [OSC<sup>+</sup>11] and IBM CAPI [SBJS15], which coherently connected a server-class CPU and

FPGA. HARPv2 used an *asymmetric* implementation of the symmetric QuickPath Interconnect (QPI) protocol [Cor09] in contrast to other approaches available at the time [WMW<sup>+</sup>16], while CAPI used a PCIe Host Bridge and Coherent Accelerator Processor Proxy on the CPU, and a service layer on the FPGA. In both cases the protocol is asymmetric and closed: the application on the FPGA has only limited access and control over the coherency protocol.

More recent developments in more modern interconnects include the Cache Coherent Interconnect for Accelerators (CCIX) [CCI19] which supports a symmetric protocol by extending PCIe, and OpenCAPI [SSI<sup>+</sup>18] which implements an asymmetric protocol over PCIe and Bluelink. Both require accelerators to work with caching enabled and use virtual addresses, translated by the CPU's MMU. Performance studies of FPGAs attached using CCIX [TSK+22] have emphasized the importance of cache coherence in heterogeneous architectures involving FPGAs. Compute Express Link (CXL) [CXL20a] builds coherence and memory semantics above PCIe and, to date, provides a unified coherent memory space between CPU and accelerators using an asymmetric protocol with coherence bypass for direct access to unshared device memory. These standards were developed in closelyguarded industrial settings, and are evolving rapidly, having largely converged on CXL. At the time of writing, the first CXL 1.1 hardware is becoming available. Symmetric coherence is planned for CXL 3.0 [SA22], and the advent of the specification has already triggered interesting ideas around what it will allow, based on simulations that promise impressive throughput and latency, as well as extensibility beyond one machine [LBH<sup>+</sup>23, MWD<sup>+</sup>23]. However, it remains unclear when suitable 3.0 hardware will appear, and CXL retains a somewhat prescriptive position on the use of cache coherence messages.

#### 1.1.3 Coherence in MPSoCs

Alongside these developments in server architecture, processors have started to evolve towards more eclectic and less monolithic designs using *chiplets* and SoC architecture as the basis for more powerful processors.

The most mature and broadly adopted coherent CPU-FPGA systems combine both on a single Multiprocessor System-on-chip (MPSoC), such as Xilinx Zynq UltraScale+ [Xil22b] and Intel Agelix [Int20]. This simplifies the physical interconnect, and provides both coherent and non-coherent ports between CPU and FPGA. Coherent access is generally asymmetric: the FPGA can access the CPU's Last Level Cache (LLC). This tightly-

engineered integration significantly limits both application flexibility and available CPU performance, the norm being simple dual or quad-core ARM processors aimed at embedded systems rather than servers.

RISC-V's TileLink takes a more general approach [Ber22, Ter17, CTL17], aimed at lowlatency connectivity between CPUs, caches, accelerators, memory, and other SoC components. TileLink comprises three protocols (increasing in functionality): Uncached Lightweight (TL-UL), Uncached Heavyweight (TL-UH), and Cached (TL-C), and a number of coherence *policies* which can be subsets of the MOESI protocol (MESI, MEI, MSI, etc.). Multi-socket coherence can be achieved with TileLink-over-Ethernet (TLoE) with OmniXtend [RTLV19]. While TileLink targets the on-chip memory hierarchy [Ber22] and implementations for high-end server CPUs and accelerators (including FPGAs) have yet to appear, TileLink shows a clear response to the demand for customizable coherent interconnects in increasingly heterogeneous systems, a demand also observed by others [MHEH<sup>+</sup>19, ZGK<sup>+</sup>21, GSL<sup>+</sup>22].

#### 1.1.4 FPGA operating systems

A final motivation for CCKit is recent work on operating systems for FPGAs. Coyote [KRA20], Optimus [MZL<sup>+</sup>20], AmorphOS [KLP<sup>+</sup>18], Feniks [ZXX<sup>+</sup>17], and ViTAL [ZL20] provide, to varying degrees, spatial and temporal multiplexing of FPGA resources (including externally-attached memory) between applications implemented in user logic, memory translation, and other services such as networking. They all target PCIe-based accelerator cards, and so adopt a DMA-based approach to copying the contents of memory to and from the FPGA. This works well for traditional GPU-style application acceleration, but rules out both the straightforward use of cache coherence between FPGA and CPU, and the flexibility afforded to applications which have direct access to the coherence protocol.

CCKit rectifies this, as a potential *component* of an FPGA OS which implements cache coherence memory access to both FPGA and CPU memory, and as a critical OS *abstraction* to make coherence protocols accessible to developers of heterogeneous CPU-FPGA applications. It also exposes limitations of existing operating systems when dealing with modern accelerators (subsection 1.2.5).

## 1.2 Approach and Design

CCKit allows FPGA applications to interact directly with a cache coherence protocol in a more flexible way than assumed by simple coherence, hiding most of the protocol's complexity. It therefore provides a portable interface for application logic to coherently access memory alongside the CPU and also, crucially, to interact with the CPU's LLC. Behind this interface, we show an efficient, deadlock-free, and scalable design providing access to the full address space while maintaining coherence invariants.

A key idea in CCKit is to factor out as much of the complexity of the coherence protocol into scalable re-usable units (part of the CCKit toolkit). The design is, in principle, applicable to a range of hardware platforms, but any implementation will be specific to a particular CPU, coherence protocol, and platform. The first implementation of CCKit is based on the Enzian platform [CRS<sup>+</sup>22] (section 3.3).

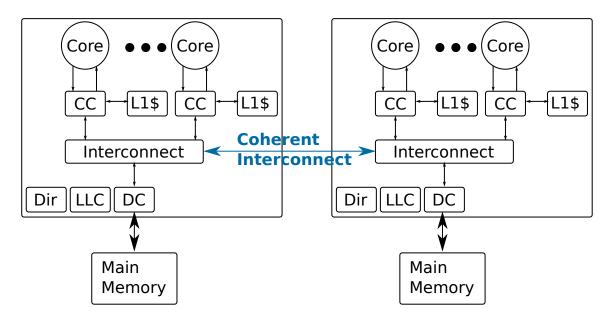

## 1.2.1 Target platform and assumptions

CCKit makes fairly relaxed assumptions about the underlying hardware. We target 2-node systems where one node is a conventional multicore CPU, and the other is an FPGA, and a MOESI-like directory-based write-invalidate cache coherence protocol connects the two. Physical address space is partitioned between the two nodes (i.e. high-order bits of the physical address determine the node where the memory is accessed). CCKit assumes an architecture-specific layer on the FPGA side which exchanges coherence messages with the CPU, guaranteeing delivery but not order, and deadlock freedom.

These assumptions are reasonable: most modern coherent multi-socket systems adopt a directory-based [Tan76, CF78] approach rather than less-scalable, broadcast-based *snoop-ing* [RG83] protocols. In directory-based systems every cache line has a "home" node, i.e. the location for storing both the line data in main memory and the directory data on where the cache line is held and in what states [NSHW20b]. Write-invalidate protocols include the well-known MSI, MESI, MOESI, MOSI, and Intel MESIF, and most modern systems implement a variant of MOESI, supporting cache-to-cache transfers and multiple, consistent-but-dirty copies of data. More details on target platforms and assumptions are discussed in subsection 3.2.1.

In practice, race conditions, message reordering by the interconnect, and concurrency

mean that real implementations have many more hidden, intermediate states than the five textbook MOESI states, greatly complicating the protocol [NSHW20b]. More that than 100 states is not unusual in a multi-socket system, and this complexity is even cited as an argument for using asymmetric protocols or no coherency at all in connecting an FPGA and CPU [CXL20b]. CCKit stands as evidence against this, providing a full symmetric protocol implementation that (as we show in subsection 9.5.3) keeps pace with the native CPU implementation.

#### **1.2.2** Coherence protocol specification

Implementing CCKit requires the full coherence protocol to be specified (indeed, we generate the state machine from a formal specification of the protocol), but within these constraints on hardware the interface provided by CCKit to user logic is completely independent of the protocol details.

The coherence protocol on Enzian is the CPU's native coherence protocol which is proprietary and its specification is not available to us. To overcome this, we reverse engineered the coherence protocol from traces and developed a model of the coherence protocol. Using this model, we were able to identify coherence transactions and develop a specification of the CPU's native coherence protocol. We then expanded this specification to also include the interface provided to user-logic. Then we built a *state space exploration tool* that takes in this specification to generate the coherence protocol.

The advantage of this methodology is that the specification of the coherence protocol as well as the interface to the user logic can be changed easily and a new state machine, with the modified specifications, can be automatically generated using the state space exploration tool.

#### 1.2.3 High-level architecture

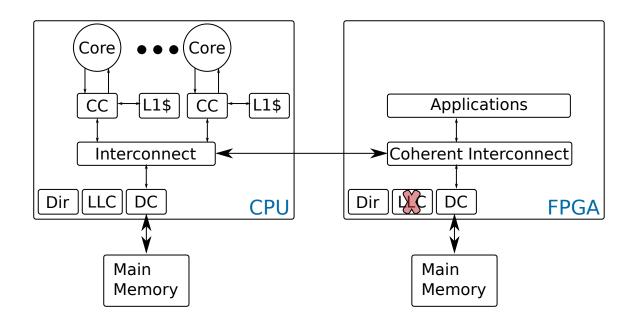

CCKit distinguishes between the case where a cache line is homed on the FPGA or on the CPU. In neither case does CCKit actually cache the line itself – this is left as a choice to the application logic. Instead, CCKit abstracts the complexity of the protocol, timing, and state machine maintenance and presents a simplified interface to the FPGA application. In the FPGA-homed case, a DC component maintains the directory information for a line, including the local protocol state and the state it believes the line to be in on the CPU.

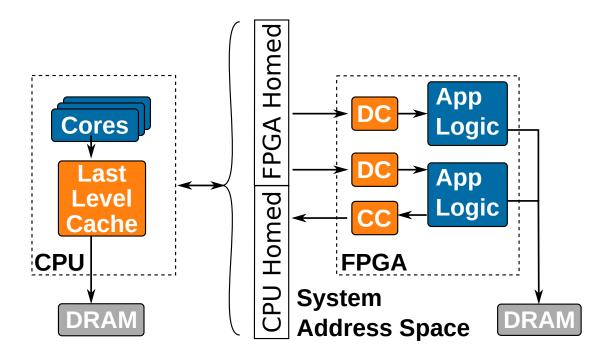

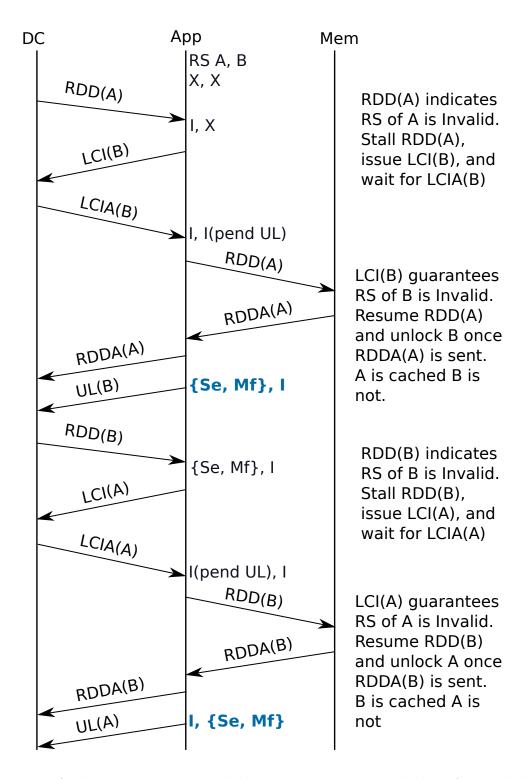

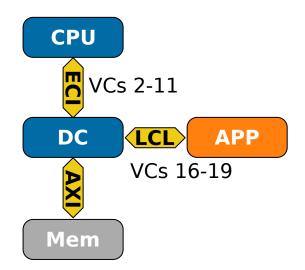

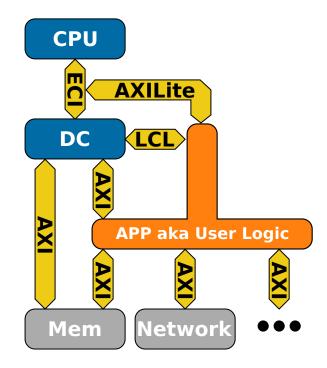

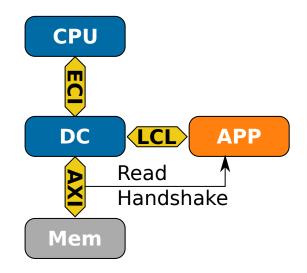

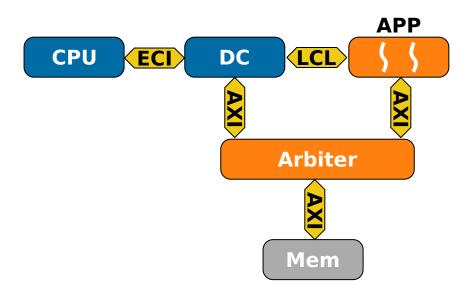

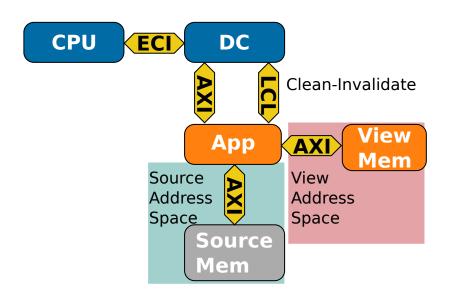

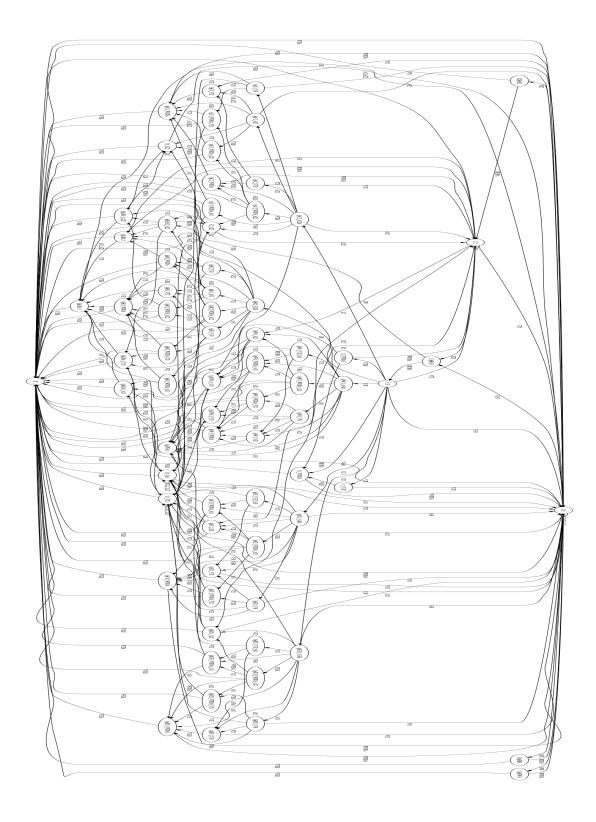

Figure 1.1: CCKit architecture.

The CPU-homed case is handled similarly by a Cache Controller (CC) component on the FPGA. Since CCKit does not perform any caching *per se*, the CC is much simpler than the DC, and is to some extent a subset of its functionality. We therefore concentrate on the DC in this thesis; all applications in chapter 9 use the DC.

Figure 1.1 shows the high-level architecture. Each DC or CC is responsible for a different region of the physical address space. By varying the number of units, performance can be traded off against FPGA resources and flexibility (since different units can be configured with variants of the protocol end-point) This mirrors the behavior of a CPU LLC, except that in a CPU the controllers' parameters are hardwired (the only "application" to be supported is the cache itself) thus it makes sense to completely integrate all functionality into the LLC controller.

#### 1.2.4 FPGA-side interface

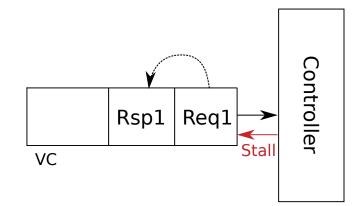

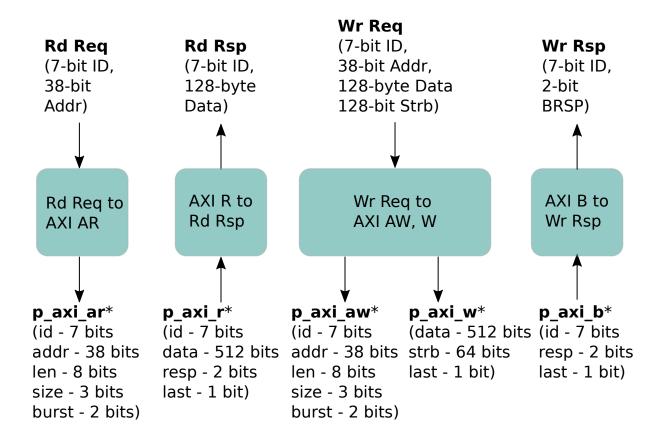

All request and response messages originating on the CPU and referring to FPGA-homed coherent addresses are routed to a DC, which tracks the state of all lines held on the CPU and initiates and responds to MOESI transactions (e.g. upgrade/downgrade) on behalf of the rest of the FPGA. The interface to the remainder of the FPGA logic is much sim-

#### Chapter 1. Introduction

pler: An Advanced eXtensible Interface (AXI) interface for reads and writes (to service upgrade and downgrade requests, respectively), plus a request-acknowledge interface allowing FPGA logic to trigger a clean (write-back without invalidate) or clean+invalidate operation on the CPU's LLC. In the simplest implementation, the AXI interface can be connected directly to the FPGA-side DRAM controllers to provide coherent read/write access to FPGA-side DRAM from the CPU. Most non-trivial applications will instantiate their own logic between these two components to interact with the coherent interconnect (chapter 9).

The request-acknowledge interface to FPGA application and the directory protocol are generated from a machine-readable specification and can be configured easily. This can be used to tailor the protocol and interface. Using CCKit, an FPGA programmer does not have to track the state of individual cache lines and can rely on the messages observed at CCKit's interface to infer certain guarantees. For example, an application observing an AXI read request for a cache line can infer that the cache line is invalid in the CPU's cache and the FPGA memory has the most up-to-date copy. Similarly, an AXI write request, when observed, guarantees the cache line is either Invalid or Shared in the CPU's cache but never Exclusive or Modified. Applications that do not require interacting with the request-acknowledge interface can rely on these guarantees provided by the AXI interface. For interactions with the request-acknowledge interface, in the simplest version of the protocol, applications can issue clean and clean-invalidate requests for cache lines and rely on messages observed in both acknowledge and AXI channels to perform what is required (subsection 9.6.3).

Changing the directory protocol can provide additional guarantees for the application, simplifying its design. For example, the application described in subsection 9.6.2 requires a cache line to be invalid in the CPU's cache until the application modifies it and releases control. For this, we generated a version of the protocol where the application can lock a cache line upon performing a clean or clean-invalidate, and we added an additional interface channel for applications to unlock cache lines. This locking mechanism prevents the CPU from upgrading a cache line thereby guaranteeing its state when the request is acknowledged. It also guarantees that the FPGA memory has the most up-to-date value. The cache line remains in this state until the application relinquishes control using an unlock message issued to the DC. This simplifies the application design by moving a part of its state machine into the DC.

By having a more flexible message format at the request-acknowledge interface can reduce

the state that needs to be maintained by applications by packing information that would be required to handle request-acknowledge transactions, as part of the request. For example, if the application needs to store and retrieve a certain (nominal) value when handling request-acknowledge transactions, the value can be embedded into the request and received as part of the acknowledgment.

#### 1.2.5 CPU-side interface

The CCKit interface to software is, compared to FPGA user logic, relatively simple: coherence is mostly transparent to software on the CPU, and what explicit cache operations there are on the CPU (flush, invalidate, etc.) simply translate into coherence messages.

The main functionality CCKit exposes to software is the ability to map part of the physical address space serviced by DCs into the virtual address space of a process. We support this in Linux via a kernel module which creates a device for the FPGA's memory space. This can be mapped into a process address space using mmap().

While the MMU can achieve this trivially, assumptions in the Linux memory management implementation introduce challenges. In CCKit we want super-page mappings for efficiency, and because fine-grained translation does not really benefit FPGA applications. We also want the page mappings to be set up eagerly in advance to avoid, for example, prefetch hints from the CPU being ignored by the cache controller because the prefetch would cause a page fault. Unfortunately, both the MAP\_HUGETLB flag to mmap to request large pages and the MAP\_POPULATE flag to create mappings in advance only apply to memory that the kernel believes to be RAM [BK22], which is not the case here. Essentially Linux so far has no notion of memory that should be treated as RAM for mapping into virtual address space, but not for anything else. For this reason, CCKit bypasses the standard in-kernel interfaces for page mapping for now. The design of better (CPU-side) OS support for heterogeneous memory is ongoing work.

#### **1.2.6** CCKit acceleration model

The acceleration model in PCIe-based non-coherent CPU-FPGA platforms typically uses the FPGA as offload accelerators. The source data that is to be processed is DMA'd into the FPGA and the results are DMA'd back to the CPU. This requires the source and result pages to be marked as non-cacheable since PCIe protocol does not have a coherence layer.

Coherent CPU-FPGA platforms limits user logic on the FPGA to perfroming load and store operations through a CC, just like cores on the CPU. This limits the observability and interaction of FPGA applications with the coherence protocol and targets to accelerate applications that benefit due to "fine-grained" interaction between CPU and FPGA ([CCF<sup>+</sup>16]) where both nodes are accessing a shared address space. This model of acceleration is possible using CCKit (see subsection 9.6.2).

A different acceleration model that is made possible by CCKit is where user logic on the FPGA can transparently extend the notion of coherence for software running on the CPU. As will be seen in chapter 2, coherence protocols maintain coherence of each cache line (cache line) independently. That is coherence transactions on one cache line is not affected by coherence messages on another cache line. In CCKit, the FPGA application can make interesting associations between unrelated cache lines by observing coherence transactions on one set of cache lines to cause coherence traffic on a different set of cache lines (an example is shown in subsection 9.6.3). Thus in CCKit's acceleration model, applications on FPGA interact with the coherence protocol through the DC to transparently provide certain coherence and consistency guarantees to software on the CPU.

## 1.3 Related Work

As discussed in section 1.1, there is growing interest in new models of coherence and applications benefiting from coherence.

Researchers have demonstrated the need for non-standard or even dynamically customized coherence protocols. For example, Cohmeleon demonstrates that, for different types of accelerators, the best performing cache coherence protocol varies at runtime [ZGK<sup>+</sup>21]. Similarly, CoNDA demonstrates the benefits of finer-grained coherence, and proposes a more customizable protocol to increase efficiency and performance [BGP<sup>+</sup>19].

FPGAs have been used to optimize a number of algorithms; many of these could greatly benefit from coherence provided by CCKit. For example, FPGAs have been used to efficiently balance a tree data structure [ZWC<sup>+</sup>20]. The addition of cache coherence would allow for concurrent access during rebalancing without the need for external signaling or explicit data transfers. Similarly, many features of Alibaba's OLTP X-Engine [HCW<sup>+</sup>19] could benefit from customizable cache coherence protocols, including the operators explored in chapter 9.

The movement towards data center disaggregation raises questions on how to handle the additional complexity of new memory tiers. Both POND [LBH<sup>+</sup>23] and TPP [MWD<sup>+</sup>23] are built around CXL, but are primarily interested in the near-NUMA latency of the interconnect and not coherence per se. However, others have demonstrated the utility of fine-grained cache coherence in disaggregated systems [CIP<sup>+</sup>21, LYT<sup>+</sup>21]. For example, MIND advocates a flexible cache coherence protocol integrated into the network [LYT<sup>+</sup>21]. Clio argues that customizable, application-accessible coherence is desirable in these systems for limiting coherence overhead [GSL<sup>+</sup>22].

SmartNICs often employ FPGAs to accelerate common networking tasks such as RPC calls [LXA<sup>+</sup>21] or RDMA [SWC<sup>+</sup>20, YHS<sup>+</sup>23]. These systems provide significant improvement, but the addition of coherence using techniques provided by CCKit could provide added benefit. For example, in Dagger, coherence could allow the use of low-latency synchronization primitives instead of complex application-level interactions [LXA<sup>+</sup>21]. StRoM, when ported to CCKit, could enable RDMA atomic operations by directly manipulating the cache using customizable cache coherence. Rambda proposes several architectural changes for accelerating memory-intensive applications which are centered around accelerator coherence [YHS<sup>+</sup>23].

A complete discussion of cache coherence simulators is beyond the scope of this section (see [BKP20] for a more thorough discussion). There is no doubt that simulation tools (e.g. ZSim [SK13], gem5 [BBB<sup>+</sup>11], or CMP\$im [JCLJ08]) are essential for the development of protocols and architectures. However, simulating a real application with these tools is slow, and often simulators trade off architectural fidelity and accuracy for speed. To evaluate the low-level correctness of controllers and protocols, RTL simulations are often necessary, requiring HDL descriptions of the CPU, interconnect, and accelerator which are seldom available to researchers. Even if these models are available, cutting-edge cycle accurate simulators run in the scale of kHz [Ver, EKK<sup>+</sup>23], making the simulation of complex systems and applications under real workloads nearly impossible.

CCKit complements these techniques by providing a real-world implementation that can faithfully interact with not only real hardware (e.g. off-chip memory, accelerators) and software, but as a part of a networked or rack-scale system.

## **1.4** Contributions

In this section, we try to address the wider implications of CCKit beyond Enzian. One of the aims of CCKit is to be platform agnostic: the principles of CCKit should be applicable to any symmetric coherent platform that implements a directory-based MOESI like coherence protocol. To achieve this, we take a layered approach when modeling CCKit. We identify the set of services and abstractions each layer has to provide for the layer on top to build upon.

Furthermore, we separate out the coherence protocol modeling and the protocol state machine generation from its implementation. The modeling and state machine generation are platform-agnostic which makes the design principles of CCKit applicable to any symmetric coherent platform, whereas the implementation is tailored to the characteristics of the target platform for maximum performance (Enzian in our case). We also show that it is possible to have a performant implementation of the home-agent on the FPGA even if it operates at a much lower frequency when compared to the CPU.

Finally, we define a simplified and platform-agnostic interface for applications to interact with the coherence protocol. This interface aims to provide high controllability and observability for applications to the coherence protocol while simplifying its interaction. Through this interface we explore both traditional and non-traditional acceleration models that are enabled by CCKit. Thus the contributions of this thesis are as follows.

- 1. A generic model for directory protocol and a state space exploration tool that generates a platform agnostic directory protocol state machine for CCKit.

- 2. A customizable, performant and platform specific implementation of CCKit's directory protocol state machine on the FPGA, tailored to Enzian.

- 3. An abstract interface to the directory protocol for applications to interact with.

- 4. Exploring traditional and non-traditional acceleration models using CCKit.

# 1.5 Structure of the Dissertation

Chapter 2 provides an introduction to cache coherence. It shows the baseline system models for different types of coherence protocols like snooping and directory based protocols and extends it to provide the baseline system model for Enzian. It also goes into detail on a number of fundamental design choices that were made before building the coherence stack on the FPGA.

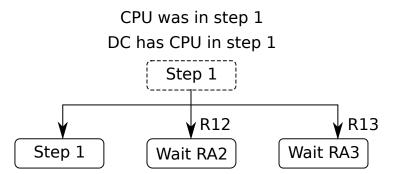

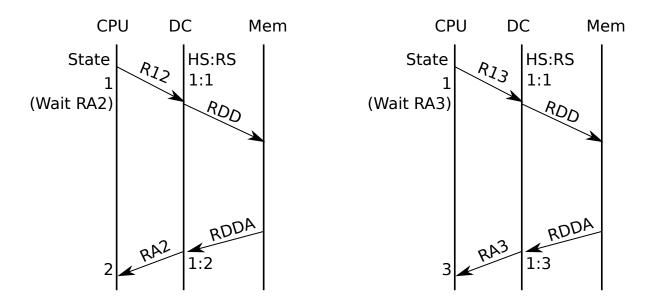

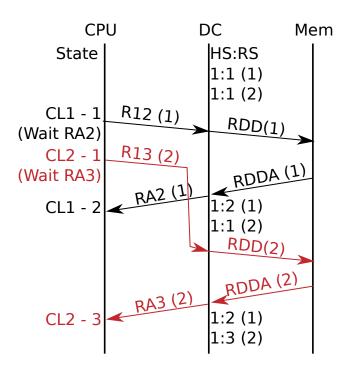

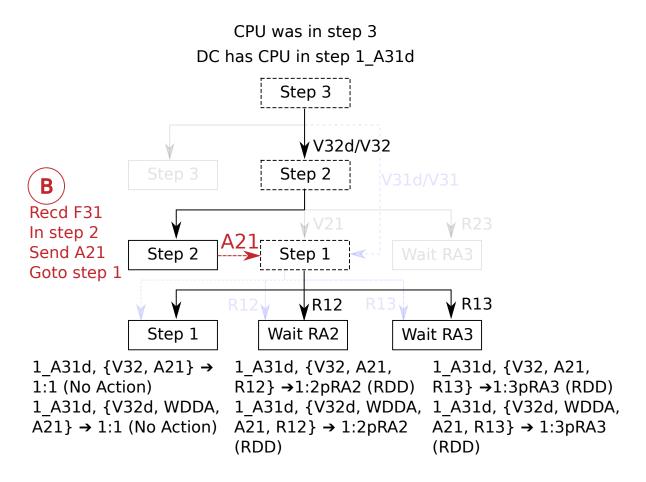

Chapter 4 describes the model of DC protocol that was developed by reverse engineering the CPU's native coherence protocol. In the absence of a formal specification of the CPU's native protocol, this model is used to identify transactions that need to be handled by the DC and build a specification. This chapter introduces *state equations* as a way of specifying the protocol and describes how these state equations can be *solved* to generate a state machine with intermediate states necessary to carry out the DC protocol.

Chapter 5 uses the DC protocol model to identify and specify coherence transactions that would allow the CPU to coherently access the FPGA attached memory. It also provides design choices and an algorithm for a state space exploration tool that solves the specification state equations to generate a DC protocol state machine automatically.

Chapter 6 extends the specification by including the state equations of coherence transactions that are generated by the DC and incorporates them in the protocol state machine.

Chapter 7 further extends the specification by describing the interface exposed by the protocol state machine to applications. It shows examples of how the interface can be customized for different application requirements and uses the state space exploration tool to automatically generate the state machine.

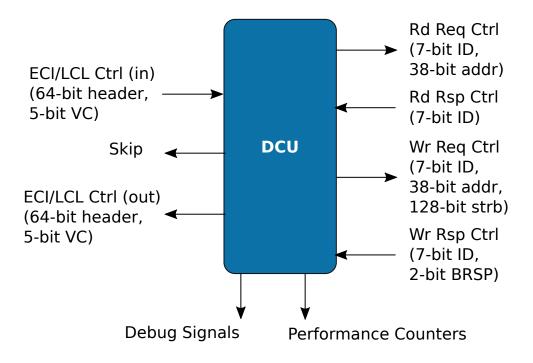

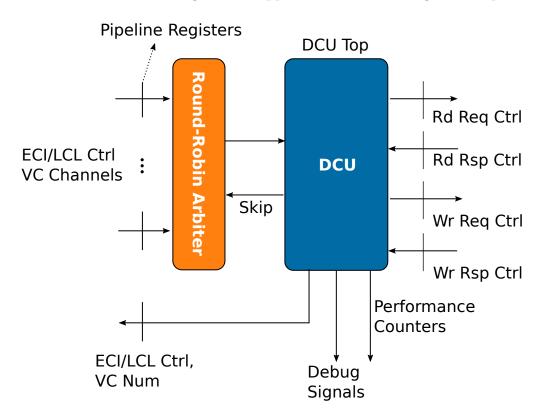

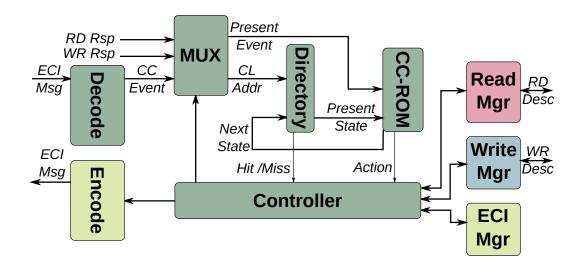

Chapter 8 describes how the DC protocol state machine is implemented on the FPGA. It shows the design choices made to build a customizable and high performance DC that provides a simplified interface to applications. The interfaces and architecture of different components that make up the DC are described in detail.

Chapter 9 focuses on building applications on top of the directory protocol layer. It evaluates the performance of the DC through a number of benchmarks and showcases different ways in which FPGA user logic can be interact with the coherence protocol through the DC when accelerating applications.

If the reader is interested in building applications using the DC, they can focus on chapter 7 to get an idea of DC's application interface, and chapter 9 to understand how the example applications are developed. The reader might also be interested in the figures in Chapter 8 that goes into detail on DC's interface signals.

If the reader is more interested in the specification of the protocol, for they want to formally verify it, or would like to generate a new protocol state machine, they can focus on chapters 5, 6 and 7.

2

# **Primer on Cache Coherence**

# 2.1 Introduction

This chapter summarizes cache coherence from the point of view of Enzian. The description given here is by no means comprehensive. Readers can refer to [NSHW20b] for a more elaborate and formal discussion.

The structure of this chapter is as follows.

- 1. Section 2.2 describes a baseline system without caches and how there is no problem of incoherence in such a system.

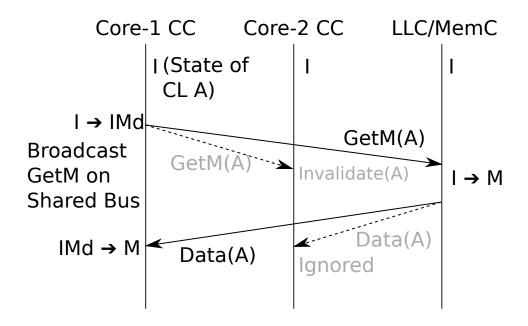

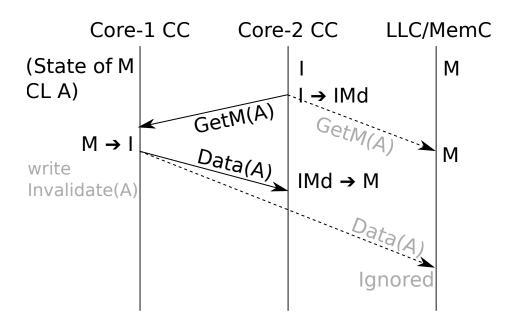

- 2. Section 2.3 describes a baseline system with caches and shows the problem of incoherence. It also details how the problem of incoherence is solved using the coherence protocol. This chapter focuses on snooping based coherence protocol and its disadvantages.

- 3. Section 2.4 shows the baseline system for a directory based protocol and how it solves problems that were present in a snooping based mechanism.

- 4. Section 2.5 details a baseline NUMA system with directory based coherence protocol. The difference between symmetric and asymmetric NUMA systems is also discussed.

- 5. Section 3.3 shows the baseline system model for Enzian and introduces its various components. The layered approach to building a coherence stack on the FPGA is also introduced here.

- 6. Section 3.2.2 describes the fundamental design choices that were made before building the coherence stack.

## 2.2 Baseline Multicore System without Caches

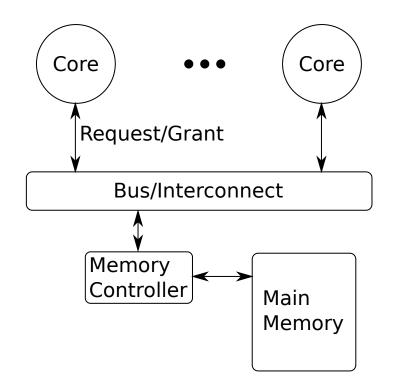

**Figure 2.1:** Baseline model for a multicore system without caches: Multiple cores interact with the main-memory controller through a shared bus.

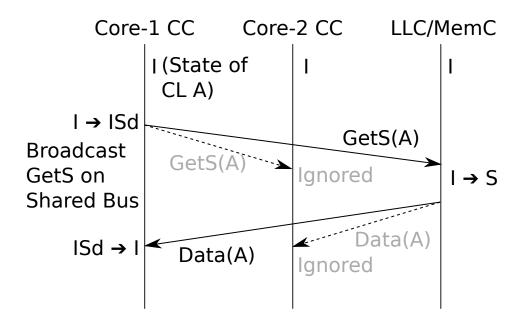

Figure 2.1 shows a simplified multicore system model without any caches. In this model, each core can make a load or store request to the shared bus. The bus uses an arbitration scheme to choose one core and grant access to main memory. The core can then perform its load or store operation directly on the main memory through the memory controller.

This system offers two advantages: first, only one core can write to a memory location at any given time. Second, there is only one copy of the data for a memory location and the most up-to-date data for the memory location resides in the main memory. The drawback of such a system without caches is the quick exhaustion of memory bandwidth by the processor load [TSS88]. To overcome this drawback caches were introduced.

## 2.3 Baseline Multicore System with Caches

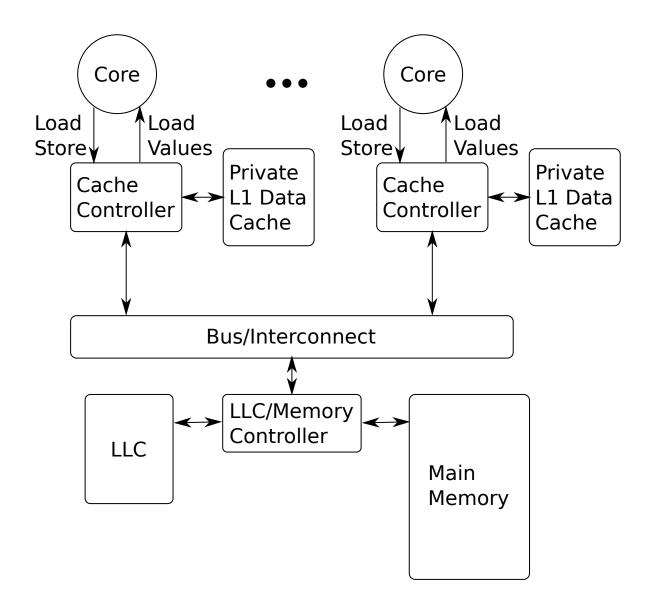

The baseline system model with caches is described in detail in [NSHW20b] and shown in Figure 2.2. In this system, each core has a private level 1 (L1) cache that is accessible through its CC. The cache controller for all cores are connected to a shared bus or interconnect. Then there can be multiple levels of shared caches before the main memory, though for the sake of simplicity, only one is shown in Figure 2.2 called the LLC. The LLC and main memory are both accessible through the LLC/Memory controller. The difference between L1 and LLC caches are that L1 is private to each core whereas LLC is shared among all cores. In this memory hierarchy as the levels increase, the memory access latency also increases with the main memory having the highest access latency. Although this model does not encompass *all* the different flavors of caching systems that exist in modern multicore systems, it is sufficiently representative to introduce the entities that are present in a multicore system with caches.

Whenever a core wants to read a memory location, it issues a *load* request to its L1 CC. The CC then fetches a copy of the memory location from the memory hierarchy and places it in the private L1 cache of that core. The value can then be loaded into a register in the core from the L1 cache. If a core wants to write to a memory location, the core issues a *store* request to its L1 CC, which then fetches the memory location into its private L1 cache before updating it with the store value from the core. Since any update by a core happens in the private L1 cache of that core, it can lead to the problem of incoherence.

#### 2.3.1 Problem of incoherence

Consider two cores core-1 and core-2 with their private L1 caches. Initially core-1 and core-2 both loads the value of a memory location into their private caches. If core-1 modifies its private copy of the memory location in its L1 cache and if this change is not propagated to the copy on core-2, both cores have different values for the same memory location. Furthermore, the main memory also has a copy which can be potentially stale. This is the problem of incoherence which arises in systems with caches.

Figure 2.2: Baseline model for multicore system with caches: Each core has a private cache accessible through a cache controller. Cache controllers communicate with each other and memory controller through a shared bus. The shared bus allows for a snooping based coherence mechanism.

#### 2.3.2 Shared memory consistency

A second issue with the correctness of memory accesses in a multicore system with caches is shared memory consistency. When multiple threads are accessing a shared memory simultaneously, there can be many possible ways how the memory is accessed. Even within a single thread, modern ISAs allow multiple possible interleavings of instructions which can change how the memory gets accessed. In order to account for this variety when writing programs, a programmer needs to know what sort of memory accesses can be expected from a system. A memory consistency model defines the correct shared memory behavior by providing rules about correctness of memory accesses. It separates out all possible correct executions from incorrect alternatives for the programmer. There are different consistency models and executions that are correct in one model might be incorrect in another. [NSHW20b] describes in detail different consistency models such as Sequential Consistency (SC), Total Store Order (TSO) and relaxed memory models.

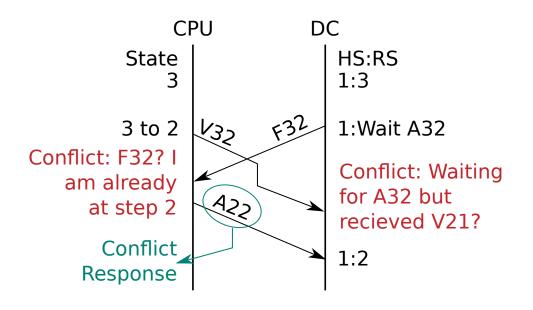

#### 2.3.3 Coherence vs consistency