#### Online Optimizations Using Hardware Performance Monitors

Florian T. Schneider

© Florian T. Schneider, 2009.

DISS. ETH Nr. 18077

### Online Optimizations Using Hardware Performance Monitors

ABHANDLUNG zur Erlangung des Titels

#### DOKTOR DER WISSENSCHAFTEN

der

ETH ZÜRICH

vorgelegt von

Florian Thomas Schneider Dipl. Ing. ETH

geboren am 31. Juli 1979

von Österreich

Angenommen auf Antrag von Prof. Dr. Thomas R. Gross, Referent Prof. Dr. Timothy Roscoe, Korreferent Dr. Vijay S. Menon, Korreferent Prof. Dr. Matthias Hauswirth, Korreferent

2009

### Abstract

Feedback-directed optimization is becoming more and more important in modern execution environments. On one hand modern CPUs impose additional difficulties for the compiler to generate efficient code: Features like multi-core and complex cache architectures make things even harder for the compiler.

On the other hand, modern programming languages are often not well suited for classic compiler optimizations (due to dynamic class loading, polymorphism, etc.). JIT compilation with feedback-guided optimization can provide significant benefits for such programs since the compiler/runtime is able to adapt to the running program and does not require complex static analysis like in an ahead-of-time compiler. Programming languages like Java or C# make intensive use of references and generally deal with a large number of small objects. As a result, data access pattern are often irregular and difficult (if not impossible) to analyze statically.

This thesis focuses on how to gather feedback provided from the hardware platform via hardware performance monitors (HPM) and use it for program optimizations in a managed runtime for Java programs. We present HPM information as another source of feedback – in addition to traditional profile-guided optimization. We work in a dynamic compilation environment and all optimizations are done as the program runs. When doing online optimizations the runtime overhead of performance monitoring is of special importance.

We look at what kind of information is available and useful for optimizations. We discuss the different problems and challenges that come with collecting HPM information. The information has to be precise and unbiased. Different hardware platforms offer different ways of obtaining HPM information. We look at two platforms in more detail: the P4 (IA-32) and the Itanium Montecito (IPF) processor

Since the HPM data collection runs concurrently with the application it should have a very low execution time overhead. Our solutions adaptively adjusts the sampling period for event sampling to limit the amount of data that has to be processed by the JVM. We present a solution to efficiently collect HPM information in an online setting with a consistently small overhead of less than 1% on average.

The raw HPM information has to be mapped back to the source program to be useful for performance analysis or compiler optimizations. We extended an existing JVM to generate the meta-information necessary to perform this mapping similar to a symbolic debugger. Detailed instruction-level information is required to achieve a reliable mapping.

We present different applications of fine-grained (instruction-level) HPM information:

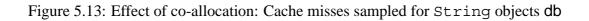

We perform a detailed performance analysis of Java applications. HPM information can be used to identify performance-critical parts of a program at the instruction-level. Our system is also able to measure data address profiles that allow to map HPM samples about cache misses back to data structures on the heap. We show how to use data address profiles to compare the performance behavior of different generational garbage collection algorithms.

As an example of how to use HPM feedback for optimizations, we present two examples: We show how HPM information can be used to perform object co-allocation – an online optimization that improves data locality at GC time in a Java VM. In the best case the execution time is reduced by 16% (3% on average) and L1 cache misses by 28%.

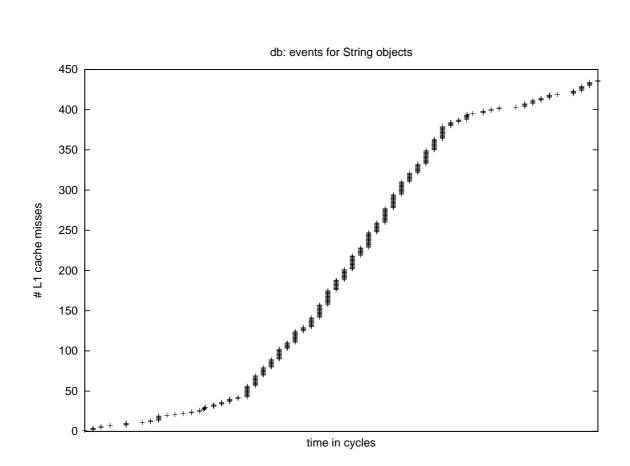

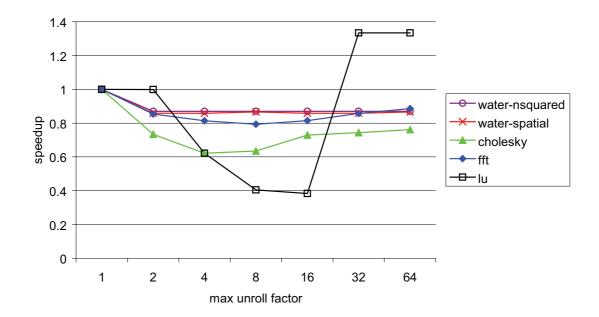

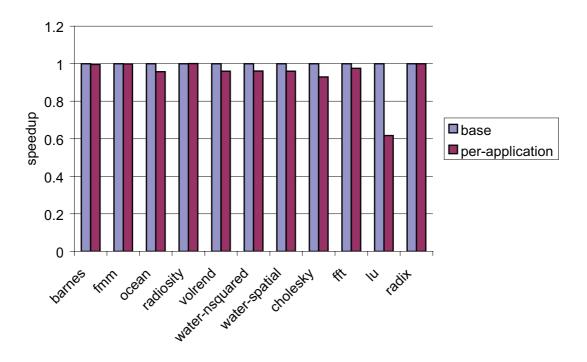

We also demonstrate how HPM feedback can be used to improve loop unrolling in a high-performance static compiler. We perform per-application and per-loop adaptation of loop unrolling parameters using data about stall cycles from the PMU. In the best case we achieve a 39% speedup (6% average) over the default heuristic at the highest optimization level.

## Zusammenfassung

Feedback-gesteuerte Optimierungen werden in modernen Laufzeitumgebungen immer wichtiger. Auf der einen Seite haben moderne Prozessoren immer mehr Funktionen, die es einem Compiler schwer gestalten effizienten Code zu generieren. Beispiele dafür sind Multi-Core-Prozessoren und immer komplexere Speicherhierarchien.

Auf der anderen Seite haben moderne dynamische Progammiersprachen Eigenschaften, die fuer klassische Compiler-Optimierungen nicht gut geeignet sind (dynamisches Class-Loading, Polymorphismus, etc.). JIT Compiler haben hier den Vorteil, da sie durch Feeback zur Laufzeit mehr Informationen über ein laufendenes Programm verwenden können und so adaptiv optimieren können ohne komplexe statische Analyse zu benötigen. Programmiersprachen wie Java oder C# verwenden viele Referenzen und eine grosse Zahl von kleinen Objekten. Die Speicherzugriffsmuster sind daher oft unregelmässig und schwierig (wenn nicht unmöglich) statisch zu analysieren.

Diese Dissertation konzentriert sich darauf, wie Informationen, die vom Prozesso durch Hardware-Performance-Monitore (HPM) zur Verfügung gestellt werden, effizient gesammelt und in einer Java Laufzeitumgebung zur Programmoptimierung genutzt werden können. Informationen von den HPM ist eine weitere Quelle von Feedback neben traditioneller Profiling-Information. Unser System ist in eine Java VM mit JIT compiler eingebettet, wobei alle Optimierungen während der Laufzeit ausgeführt werden. Deshalb ist es extrem wichtig, die Feedback-Daten möglichst effizient zu sammeln.

Zuerst betrachten wir welche Art von Informationen zur Verfügung stehen und welche für Optimierungen benutzt werden können. Um HPM-Informationen zu bekommen müssen verschiedene Probleme gelöst werden: Die Informationen müssen genau und unverzerrt sein. Je nach Hardware-Architektur gibt es verschiedene Möglichkeiten das zu erreichen. Diese Arbeit stellt zwei Architekturen genauer vor und beschreibt wie HPM-Informationen genutzt werden könnnen: den P4 Prozessor und den Itanium Montecito-Prozessor.

Da die HPM-Datensammlung und -verarbeitung parallel zur Programmausführung passieren, müssen die zusätzlichen Kosten minimal gehalten werden. Unsere Lösung verwendet ein adaptives Sampling-Intervall um die Datenmenge zu begrenzen und zuverlässig einen geringen Overhead zu erreichen (< 1% im Durchschnitt).

Dann müssen die gesammelten rohen HPM-Daten zurück mit dem Source-Programm verbunden werden, um sie in der Java VM weiterzuverwenden. Wir erweitern eine existierende JVM, indem wir Meta-Informationen über jede Applikation im JIT Compiler speichern, ähnlich wie ein symbolischer Debugger. Um die genaue Instruktion im Source-Programm zu finden ist es notwendig, dass die HPM-Daten auf eine Maschineninstruktion genau sind.

Als nächstes stellen wir verschiedene konkrete Anwendungen der erstellten Infrastruktur vor: Zuerst führen wir eine detailierte Performance-Analyse einiger Java-Programme durch. Die HPM-Daten helfen dabei performance-kritische Load-Instruktionen zu finden.

Mit unserem System können wir auch HPM-Daten mit Addressen im Speicher assoziieren (d.h. Speicheraddress-Profile zu erstellen). Damit ist es möglich Datenstrukturen eines Programms zu finden, die für die Gesamt-Performance entscheidend sind. In unseren Experimenten verwenden wir Speicheraddress-Profile um die Cache-Performance verschiedener Garbage-Collector-Algorithmen im Detail zu vergleichen.

Zum Schluss zeigen wir zwei Optimierungen um zu zeigen, wie HPM-Informationen als Feedback verwendet werden kann. Die erste Optimierung ist Objekt-Koallokation, eine Online-Optimierung für bessere Cache-Performance beim Speicherzugriff auf Java-Objekte. Im besten Fall erreichen wir damit eine Beschleunigung um bis zu 16% (3% im Durchschnitt) und reduzieren die Anzahl der Cache-Misses um bis zu 28%.

Die zweite Optimierung ist Loop-Unrolling. Hier demonstrieren wir wie HPM-Informationen die existierenden Heuristiken für Loop-Unrolling in einem statischen Compiler verbessern kann. Im besten Fall resultiert eine Verbesserung um bis zu 39% (6% im Durchschnitt) verglichen mit der Standard-Heuristik auf dem hoechsten Optimierungs-Level.

## Acknowledgments

Thanks to my PhD advisor Prof. Thomas Gross for the support, for his feedback that helped improving my work and for sharing his invaluable knowledge about how to pursue research as an independent researcher.

Thanks to the second readers Vijay Menon, Mathias Hauswirth and Timothy Roscoe for reviewing my thesis and for the helpful comments.

Thanks to my colleages in no specific order: Valery Naumov, my former office mate, for the friendship and the countless fruitful discussions. Niko Matsakis, my current office mate, with whom I had very good conversations about our research. Yang Su, with whom I exchanged many ideas while writing up the thesis. Mathias Payer, who did his master thesis under my supervision and helped with important parts of the implementation. I'd also like to thank all my other dear colleagues not mentioned here explicitly for the good times spent together and for the feedback and helped me improving my thesis defense presentation.

Finally, thanks to my family. Without my parents I would not be where I am now.

## Contents

| 1                   | Intr | oduction 1          |                                        |    |

|---------------------|------|---------------------|----------------------------------------|----|

|                     | 1.1  | Thesis              | statement                              | 3  |

|                     | 1.2  | Organi              | zation of this dissertation            | 4  |

| 2 Background        |      |                     | 1                                      | 5  |

|                     | 2.1  | Localiz             | zing performance bottlenecks           | 5  |

|                     | 2.2  | Overvi              | ew over hardware performance monitors  | 6  |

|                     |      | 2.2.1               | P4                                     | 7  |

|                     |      | 2.2.2               | Core 2                                 | 8  |

|                     |      | 2.2.3               | IPF                                    | 9  |

|                     | 2.3  | Compa               | arison of different HPM architectures  | 10 |

|                     |      | 2.3.1               | Event-based sampling                   | 10 |

|                     |      | 2.3.2               | Precise instruction-level information  | 13 |

|                     | 2.4  | PEBS                |                                        | 13 |

|                     |      | 2.4.1               | PEBS support on newer IA-32 processors | 14 |

|                     | 2.5  | .5 Runtime platform |                                        | 16 |

|                     |      | 2.5.1               | Perfmon                                | 16 |

|                     |      | 2.5.2               | Jikes RVM                              | 17 |

|                     | 2.6  | Summa               | ary                                    | 18 |

| 3                   | Har  | dware P             | Performance Monitoring in a Java VM    | 19 |

| 3.1 System overview |      | n overview          | 20                                     |    |

|                     | 3.2  | -                   |                                        | 21 |

|                     |      | 3.2.1               | User-space library                     | 22 |

|                     |      | 3.2.2               | Modifications to the VM                | 23 |

|                     |      | 3.2.3               | Modifications to the compiler          | 24 |

|                     | 3.3  | Mappi               | ng HPM data to the source program      | 24 |

|                     |      | 3.3.1               | Method lookup                          | 25 |

#### CONTENTS

|                                    |     | 3.3.2                  | Bytecode lookup                                            | 26 |

|------------------------------------|-----|------------------------|------------------------------------------------------------|----|

|                                    |     | 3.3.3                  | Data address profiles                                      | 28 |

|                                    | 3.4 | Runtir                 | ne overhead of online performance monitoring               | 29 |

|                                    |     | 3.4.1                  | Space overhead                                             | 30 |

|                                    |     | 3.4.2                  | Runtime overhead with a fixed sampling period              | 30 |

|                                    |     | 3.4.3                  | Limiting the monitoring overhead: Adaptive sampling period | 32 |

|                                    | 3.5 | Biasec                 | l event sampling                                           | 35 |

|                                    |     | 3.5.1                  | IA-32                                                      | 36 |

|                                    |     | 3.5.2                  | IPF                                                        | 37 |

|                                    | 3.6 | Summ                   | ary                                                        | 41 |

| 4                                  | Mea | suring                 | application performance behavior using HPM                 | 45 |

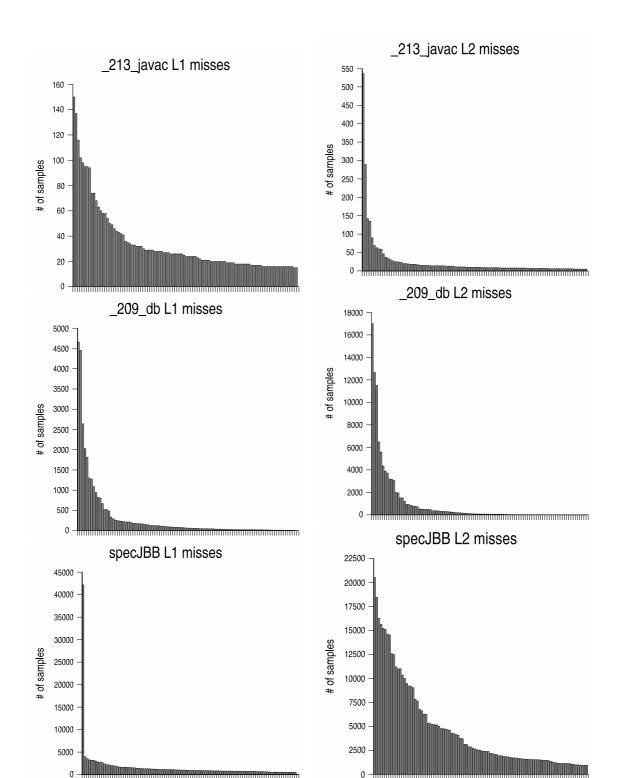

|                                    | 4.1 | Distrib                | oution of data cache misses on load instructions           | 45 |

|                                    | 4.2 | Data a                 | ddress distribution of memory loads                        | 48 |

|                                    | 4.3 | Distrib                | oution of DTLB and cache miss addresses                    | 50 |

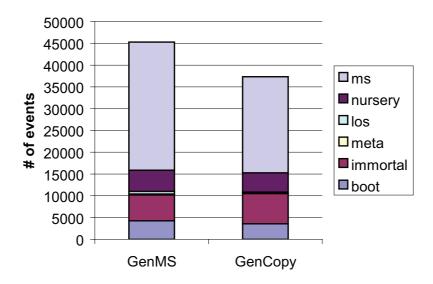

|                                    | 4.4 | Analy                  | sis of data cache misses with different GC algorithms      | 51 |

|                                    | 4.5 | Summ                   | ary                                                        | 56 |

| 5 Optimizations using HPM feedback |     | ons using HPM feedback | 59                                                         |    |

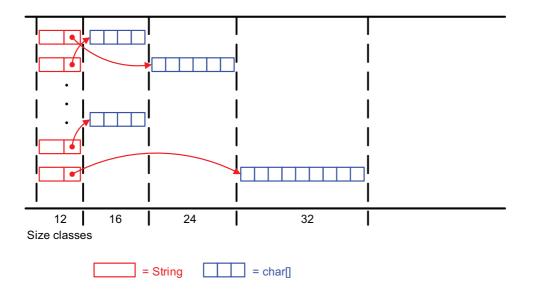

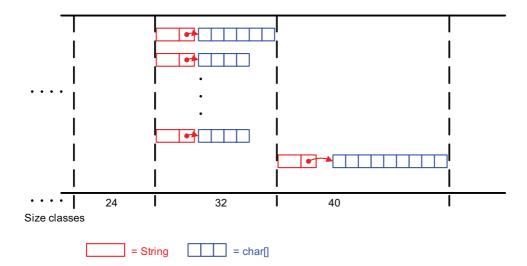

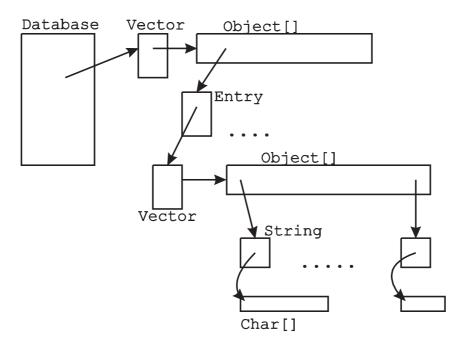

|                                    | 5.1 | Coallo                 | cation guided by HPM feedback                              | 59 |

|                                    |     | 5.1.1                  | Analysis                                                   | 59 |

|                                    |     | 5.1.2                  | Approach                                                   | 60 |

|                                    |     | 5.1.3                  | Mapping cache misses to object references                  | 62 |

|                                    |     | 5.1.4                  | Assigning weights to references                            | 63 |

|                                    |     | 5.1.5                  | Online monitoring                                          | 67 |

|                                    |     | 5.1.6                  | Nursery tracing with co-allocation                         | 67 |

|                                    | 5.2 | Experi                 | imental evaluation of object co-allocation                 | 68 |

|                                    |     | 5.2.1                  | Experimental platform                                      | 70 |

|                                    |     | 5.2.2                  | Methodology                                                | 70 |

|                                    |     | 5.2.3                  | Benchmark programs                                         | 71 |

|                                    |     | 5.2.4                  | Number of co-allocated objects                             | 72 |

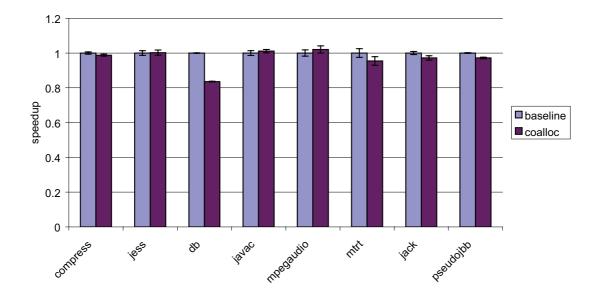

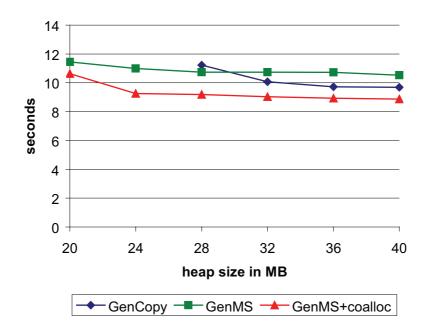

|                                    |     | 5.2.5                  | Performance impact of co-allocation                        | 72 |

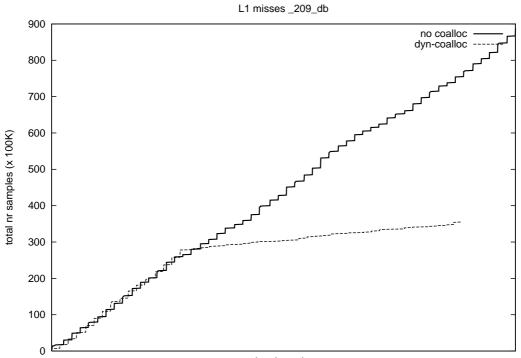

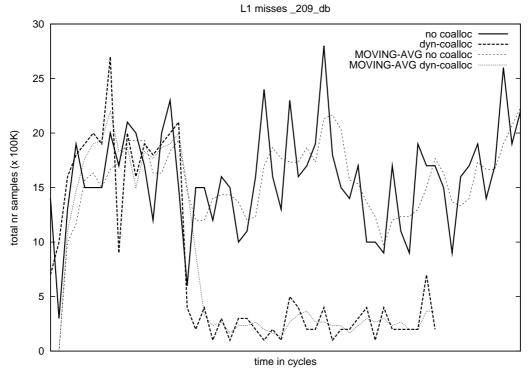

|                                    |     | 5.2.6                  | Runtime feedback                                           | 77 |

|                                    |     | 5.2.7                  | Summary                                                    | 80 |

|                                    | 5.3 | Loop                   | unrolling using HPM feedback                               | 82 |

|                                    |     | 5.3.1                  | Background                                                 | 82 |

|                                    |     | 5.3.2                  | Runtime platform                                           | 83 |

#### CONTENTS

|   |                | 5.3.3 Approach                            | 4 |  |  |  |

|---|----------------|-------------------------------------------|---|--|--|--|

|   |                | 5.3.4 Computing per-loop unrolling hints  | 6 |  |  |  |

|   |                | 5.3.5 Discussion                          | 0 |  |  |  |

|   |                | 5.3.6 Summary                             | 2 |  |  |  |

| 6 | Related Work 9 |                                           |   |  |  |  |

|   | 6.1            | Profiling and Performance monitoring      | 3 |  |  |  |

|   | 6.2            | Data locality                             | 5 |  |  |  |

|   | 6.3            | GC                                        | 5 |  |  |  |

|   | 6.4            | Online optimizations                      | 6 |  |  |  |

| 7 | Con            | clusions 9                                | 9 |  |  |  |

|   | 7.1            | Online performance monitoring             | 9 |  |  |  |

|   | 7.2            | Performance analysis of Java applications | 0 |  |  |  |

|   | 7.3            | HPM feedback-guided optimizations         | 0 |  |  |  |

|   |                | 7.3.1 Object co-allocation                | 0 |  |  |  |

|   |                | 7.3.2 Loop unrolling                      | 1 |  |  |  |

## 1 Introduction

Object-oriented programming languages like Java or C# allow changes to an executing program at runtime, e.g., through the use of a dynamic class loader. At the same time, modern processor architectures are difficult compiler targets if the compiler aims to optimize a program for speed of execution; features like prefetching and branch prediction are (sometimes) difficult to model in a compiler. So a code generator is faced with two difficulties: the dynamic nature of the target program complicates analysis of program properties (e.g., it is difficult to determine pointer aliasing or to analyze the memory referencing patterns), and important performance aspects (e.g., number and location of cache misses) are only evident at runtime.

Fortunately, programs written in such an object-oriented language are usually executed in a virtual machine that includes a JIT (dynamic) compiler. The dynamic compiler has the opportunity to immediately make use of information obtained at runtime. We distinguish between two kinds of information about an application that can be obtained at runtime:

- information that is independent of the execution platform like the execution frequency of methods, basic blocks or instructions; often the term *profiles* is used for this kind.

- machine-level information, i.e. performance data about the hardware level of the execution platform. Examples for this type of information are cache misses, TLB misses, or branch prediction failures. This kind of information is hard to model without feedback from the hardware, and therefore such information can be very valuable for a compiler to optimize memory system performance [49].

Profiles are a useful input to the code generator (not only in a JIT compiler but also in an ahead-of-time compiler). However, many previous optimizations (static and dynamic) focus only on the platform-independent information and did not include direct feedback from the hardware level [74, 62]. Yet most modern CPUs (like the Pentium 4, Itanium, PowerPC) have a performance measurement unit (PMU) to obtain performance-related information and therefore could provide input to a dynamic code generator that optimizes a program for a specific hardware platform. Using low-level hardware feedback information is becoming more and more important, especially on platforms like the Itanium

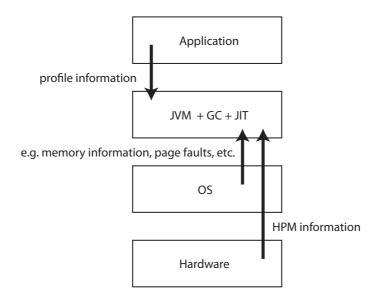

Figure 1.1: Different sources of feedback information that a JVM can use for program optimization.

processor family (IPF) [5, 7] that rely even more on the compiler for achieving good performance.

Of course, an application may also use feedback from other sources to optimize execution on a specific platform: E.g., it could use feedback from the OS about the virtual memory system to optimize memory management [54]. Figure 1.1 shows a high-level view of the different forms of feedback that can be useful for program optimization in a managed runtime environment. From the different sources of feedback that a VM/JIT compiler may use for optimization this dissertation focuses on how hardware-level information can be used for optimization.

To be useful for an optimizing JIT compiler and associated runtime system<sup>1</sup> the collected performance information must be *accurate* enough and *cheap* to obtain at run-time. There are a couple of requirements for a module that makes information from the hardware performance monitors available in such an execution environment:

- The interface between the VM and the performance monitoring hardware should hide machine-specific details where possible.

- The module should be flexible to allow obtaining different execution metrics.

- The overhead to collect the data should be as low as possible, and the system should not perturb executed applications too much.

<sup>&</sup>lt;sup>1</sup>We consider the JIT compiler, the virtual machine (VM), and the runtime system as one unit since all components must cooperate to perform most interesting optimizations.

#### 1.1. THESIS STATEMENT

- The information must be accurate enough to be useful for online optimization. Often the granularity of a method or even a basic block is too coarse to infer which operation is responsible for some event (e.g. cache misses).

- The platform should work for off-the-shelf VMs, with only small or no changes to the core VM code. Otherwise the effort to port the infrastructure to another VM or to a new release would be prohibitively large.

In this dissertation we show how a Java system can benefit from using machine-level performance data. The approach and results are in general not tied to the Java programming language. Of course, any compiler that uses platform-specific information may also use profile information, e.g., to decide where and when to exploit the results obtained from the performance measurement unit, but this aspect is not discussed further here.

We describe and evaluate a module to feed fine-grained performance data from the hardware performance measurement (HPM) unit of a modern processor into the Java system. Our infrastructure is built on top of the Jikes RVM [22, 21], a freely available open-source research VM implemented in Java, and the perfmon HPM interface [56] running on a Linux kernel.

In our system we exploit special features of the P4 processor, called precise eventbased sampling (PEBS), that allow to correlate measured events to single instructions and to the source program (in our case Java bytecode). The overhead of the runtime performance monitoring is reasonably low and stable (<1% avg) for a large number of benchmark programs. We achieve this using adaptive event-based sampling.

We also show how the collected data can be used for detailed performance analysis in a Java runtime environment using instruction address profiles and data address profiles.

As an example application of our infrastructure we present a garbage collector that is guided by online hardware feedback and report the results for a selection of standard Java benchmarks. The garbage collector improves data locality of Java programs automatically by co-allocating heap objects using information about data cache misses. The principal idea is to identify those objects and references that "produce" the largest number of cache misses. The garbage collector uses these hints to adapt its behavior for better data locality. Our system is, however, not aimed just at data locality optimizations in the GC. Instead machine-level performance data should be thought of an additional feedback for the whole runtime environment. We chose this optimization to demonstrate that the overhead of the approach is low in practice to allow a code generator/runtime system to deal with memory performance – one of the difficult areas for a compiler for object-oriented programs.

#### 1.1 Thesis statement

The key contribution of this thesis is to show that it is possible to collect detailed performance data from the hardware during runtime with a low-enough overhead so that it can be directly applied for optimization by a managed runtime environment.

#### 1.2 Organization of this dissertation

Chapter 2 describes the hardware and software platform we used and gives an overview of the performance monitoring features of different hardware architectures.

Chapter 3 describes the online performance monitoring infrastructure we built in detail and discusses problems and challenges when doing low-overhead online performance monitoring. We show how we achieve robust low-overhead performance monitoring across different types of programs, how we reduce or avoid biased measurements when doing event-based sampling, and how we map raw HPM data back to the source program.

Chapter 4 shows how our performance monitoring infrastructure can be used for finegrained performance analysis of Java programs. It discusses the use of instruction address profiles and data address profiles to track down performance-critical instructions and data structures in a program. We also compare the performance of different garbage collection algorithms in terms of cache performance.

In Chapter 5 we present two optimizations that use hardware feedback to improve performance. The first application of online performance monitoring presented is *object co-allocation*, a fully-automatic online optimization driven by hardware feedback. We describe our approach and show how co-allocation improves data locality and speeds up applications by up to 18% in a Java VM using a generational garbage collector. As a second application of HPM information we evaluate how loop unrolling can be improved using hardware feedback. We performed experiments in a static C/C++ compiler and achieve an average speedup between 5 and 6% over the default heuristic at the highest optimization level.

Finally, Chapter 6 gives a survey over related work and Chapter 7 gives a summary of our results and concluding remarks.

## 2

## Background

This chapter gives an overview of the platforms that we can use for performance monitoring. We discuss different approaches of how to localize performance bottleneck in applications in Section 2.1 and show what features modern CPUs offer for performance analysis in Section 2.2.

Section 2.3 compares the functionality found on the performance monitoring unit (PMU) of the two architectures covered in this chapter: the IA-32 and the Itanium processor family.

Section 2.4 describes precise event-based sampling (PEBS), a feature of the IA-32 PMU which allows to collect instruction-level performance data in detail. Our system uses PEBS for performance monitoring.

Finally, we shortly describe the software components that our system is based on in Section 2.5. There we also discuss the motivation behind the platform choices made during the implementation of our system.

#### 2.1 Localizing performance bottlenecks

This section gives an overview of different techniques to track down performance bottlenecks in applications. There are different ways to characterize the performance of an application. Some techniques are only suitable for offline profiling and analysis. Others are also usable in an online optimization setting. Table 2.1 shows the different approaches to measuring and characterizing application performance.

- 1. Instrumentation [81]: The compiler inserts code sequences that count certain events in the application code. In most cases it is used to generate edge profiles for feedback-guided optimization. It usually requires recompiling existing code. In a dynamic runtime environment instrumentation is often used during the initial compilation [24, 79, 16] or interpreted execution [42]. In the following (optimizing) recompilation there is usually no instrumentation since it slows down execution considerably.

- 2. Timer-based sampling: The Jikes RVM [24] uses timer-interrupt-based sampling of the application's calling stack to determine frequently executed methods. This is a

|                  | Instrumentation     | Timer-based | HPM sampling             | Simulation  |

|------------------|---------------------|-------------|--------------------------|-------------|

| Runtime overhead | medium to high      | very low    | low to very low          | very high   |

| Resolution       | basic block, method | method      | basic block, instruction | instruction |

| Accuracy         | medium to high      | low         | medium to high           | high        |

| Invasiveness     | medium to high      | very low    | very low                 | N/A         |

Table 2.1: Overview over different techniques for performance profiling.

very light-weight approach, but it is in general limited in resolution to method-level information. For more fine-grained data (e.g., at the basic block level) the interrupt frequency would be prohibitively high. The main advantage of sampling compared to instrumentation is that there is no additional code that has to be inserted into the program, and therefore the runtime overhead is much lower.

- 3. HPM event-based sampling [32]: Event-based sampling can be used to identify locations where performance-critical events occur. It also provides platform-specific data not available with software-only methods, but requires hardware support. Fortunately, most modern CPUs support event-based sampling. The problem is that the precision of the data often varies a lot depending on the underlying hardware platform and the exact data source. Also, the available hardware documentation often is not detailed enough about these issues so that a compiler implementors can sometimes not be sure which data actually could be used for hardware feedback-guided optimization.

- 4. Simulation [69]: Simulation can give very precise (and also platform-specific) information about performance behavior of applications. To get useful information the simulator needs a detailed model of the simulated architecture. One downside is that detailed simulation is usually very expensive in terms of execution time (up to 20-100x slowdown), so it is not applicable for dynamic optimization. Approaches that do not perform a full simulation, but instead approximate the precise behavior may be possible even during runtime ([91]).

Overall HPM sampling provides a good compromise for dynamic compilation systems which are the main target platform for feedback-guided optimizations. Instrumentation and simulation have their applications, but are either limited in the type of information that can be obtained, or too expensive for use in a dynamic runtime.

#### 2.2 Overview over hardware performance monitors

Almost all modern general-purpose CPUs offer special hardware support for performance monitoring. In this work we focus mainly on two platforms: the IA-32 represented by the Intel P4 and the Core 2 microarchitecture and, for some experiments, the Itanium 2 Montecito from the Itanium processor family (IPF).

#### 2.2. OVERVIEW OVER HARDWARE PERFORMANCE MONITORS

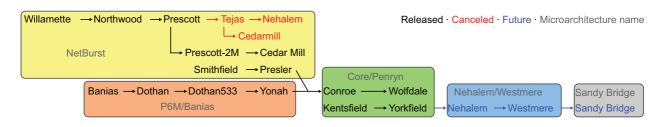

Figure 2.1: Intel's IA-32 processor roadmap [60].

Figure 2.1 [60] shows the roadmap of the Intel IA-32 architectures. Processors using the Netburst microarchitecture are those with a yellow background, Core and Core 2 CPUs have a green background. Names in red are cancelled processors.

For our experiments with IA-32 we are using Prescott P4 processors. Current processors belong to the Core 2/Penryn architecture which developed out of the P6M (Pentium 3, Pentium M) and the Netburst microarchitectures. Even though the Netburst family has been completely replaced by newer Core 2 architecture processors many features of the P4 are still present in the newer architectures. This means that results taken from that CPU generation are in many cases still valid on today's CPUs. Especially, the PMU architectures are very similar. Core 2 has some extensions, but supports basically all PMU features of the P4 that we will discuss in the following sections. The differences of the P4 and Core 2 with regard to performance monitoring are covered in Section 2.2.2. Section 2.4.1 discusses the mapping of HPM events that are important for this work from the P4 to Core 2-based CPUs in more detail.

In the next sections we will describe the hardware performance monitors of the these architectures in more detail.

#### 2.2.1 P4

The P4 offers a large variety of performance events for counting [6, 78, 77].

In total it has 18 counter registers each 40 bit wide. Each of the counter registers has a counter configuration control register (CCCR) associated with it.

Event selection control registers (ESCR) are used for selecting which events to be monitored with the counter registers. There are 45 ESCRs on the Pentium 4 corresponding to 45 events from various parts of the system. (This number may be larger in newer processor models). Each counter register has several ESCRs associated with it to select which events should be counted in that counter register

The P4's performance monitoring unit supports three modes of operation:

• Event counting: The performance counters are configured to count events detected by the CPU's event detectors. A tool can read those counter values after program execution and reports the total number of events. This mode can be used to obtain numbers like cache miss rate, total execution cycles, etc.) More fine-grained information (e.g., on a method level) can be obtained by instrumenting the program for reading counter values. An application of this measurement mode would be to evaluate the overall effect of program transformations.

• Imprecise event-based sampling (IEBS): A performance counter register is configured to count an event and whenever a certain number of events p has occurred (when the counter overflows), the CPU generates an performance monitoring interrupt. For a sampling period p the user sets up the counter register to

$$2^w - p$$

where w is the width of the counter register. When this register overflows the CPU issues an interrupt. The interrupt service routine records the return address (program counter where the overflow happened), resets the counter and restarts the counter. From the return address it is possible to estimate the location of an event, but the precision of this information heavily depends on the underlying microarchitecture (out-of-order execution, pipeline length, etc.) since the execution of the interrupt service routine is usually delayed by several instructions. We analyze event-based sampling in more detail in Section 2.3.1.

• Precise event-based sampling (PEBS): This type of monitoring is similar to nonprecise event-based sampling, but it uses a predefined memory buffer to save the architectural state (all register contents) whenever the counter overflows. PEBS reports the exact instruction where the sampled event happened using special hardware support. In contrast, normal EBS can only measure an approximate location for sampled events due to the super-scalar design and out-of-order execution. With IEBS the sampled program pointer may be up to 5 dynamic basic blocks away from the actual source instruction [45]. Another difference is that PEBS can be used to count only a subset of the available events and only one PEBS event can be counted at a time. We discuss PEBS in more detail in the next section.

#### 2.2.2 Core 2

This section gives a brief overview of the Core 2 architecture [11, 12, 13, 14, 15] with focus on the differences to earlier architectures that concern performance monitoring. There are many architectural differences between older processors based on the Netburst microarchitecture (P4) and the Core 2 microarchitecture. Most of them do not affect the performance monitoring unit significantly. Core 2 also employs aggressive out-of-order execution like the P4 which makes precise sampling equally challenging.

Precise event-based sampling (PEBS) as found on the P4 is available also on Core 2. The set of events is mostly equivalent, but of course there are small changes. The programming of the PEBS features also changes slightly. The exact differences (e.g. which registers to program) can be found in the corresponding Intel architecture reference manuals [15].

8

#### 2.2. OVERVIEW OVER HARDWARE PERFORMANCE MONITORS

The events available on the Core 2 microarchitecture are adapted to the changed cache hierarchy: E.g., there is also no trace cache for micro-ops with Core 2, but instead a normal L1 instruction cache, so the Core 2 PMU offers events for L1 I-cache instead of events for the trace cache. We discuss specific issues about HPM events that must be addressed when porting our system to Core 2 in Section 2.4.1.

The multi-core nature of Core 2 also adds more HPM metrics that can be measured: For some events we can choose to use per-core counters or measure cumulatively for all cores. This can be done by setting a mask value to filter out event only from one core, or count events from all cores. However, in this work we do not deal with events that are specific to multi-processor systems.

#### 2.2.3 IPF

This subsection gives a short overview of Itanium-specific features for performance monitoring [5, 7, 8, 9, 10]. We focus on the newer generation of Itanium processors (Montecito) which we are using in some of our experiments.

The Itanium2 has 12 48-bit wide counter registers that can be programmed to count events. In total there are around 600 different events to measure. The IPF also allows to filter events by instruction address range, data address range, privilege level (supervisor vs user mode) or by op-code. In contrast, the IA-32 can only filter events by privilege level.

The IPF also supports the two modes of measurement present on IA-32: simple event counting and event-based sampling. Additionally it has three features not present on IA-32: the Event Address Register (EAR) the branch trace buffer (BTB) and stall cycle accounting which we will describe shortly:

- 1. Stall cycle accounting: This measurement mode allows to attribute stall cycles in the CPU to different functional units of the CPU. This is makes it possible to find out where stall cycles come from. The different stall categories are: front end stalls, execution unit stalls, register stack engine stalls, L1 data cache stalls, and flush stalls.

- 2. Event Address Register (EAR): The EAR can be used for event-based sampling. It is restricted to certain events and it records the exact data (or instruction) address related to an event sample. The IPF does not have a mode comparable to PEBS on IA-32. Instead the EAR is used to gather precise information. Events that support EAR are TLB misses, D-cache/I-cache misses and ALAT misses. It also allows to filter miss events by latency to distinguish short versus long latency misses.

- 3. Branch Trace Buffer (BTB): The branch trace buffer is also a feature not available on IA32. It is used in combination with event sampling. When a sample is taken (e.g. on an I-cache miss, instruction retired, etc.), the BTB records a history of up to the last 8 branches<sup>1</sup> plus additional information about each branch (address, target,

<sup>&</sup>lt;sup>1</sup>On the newer Itanium 2 Montecito processors the BTB records 16 branches.

taken/not-taken, predicted correctly/incorrectly). For example, it can be configured to record branch history on each sampled I-cache miss.

Instructions on the IPF are grouped into bundles of 3 instructions 41 bits wide each. Each bundles is 128 bit long and has a 2 bits that indicate the type of bundle.

Instructions are issued to the execution units in instruction groups of up to 6 instructions. All instructions of a group are issued in parallel which means they must not have any dependencies between each other. The compiler has to make sure it inserts stop bits between instruction groups properly to separate instructions that have data dependencies.

As a consequence the HPM unit not only reports the instruction address of a sampled instruction, but also the number of the bundle in the instruction group (0 or 1) and the slot number of the instruction within that bundle (0, 1 or 2). This way the exact source instruction of an event can be found.

For events that do not support the EAR it is only possible to create instruction address profiles (like with IEBS on IA-32). The reported instruction address only provide limited precision and can be off by several bundles depending on which event is measured. In our own experiments we found that the instructions reported the imprecise event-based sampling are often around 5-6 bundles (=15-18 instructions) away from the correct instruction address. For some events we even observe a delay of up to 20 bundles. As a consequence these events can only be located at a very coarse grained level without any further analysis (e.g. method-level).

#### 2.3 Comparison of different HPM architectures

This section compares the features, advantages and disadvantages of two HPM architectures: the P4 as an example of the IA-32 architecture and the Itanium2 Montecito (IPF).

#### 2.3.1 Event-based sampling

We performed an experiment to compare the information that can be obtained using normal event-based sampling on both platforms. In this mode the CPU issues a performance monitoring interrupt (PMI) whenever a preset counter overflows. The location of the event can be estimated from the return address given to the interrupt service routine.

When performing event-based sampling we can see the difference between an inorder-execution processor (IPF Montecito) and an out-of-order platform (P4) in the measurement results.

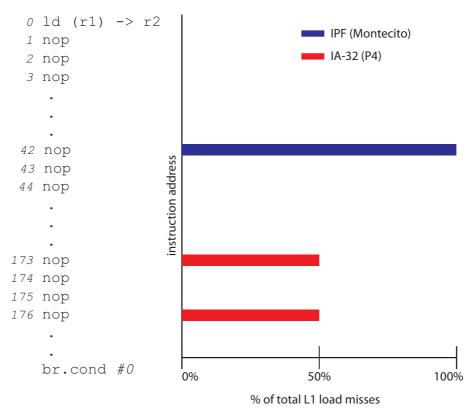

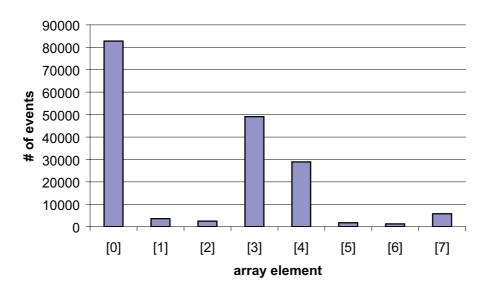

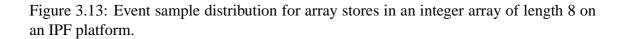

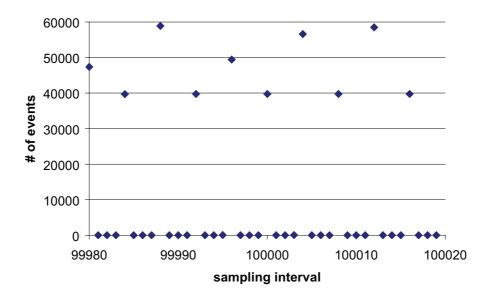

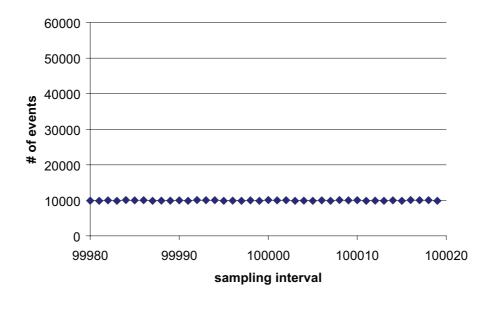

Figure 2.3 shows the histogram of instruction addresses delivered to the performance monitoring interrupt routine on an P4 and an Itanium Montecito processor. Here, we setup the system to measure L1 cache misses. The C source code of the example program is given in Figure 2.2. It iterates over a large array (> 16KB, the size of the L1 data cache) multiple times so that the array load at line number 6 produces a capacity miss whenever the L1 data cache becomes full.

#### 2.3. COMPARISON OF DIFFERENT HPM ARCHITECTURES

The left side of Figure 2.3 shows the relevant parts of the loop body in pseudo-code assembly. It consists of one load instruction per iteration. The load instruction sequentially loads an integer value from a large array which is larger than the size of the L1 cache). After the load we manually inserted a few hundred NOP instructions to observe the delay of the program counter reported via the performance interrupt service routine. We iterate over the array a large number of times so that we can expect a large enough number of L1 capacity misses.

On the Montecito all samples are reported on the same address. We see one peak in the histogram at a distance of 42 instructions (14 bundles) between the load instruction and the reported address<sup>2</sup>.

In contrast, on the P4 we see two peaks at 173 and 176 NOP instructions where each contains 50% of the sampled events <sup>3</sup>. The reason for multiple peaks is that the P4 is an out-of-order processor whereas the Montecito is an in-order architecture.

The distance between the event source address and the reported address can vary considerably depending on how many instructions can be fetched and processed in between. Also, the delay can be different in a normal application where there are no artificially inserted NOP instructions. The experimental results from our setup serve as an illustration for the problems and challenges when doing event-based sampling rather than a guideline to calibrate other measurements. In general we can assume the the distance between an event source instruction and the reported instruction address is unknown within some lower and upper limit that can be approximated experimentally.

If we assume that many basic blocks consist of 10 or less instructions, the reported location may more than 4 (on the Montecito) up to or 17 (on the P4) dynamic basic blocks away from the event source instruction. This large distance (which may not be known in advance in general) makes is especially hard to map such events back to the source program. On the P4 there is the additional difficulty of event samples that are dispersed over multiple addresses. But it remains hard even on IPF where there is a more predictable distance between the source instruction and the instruction reported by the PMU.

Even though the example workload is very simple compared to real-world applications, it illustrates the difficulties when trying to identify performance bottlenecks in a program reliably.

It also shows that out-of-order processors make things even more complicated so that it is almost impossible to obtain precise instruction-level information without special hardware support like PEBS or the EAR.

<sup>&</sup>lt;sup>2</sup>This distance can be different for other events. In our experiments with microbenchmarks we observed delays from 5 to 20 bundles (up to 60 instructions).

<sup>&</sup>lt;sup>3</sup>For other combinations of instructions and events we observed different (but in general not predictable) number of peaks in the histogram (up to to 3).

```

long k = 0;

1

long * A = malloc(10000*sizeof(long));

2

3

int i;

4

for ( i =0; i <10000000; i ++) {

5

k += A[i \% 10000];

6

asm("nop"

7

"nop"

8

"nop"

9

10

. . .

11

12

. . .

13

"nop"

"nop"

14

15

"nop");

}

16

```

Figure 2.3: Instruction address histogram obtained with event-based sampling on the IPF and the IA-32 platform.

#### 2.3.2 Precise instruction-level information

Since normal event-based sampling is too imprecise to provide fine-grained information, both platforms, IA-32 and IPF, have special hardware support for obtaining precise instruction-level HPM information for a limited number of events:

- PEBS: All IA-32 processors from the Pentium P4 on (including the newer Core 2 generation CPUs) support Precise Event Based Sampling (PEBS) to accurately sample performance events. A small subset of events can be measured in PEBS mode. The hardware takes care of tracking the exact source instruction for a sampled event and reports all register contents when that event happened. One drawback is that only a very small number of events can be measured with PEBS (e.g., I-cache events are not available). For all others the user has to fall back to normal event-based sampling (EBS) which offers only imprecise instruction-level information. Also, only one PEBS-enabled event can be measured at a time.

- 2. EAR: The IPF architecture offers the Event Address Registers (EAR) to pinpoint the instruction address or the data address related to an event. It is used together with event-based sampling and can be used to derive the exact origin of an event since the program counter delivered to the interrupt service routine on a counter overflow can be up to 20 instruction bundles away from the event-producing instruction. The EAR can only be used with a limited set of events, but the EAR supports a wider range of events compared to PEBS events on IA-32 (e.g. L1/L2 data cache, instruction cache, TLB, and ALAT events)

#### 2.4 **PEBS**

We will discuss the PEBS features of the P4 processor in more detail since our system heavily relies on them for performance monitoring.

In PEBS mode the HPM unit performs the collection and storage of the samples autonomously once configured. Figure 2.4 shows the format of a PEBS sample. Each sample contains the CPU state (the program counter EIP plus all register contents) after the sampled instruction. The register values contained in a PEBS sample are used later to recover more high-level information about a PMU event.

The CPU provides a set of registers that specify a buffer called debug store area (DS area). This buffer is allocated by the OS (i.e. the perfmon kernel module). The client (in our case the Java VM) specifies the size of the DS area, and a threshold value that determines at which point the CPU will generate an performance monitoring interrupt (PMI) (e.g., when the DS area is 90% full). After calling the interrupt service routine, the HPM unit is reset to start filling the DS area from the beginning.

Setting up the hardware for monitoring requires the following three steps in case of PEBS<sup>4</sup>:

<sup>&</sup>lt;sup>4</sup>Normal imprecise event-based sampling only requires the first two steps.

| 1  | typedef | struct {    |        |         |

|----|---------|-------------|--------|---------|

| 2  |         | unsigned    | long   | eflags; |

| 3  |         | unsigned    | long   | ip;     |

| 4  |         | unsigned    | long   | eax;    |

| 5  |         | unsigned    | long   | ebx;    |

| 6  |         | unsigned    | long   | ecx;    |

| 7  |         | unsigned    | long   | edx;    |

| 8  |         | unsigned    | long   | esi;    |

| 9  |         | unsigned    | long   | edi;    |

| 10 |         | unsigned    | long   | ebp;    |

| 11 |         | unsigned    | long   | esp;    |

| 12 | } pfm_p | $ebs_p4_sm$ | npl_en | try_t;  |

Figure 2.4: One PEBS record on the P4 contains the instruction pointer (EIP) and all register contents (total 40 bytes).

- Setting the ESCR. It selects the event to be monitored plus event-specific options and determines if we count events in user-level and/or kernel-level code.

- Setting the CCCR that corresponds to the counter register used. It selects the corresponding ESCR that we initialized in the first step.

- When using PEBS we need to initialize two special registers (PEBS\_MATRIX\_VERT and PEBS\_ENABLE) to set up PEBS specific options.

The exact details and values for the setup of the individual registers can be found in the Intel documentation [6] and from the example programs included with perfmon [56].

#### 2.4.1 PEBS support on newer IA-32 processors

This section discusses the support for precise sampling (PEBS) on newer IA-32 processors based on the Core 2 microarchitecture. To make the techniques presented in this thesis applicable to those processors we need to have precise sampling support for the HPM events that we use on the P4.

Fortunately, all the important PEBS events provided by the PMU on the P4 processor have corresponding a event on the newer IA-32 Core 2 architecture. The Core 2 processor family offers a larger set of events which mostly backward compatible to previous CPU generations except for small variations.

Table 2.2 shows equivalent events for different IA-32 architectures: the P4 (Netburst architecture) and the Core 2 architecture. Here we only discuss events concerning the memory hierarchy. The table shows the exact event descriptor for each event type. In most cases each metric is composed of a high-level event (e.g. FRONT\_END\_EVENT)

|                 | Architecture               |                                  |  |

|-----------------|----------------------------|----------------------------------|--|

| HPM event       | P4 (Netburst)              | Core 2                           |  |

| L1D load miss   | REPLAY_EVENT.L1_LD_EVENT   | MEM_LOAD_RETIRED.L1D_MISS        |  |

| L1I miss        | n/a <sup>a</sup>           | n/a <sup>b</sup>                 |  |

| L2D load miss   | REPLAY_EVENT.L2_LD_EVENT   | MEM_LOAD_RETIRED.L2_MISS         |  |

| L2I miss        | n/a <sup>c</sup>           | n/a <sup>c</sup>                 |  |

| L3 miss         | n/a <sup>b</sup>           | n/a <sup>b</sup>                 |  |

| DTLB load miss  | REPLAY_EVENT.DTLB_LD_MISS  | MEM_LOAD_RETIRED.DTLB_MISS       |  |

| DTLB store miss | REPLAY_EVENT.DTLB_ST_MISS  | n/a <sup>b</sup>                 |  |

| DTLB miss       | REPLAY_EVENT.DTLB_ALL_MISS | n/a <sup>b</sup>                 |  |

| ITLB miss       | n/a <sup>b</sup>           | n/a <sup>b</sup>                 |  |

| memory load     | FRONT_END_EVENT.TAGLOADS   | INSTR_RETIRED.ANY_P <sup>d</sup> |  |

| memory store    | FRONT_END_EVENT.TAGSTORES  | INSTR_RETIRED.ANY_P <sup>d</sup> |  |

<sup>*a*</sup>The P4 has a micro-op trace cache instead of a normal L1 I-cache.

<sup>b</sup>No corresponding PEBS event available on this architecture.

<sup>c</sup>L2 cache is unified on both architectures.

<sup>d</sup>This event requires filtering out memory operations since it records *all* retired instructions.

Table 2.2: Equivalent precise sampling events for different CPU architectures.

and a mask value (e.g. TAGLOADS) which selects sub-category of the high-level event. So FRONT\_END\_EVENT.TAGLOADS would select all load instructions that are seen by the CPU's front end. There are more selection criteria with corresponding selection mask values (e.g. counting speculative vs. non-speculative instructions) which are omitted here for conciseness.

We can see that all events used on the P4 can be also measured on the newer Core 2-based processors. Each P4 PEBS event of interest can be mapped to a corresponding event on Core 2. However, there are a few subtle differences for individual metrics:

- In some cases like for DTLB cache misses, the P4 can capture load and store misses whereas the Core 2 can only measures loads.

- Another difference is that for measuring memory loads or stores the P4 counts operations seen at the front-end whereas on Core 2 only retired instruction are counted. Instructions executing speculatively may not retire, but are discarded at the backend. However, this discrepancy can be resolved by filtering out speculative instructions by configuring the P4 PMU accordingly.

In general small differences like this do not pose a fundamental problem in applying our techniques on newer architectures. Therefore, our techniques remain applicable for current IA-32 CPUs. Also, the requirements to program PEBS on the P4 and Core 2-based CPUs are very similar. The exact differences are described in Chapter 18 of the IA-32 architecture reference manual[15].

#### 2.5 Runtime platform

This section shortly describes the components involved in our system. It also presents the motivation and the reasons why we picked a particular component for this dissertation. It covers:

- the Linux kernel module for performance monitoring,

- Java VM, the

- JIT compiler and the

- memory management/GC system.

#### 2.5.1 Perfmon

Perfmon [56] is a Linux kernel module that gives the user access to the CPU's performance monitoring features. Perfmon was originally developped at HP labs and is now available as open source.

We use the perfmon2 kernel patch and the corresponding libpfm library [55] to access the hardware performance monitors.

The main reason for using perfmon was that it supports all modern PMUs and offers support for many advanced features like PEBS on the IA-32. It is also actively maintained by the community and seems to become the standard for tools and application of performance monitoring on Linux.

The kernel module provides system calls to read and write the performance monitoring registers of the CPU. The second important feature of perfmon is a virtual perprocess view of the hardware performance counters. By default the hardware counts events system-wide (i.e. events of all processes and the OS kernel). It provides a so-called performance monitoring context that can be attached to a Linux process and that contains all HPM information on a per-process basis. Other functions exist for initializing, starting and stopping counters.

Libpfm is a user-space shared library (libpfm) that provides functions common to all platforms. Events that are existent on all hardware platforms (cycle counting, retired instructions) have special platform-independent calls for setup.

However, libpfm has some critical limitations: It does not directly support platformspecific features like PEBS. When measuring platform-specific events the user has to setup the PMU registers manually. For that purpose the proper values for the HPM registers have to be determined from the hardware documentation directly. This limitations lead us to implement our own user-space library. We only reuse libpfm for the parts that do not deal with PEBS. Our library makes the PEBS events available to user applications in a convenient way. For experiments with normal binaries (e.g., compiled from C/C++) perfmon offers also a command-line interface to perform off-line measurements and profiling.

When compiling with debug information (-g) events can be attributed to functions and source line numbers. To get more detailed information it is usually necessary to perform further analysis manually using a symbolic debugger (e.g., gdb) and disassembling the relevant part of the program.

#### 2.5.2 Jikes RVM

Our implementation is done with the IBM Jikes RVM (version 2.4.2) [22, 21], a high performance Java virtual machine written mostly in Java. It includes an optimizing compiler with an adaptive optimization system (AOS) [24]: First, each method is compiled with a simple and quick baseline compiler. This first compilation does not include any local or global optimizations. Basically, the baseline compiler just concatenates templates for each Java bytecode instruction. The resulting machine code is not very efficient, but it is just used either for infrequently executed methods, or for collecting profile information at runtime for frequently executed methods which will be recompiled later by the optimizing compiler.

Methods that are executed frequently enough are recompiled and optimized using the optimizing compiler. The optimizer has three optimization levels (-O0, -O1 and -O2). The VM uses a static cost model with profiled execution frequencies to decide which optimization level to apply for a method.

When compiling a method with the optimizing compiler Jikes RVM initially translates Java bytecode into a high-level IR (HIR). It is almost equivalent to the Java bytecode except that it is not stack-based, but uses virtual registers to store temporary values.

After performing high-level optimizations (e.g., loop transformations, inlining, devirtualization, redundant load elimination, CSE, constant/copy propagation, etc.) the IR is lowered into the low-level IR (LIR) on which the optimizer performs a set of low-level optimizations (e.g., instruction scheduling, CSE, constant/copy propagation, etc.).

Finally, the compiler generates the machine-level IR (MIR) which closely resembles the final machine code. It does another pass of transformations (register allocation, peephole optimizations) before it generates the executable machine code.

To estimate the execution frequency for methods the VM samples the call stack in regular time intervals and records which methods are on top of the call stack. This is a very efficient way to approximate method execution frequencies without the need for instrumentation <sup>5</sup>.

Jikes RVM provides its own thread implementation. It forks one OS process per physical CPU called "virtual" processors. The thread scheduler schedules all Java threads (including the GC and the compilation thread) on these "virtual" processors. It is a quasi-

<sup>&</sup>lt;sup>5</sup>Alternatively, the baseline compiler can instrument each method with a counter to measure execution frequency.

preemptive m-to-n threading model [20] similar to Java "green threads". However, this model has implications on implementing I/O in the VM: if one methods executes a block-ing system call the whole virtual processor is blocked until the call returns.

We specifically avoid blocking I/O calls when communicating with the kernel module (perfmon) to avoid unnecessary blocking of the virtual processors.

Jikes RVM comes with a flexible module for memory management, the Jikes Memory Management Toolkit (MMTk) [28]. It allows to specify different garbage collector and allocation policies at compile time. All basic GC algorithms like mark-and-sweep, reference counting, semi-space copying and generational GC are implemented in MMTk. In our experiments we mainly use different variants of the generational collectors.

There are several reasons why Jikes RVM was picked as a implementation platform in this thesis:

- Implementation and development: For a full-featured JVM the Jikes RVM is still relatively simple and small compared other JVMs. The fact that it is implemented in Java also makes extending and debugging the VM more convenient than when using a VM implemented in C or C++.

- Performance: For a research compiler Jikes RVM offers reasonable performance compared to production JVMs.

- Availability: Jikes RVM is open-source and actively developed by the community.

#### 2.6 Summary

Modern micro-architectures offer an increasing amount of hardware performance monitoring facilities. For a compiler and runtime system that wants to perform feedbackguided optmizations it is important to be able to obtain precise instruction-level data. Almost all newer CPUs have support for precise event sampling: IA-32 offers Precise Event Based Sampling (PEBS), IPF has the Event Address Register (EAR).

The HPM events (especially the PEBS events) available on newer IA-32 processors like the Core 2 are compatible to the events of the P4 processors we are using in this work. As a result, the infrastructure presented here still can be used on newer platforms.

In our implementation we are using Linux and the perfmon kernel patch. Perfmon seems to become the standard module for performance monitoring and fully supports all platforms we are dealing with (IA-32, IPF)

As a Java runtime system we use Jikes RVM, a research Java virtual machine. It is relatively easily extensible (compared to a full-size production JVM), but still offers competitive performance which makes it a good candidate for a research prototype.

# 3

## Hardware Performance Monitoring in a Java VM

This chapter discusses the design and the implementation of a HPM measurement module for a Java VM. The goal is to collect 'real-time' hardware performance data at runtime. Such a system has additional requirements to meet compared to an off-line profiling tool. We will describe the different design parameters to make efficient online performance monitoring possible.

First, we present an overview over the system in Section 3.1. Section 3.2 discusses the implementation and the changes done to the affected components: the VM, the JIT compiler and optimizer and the memory management.

We will the go on with a discussion on the various problems and challenges that arise when performing online performance monitoring and present a solution to each them. Some of these issues like mapping raw HPM data to the original program source or avoiding biased measurements are a general problem when collecting HPM data, others, like how to limit the worst-case measurement overhead, are specific for online monitoring and do not occur in an off-line setting. There are three main challenges to overcome so that such a system can be used in practice:

- 1. Mapping HPM data to source code (Section 3.3): The hardware only delivers raw addresses and register contents. The system needs additional meta-information about the source program to correctly map the raw HPM data back to the source code. In our case the source code consists of Java bytecode. For every HPM event we have to find the Java method and the bytecode instruction that is the origin of that event.

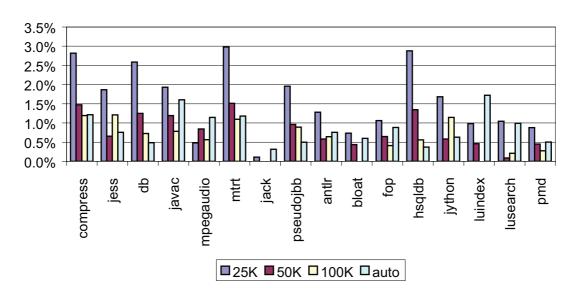

- 2. Monitoring overhead (Section 3.4): There are two objectives concerning runtime overhead to meet. First, achieving a low overhead is crucial in an online setting. The application that runs at the same time as the monitoring code should not experience a significant slowdown. Secondly, in a sampling-based system like ours, the runtime overhead of online HPM measurements should be stable across different applications. Different programs generate different amounts of HPM events. The monitoring module must adapt to changing event rates.

3. Unbiased measurement (Section 3.5): The measurement should accurately reflect the application's performance behavior. Since our system is based on sampling there is always the problem of avoiding a prohibitively large bias. We performed various experiments with micro-benchmarks to quantify the bias when doing sampling, and we will discuss how to improve the accuracy of sampling-based HPM measurements.

#### 3.1 System overview

We use the precise event-based sampling (PEBS) feature of the P4 processor [6] to measure events like cache misses. In principle the system can be implemented on any system that offers the kind of precise instruction-level HPM events like PEBS does. As discussed in Chapter 2 this is the case for the newer Core 2 architecture, but also for the Itanium platform. The PEBS mechanism has two advantages that make it especially useful for monitoring applications during runtime:

The first advantage is that PEBS reports the exact instruction (program counter plus all register contents) for the sampled events. This allows the compiler to recover higher-level information about the collected events, e.g., method, bytecode instruction, or field variable accessed.

Secondly, the CPU collects event samples on its own using a microcode routine and stores them in the Debug Store (DS) area - a buffer supplied by the OS kernel module. An interrupt is generated only when the DS area is filled to a specified threshold.

The P4 has a small number of events that can be selected for PEBS (e.g. L1, L2 cache misses and DTLB misses). It also allows only one PEBS event to be measured at a time. For other events that do not support PEBS, but only Imprecise event-based sampling (IEBS), it is not possible to map the reported addresses back to the source program on a instruction- or basic block-level. Method-level information could be still recovered to a certain extent, but very small methods may not be represented correctly since the displacement of IEBS samples can several basic blocks from the real event source instruction. Section 2.3.1 discusses the problems arising when using IEBS in more detail.

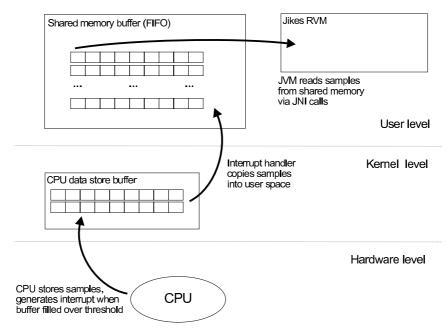

Figure 3.1 summarizes the system and how the different components interact with each other. The system consists of three main parts:

1. Perfmon loadable kernel module [56]<sup>1</sup>: This kernel module is part of the Perfmon infrastructure and is developed at HP. It offers the functions to access the performance counter hardware for a variety of hardware platforms. The kernel module hides the platform-specific details from the JVM. It also provides the interrupt handler that is called by the sampling hardware when the CPU buffer for the samples is full.

<sup>&</sup>lt;sup>1</sup>Available for download at http://www.hpl.hp.com/research/linux/perfmon/

#### 3.2. IMPLEMENTATION AND DESIGN ISSUES

Figure 3.1: Overview of the monitoring system.

- 2. Native shared library (C) [74]: Since we cannot call device drivers directly from Java or from the Jikes RVM we developed a native library to provide an interface to the kernel functions and access it via the Java Native Interface (JNI). This makes porting the system to other Java VMs (that support JNI) easier. We could not reuse libpfm (the user-space library provided with perfmon) because it does not support monitoring a process using PEBS like we do in our system.

- 3. Collector thread (Java): We use a separate Java thread that performs all monitoring tasks inside the JVM. It calls the native library for communication with the PMU and uses it to transfers HPM data from the kernel space into the JVM.

#### 3.2 Implementation and design issues

Since we are using Jikes RVM which is almost completely written in Java, most of our performance monitoring module is also implemented in Java except for the native library that provides the JNI interface to perfmon.

The copying of samples into user-space is necessary to allow the use of a different hardware platform with very few changes to the user-space library. The library is not limited to Java and can also be used from other runtime environments. Basically, the system can also be integrated with other Java VMs that support JNI. In principle it is also possible to monitor programs written in C or C++. This aspect, however, is not central to this work.

#### 3.2.1 User-space library

This section gives a short overview of the PEBS library that serves as an interface from the VM to the perfmon kernel module. The library allows to read samples from the kernel module. The challenge here is to make the data exchange between Java and the kernel as efficient as possible.

In our system we could not use libpfm which is provided by HP with perfmon since it does not support the special PEBS features needed for our online performance monitoring system. Since libpfm does not include this functionality we need to access the HPM registers directly via the kernel module. For this purpose we implemented our own user-space library to give the Java VM access to the PEBS HPM facilities.

The main functions of the library are:

- Functions for startup and initialization of the hardware counters.

- Copying monitoring data (samples) from kernel space (DS area filled directly by the CPU) to the user(VM)-supplied buffer. The samples are returned from the native library in a Java int[].

- Calls for changing interval/monitoring during runtime: e.g. sampling interval or event type.

- Stopping monitoring and shutting down the HPM module.

There are two possibilities to transfer data from kernel space to user space (VM address space):

- 1. Transfer data via JNI: This is safe, but slow. JNI data transfers work via Java reflection. This has the advantage that it does not require coordinating with other VM activities like the GC thread.

- 2. Copy data directly into the Java object (array) without JNI interaction: This is much faster than using JNI calls to copy the data, but we have to make sure that the garbage collector does not interfere by moving the object that the native code is writing to. We provide a pre-allocated array to the native code. The library function then copies all collected samples into this array directly without any JNI calls. We have to disable the GC manually for the short period of time while samples are copied from kernel space. As a consequence the native code must not allocate any new Java objects, since this may trigger a garbage collection which is not possible while GC is disabled. In practice we did not find this to be a significant limitation.

In our native library we use the second approach (copying samples directly) since it reduces the overhead of processing the HPM samples significantly.

The HPM unit of the P4 supports only a limited number of events to be measured in PEBS mode. Since we rely on PEBS for an accurate mapping of event samples back

#### 3.2. IMPLEMENTATION AND DESIGN ISSUES

to the program source, our library is limited to this set of events. The following events (followed by their perfmon event qualifier) can be measured with using our performance monitoring library:

- L1 data load misses (REPLAY\_EVENT:L1\_LD\_EVENT)

- L2 data load misses (REPLAY\_EVENT:L2\_LD\_EVENT)

- DTLB load misses (REPLAY\_EVENT:DTLB\_LD\_MISS)

- DTLB store misses (REPLAY\_EVENT:DTLB\_ST\_MISS)

- All DTLB misses (REPLAY\_EVENT:DTLB\_ALL\_MISS)

- Memory loads/stores completed (FRONT\_END\_EVENT:TAGLOADS/TAGSTORES)

Note that the absolute numbers obtained when measuring these events do not always directly correlate with the real program behavior due to hardware limitations. E.g., the Intel P4 documentation [6] states that not all L2 misses are captured by the HPM unit. Another example concerns counting completed memory loads: Our own measurements show that when sampling completed loads, only about 50% of all loads are considered for sampling. However, this is still ok as long as we can ensure that the samples taken are not biased too much.

# 3.2.2 Modifications to the VM

At VM startup we load our shared library that provides access to the HPM hardware. Next, we initialize it using user-defined command-line parameters. The initialization takes the event identifier, an initial sampling interval and the sample buffer size as input parameters. If not specified further the system provides useful default values for missing parameters.

Then, the JVM starts a monitoring thread. We mark this thread it as a daemon thread. This means that the VM automatically kills it after all user threads have terminated and the VM shuts down (after the main application thread terminates). Figure 3.2 shows the activities of the monitoring thread in pseudo code. The monitoring thread wakes up periodically and polls for new samples. The polling interval is set to 100ms by default. After it read all available samples from the PEBS buffer it starts filtering and processing the raw data. In this step the system tries map each sample back to the original source code (Java bytecode). We discuss this processing step in more detail in Section 3.3. By processing samples in batches the cost of invoking the monitoring thread is amortized over a large number of collected samples.

The PEBS sample buffer should be allocated large enough so that it does not overflow between two invocations of the monitoring thread. We found that a size of 20K samples (800 Kbytes) is large enough for even the most demanding monitoring applications. During normal operation usually not more than 20% of the buffer is occupied. If an overflow

```

1  while(true) {

2     int[] samples = Read_PEBS_Samples();

3     if (samples.length > 0)

4         Process_PEBS_Samples();

5         Sleep(100ms);

6     }

```

Figure 3.2: Main loop of the monitoring thread running in the VM.

still occurs the HPM hardware stops collecting data temporarily and restarts only after the samples have been read out and processed. In this case the system just does not collect HPM data until the next polling interval.

# 3.2.3 Modifications to the compiler

24

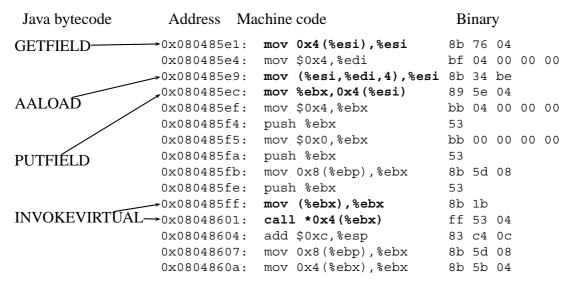

The raw performance monitoring data can only be useful for optimizations if we can map the raw data back to the original "source" program (Java bytecode in our case). For this purpose we need to store additional meta-information about the compiled code in the JIT compiler. This meta-information is necessary to identify the Java method and the bytecode instruction within the method for a given HPM sample. The next section (3.3) describes the mapping of HPM data back to the Java bytecode in detail.

# 3.3 Mapping HPM data to the source program

This section will present our approach to mapping HPM events back to the Java bytecode so that the information can be used for dynamic optimization in a JVM. We show the modifications necessary in the JVM to make this mapping possible.

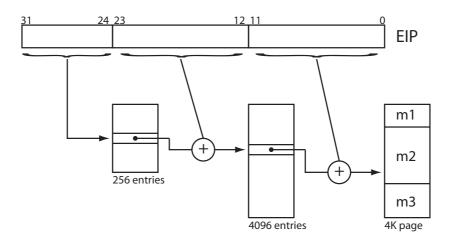

Depending on the underlying platform there are different difficulties in mapping the samples to the source code. For example, on the IA32 the reported program counter of a sample points to the instruction *after* the event-producing instruction. It is not trivial to navigate back one instruction on a variable instruction length architectures (CISC) like the IA32. Having a JIT compiler is clearly an advantage here: All meta-information about the machine code is available at run-time, and we can navigate in machine code on a variable instruction length architecture.

One sample on the P4 platform has a size of 40 bytes. It contains the program counter (EIP) where the sampled event occurred and the values of all registers at that time. To actually use the raw data for optimization, we need to obtain higher-level information about each sample. For identifying the Java bytecode instruction of a sample we only have to analyze the EIP register. The data register are only used if we are generating data address profiles as described later in Section 3.3.3.

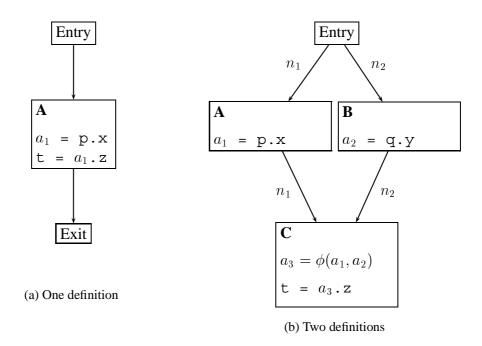

Program counter Java method Java bytecode Compiler IR

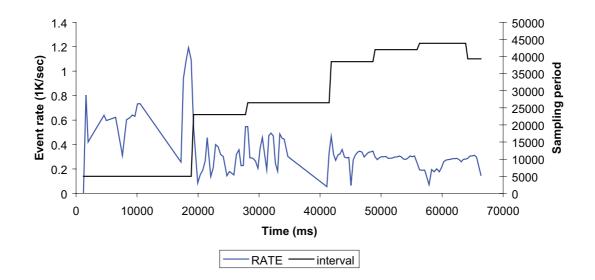

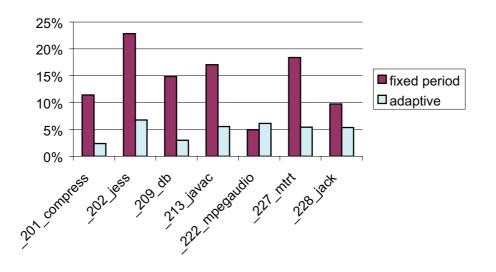

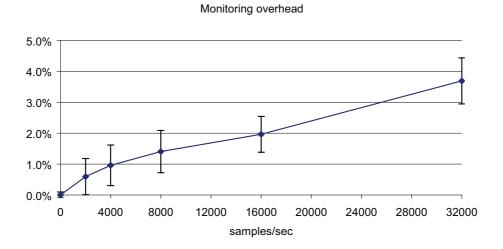

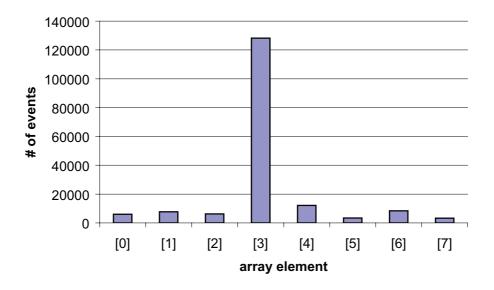

Figure 3.3: Process of finding the IR instruction from the program counter (EIP) given by the raw sample data.