DISS. ETH NO. 21347

## Neuromorphic Implementation of a Saliency-based Visual Selective Attention System

A dissertation submitted to

## ETH ZURICH

for the degree of Doctor of Sciences presented by

## **DANIEL EDUARD SONNLEITHNER**

Dipl.-Ing., Universität Karlsruhe (TH) 23. December 1982 citizen of Vully-les-Lacs, Switzerland

accepted on the recommendation of

Prof. Dr. Rodney Douglas, examiner Prof. Dr. Giacomo Indiveri, co-examiner Prof. Dr. Ernst Niebur, co-examiner

2013

TO INKEN MARIE.

# Disclaimer

I hereby declare that the work in this thesis is that of the candidate alone, except where indicated in the text, and as described below.

The description of experiments and results of creating a scan-path, Sec. 4.2, was already published in Sonnleithner and Indiveri [2012].

The use of "we" in the thesis refers to the above-mentioned people in the relevant sections.

## Abstract

Visual perception is one of our most important senses. To be able to see our eyes transform the light signal into spiking data streams. Our brain extracts from this data relevant information. To provide vision to a mobile robotic system both computational steps have to be implemented. With today's technology it is possible to build visual sensors with high resolution and high recording frame rates that dissipate little power. The sensors provide a clear, detailed view of the robot's environment. Therefore the first aspect of vision is implemented. The second aspect is to extract relevant information from the visual data. Information are relevant for the robot if they allow its interaction with the environment, e.g. determining its location or recognizing obstacles. Therefore, the extraction has to happen in real time.

The problem for the robot is to extract relevant information from the huge amount of visual data provided by its sensors in real time with limited computational resources.

In biology an analogy of this phenomenon can be observed: Our eyes provide far more data than the human brain can process. Nevertheless we are able to interact with our environment in real time. The mechanism that allows us to extract the relevant information from the data provided by our eyes in real time is called *selective attention* [Treisman and Gelade, 1980]: Only a subset of the visual data is processed in detail, the rest is discarded. A preprocessing system identifies regions in the visual space that are salient. The visual data from these regions is processed further by our brain in a serial fashion. An alternative to master the described problem is to adapt this bio-inspired strategy to robotics. In this thesis I present a neuromorphic multi-chip system that is derived from a saliency-based selective attention model [Koch and Ullman, 1985]. My proposed solution uses building blocks derived from the brain: emulates of neurons and synapses. Therefore, it achieves very efficient computations. To estimate the most relevant regions of the input scene the model uses a "saliency map": this map assigns to each pixel of the input image a value for its saliency. In the model, saliency is computed by using center-surround operations [Itti et al., 1998]. In this thesis I implement this operation by making use of a 2D-array of silicon neurons with excitatory and inhibitory synapses. The synaptic weights are realized with the help of a probabilistic mapping device. The selective attention model scans sequentially the regions of high saliency. I implement this operation by using a neuromorphic chip implementing a 2D-Winner-Take-All (WTA) network with Inhibition of Return (IOR) functionality. In order to control the operational parameters of the neuromorphic chips used in this thesis as well as for the communication of the individual chips with a workstation, I developed a custom hardware/software infrastructure. Furthermore, I present results of experiments conducted with the visual selective attention system to show its functionality.

By implementing the bio-inspired method of selective attention a mobile robot can better assign its computational resources to certain regions in the robot's visual input space. It is the first time that such an implementation of a selective attention system based on a neuromorphic multi-chip system is presented.

## Zusammenfassung

Sehen ist eines unserer wichtigsten Sinne. Um zu sehen, wandelt unser Auge das Licht in elektrische Impulse um. Das Gehirn extrahiert daraus relevante Informationen. Um einen mobilen Roboter mit der Fähigkeit des Sehens auszustatten, müssen beide Verarbeitungsschritte implementiert werden. Mittels heutiger Fertigungstechniken ist es möglich, sparsame Bildsensoren mit hoher Auflösung und hoher Aufnahmefrequenz zu bauen. Sie liefern scharfe, detailreiche Bilder der Umgebung des Roboters. Damit wird der erste Aspekt des Sehens ermöglicht. Der zweite ist, die relevanten Informationen aus den Bilddaten zu extrahieren. Informationen sind für den Roboter relevant, wenn sie ihm ermöglichen mit seiner Umgebung zu interagieren, z.B. seine Position zu bestimmen oder Hindernissen auszuweichen. Um dies zu gewährleisten, ist es nötig, dass die Bilddaten in Echtzeit verarbeitet werden.

Problematisch dabei ist, mit begrenzten Rechenkapazitäten die für den Roboter relevanten Informationen aus der riesigen Menge an visuellen Daten, die der Sensor zur Verfügung stellt, in Echtzeit zu extrahieren.

In der Biologie lässt sich ein analoges Phänomen beobachten: Unsere Augen liefern ein Vielfaches der Daten, die vom menschlichen Gehirn überhaupt verarbeitet werden können. Dennoch können wir mit unserer Umgebung in Echtzeit interagieren. Den Mechanismus, der die relevanten Informationen aus den Daten, die unsere Augen liefern, extrahiert, wird selektive Aufmerksamkeit genannt [Treisman and Gelade, 1980]: Nur ein Teil der Bilddaten wird im Detail verarbeitet, der Rest wird verworfen. Ein vorverarbeitendes System erkennt Bereiche im Sehfeld, die salient sind. Die Bilddaten dieser Bereiche werden von unserem Gehirn in sequentieller Weise weiterverarbeitet. Eine Möglichkeit das Datenproblem zu lösen, ist, diese Strategie aus der Biologie auf die Robotik zu übertragen. In dieser Arbeit beschreibe ich ein neuromorphisches Multi-Chip-System, dass von einem selektiven Aufmerksamkeitsmodell abgeleitet ist [Koch and Ullman, 1985]. Das neuromorphische Multi-Chip-System nutzt dem Gehirn nachempfundene Bausteine: Emulationen von Neuronen und Synapsen. Dadurch kann das System Berechnungen sehr effizient ausführen. Um die relevanten Bereiche im Eingangsbild zu erkennen, nutzt das Modell eine Salienzkarte. Diese Karte ordnet jedem Pixel des Eingangsbildes einen Wert für dessen Salienz zu. Im Modell wird die Salienz mittels Zentrum-Umfeld-Funktion bestimmt [Itti et al., 1998]. In dieser Arbeit implementiere ich diese Funktion mit Hilfe eines neuromorphen Chips bei dem künstliche Neuronen und erregende und hemmende Synapsen in zwei Dimensionen angeordnet sind. Die Gewichte der Synapsen werden mittels eines wahrscheinlichkeitsgesteuerten Mappers realisiert. Das Aufmerksamkeitsmodell scannt sequentiell alle Bereiche mit hoher Salienz. Ich implementiere diese Funktion mit Hilfe eines zweidimensionalen Winner-Takes-All Netzwerkes mit Inhibition of Return Funktionalität. Um zum Einen die Betriebsparameter der neuromorphen Chips einzustellen und zum Anderen die Kommunikation zwischen den Chips und einem Computer zu ermöglichen, habe ich eine Hardware/Software Infrastruktur entwickelt. Ausserdem beschreibe ich die Resultate von Experimenten, die mit dem selektiven Aufmerksamkeitssystem durchgeführt wurden, um seine Funktionsweise zu zeigen.

Durch die Anwendung der selektiven Aufmerksamkeitsmethode, die von der Biologie abgeleitet ist, können mobile Roboter ihre Rechenkapazitäten besser den relevanten Bereichen im Sichtbereich zuordnen. Das hier dargestellte System ist das erste selektive Aufmerksamkeitssystem, dass auf einem neuromorphen Multi-Chip-System aufbaut.

# Contents

| 1 | Introduction                                                           |                                                                      |                                                                        | 1          |  |  |  |

|---|------------------------------------------------------------------------|----------------------------------------------------------------------|------------------------------------------------------------------------|------------|--|--|--|

|   | 1.1                                                                    |                                                                      | s of selective attention                                               | 1          |  |  |  |

|   | 1.2                                                                    | Selecti                                                              | ve attention models are implemented using different technologies       | 3          |  |  |  |

|   | 1.3                                                                    | The pr                                                               | oblem addressed: a neuromorphic implementation of a selective atten-   |            |  |  |  |

|   |                                                                        | tion sy                                                              | stem                                                                   | 5          |  |  |  |

|   | 1.4                                                                    | Thesis                                                               | outline                                                                | 5          |  |  |  |

| 2 | Neuromorphic VLSI infrastructure necessary for the selective attention |                                                                      |                                                                        |            |  |  |  |

|   |                                                                        |                                                                      | mplementation                                                          | 7          |  |  |  |

|   | 2.1                                                                    |                                                                      | re neuromorphic devices controlled?                                    | 7          |  |  |  |

|   |                                                                        | 2.1.1                                                                | Controlling a single neuromorphic chip: the AMDA board                 | 7          |  |  |  |

|   |                                                                        | 2.1.2                                                                | Communication to the neuromorphic device via the AER bus               | 11         |  |  |  |

|   |                                                                        | 2.1.3                                                                | Address translating: the AER mapper                                    | 13         |  |  |  |

|   |                                                                        | 2.1.4                                                                | How do multiple neuromorphic devices communicate amongst each          |            |  |  |  |

|   | • •                                                                    | <b>T</b>                                                             | other?                                                                 | 14         |  |  |  |

|   | 2.2                                                                    |                                                                      | ree different neuromorphic devices used in this thesis                 | 18         |  |  |  |

|   |                                                                        | 2.2.1                                                                | The DVS: a visual neuromorphic sensor                                  | 18         |  |  |  |

|   |                                                                        | 2.2.2                                                                | A "general purpose" neuromorphic chip: the IF2DWTA                     | 18         |  |  |  |

|   | 0.0                                                                    | 2.2.3                                                                | A "selective attention chip": the SAC                                  | 19         |  |  |  |

|   | 2.3                                                                    | Concil                                                               | usion & Discussion                                                     | 20         |  |  |  |

| 3 |                                                                        | From theoretical models of attention to neuromorphic hardware imple- |                                                                        |            |  |  |  |

|   |                                                                        | ntation                                                              |                                                                        | 22         |  |  |  |

|   | 3.1                                                                    |                                                                      | ency-map based visual attention model                                  | 22         |  |  |  |

|   | 3.2                                                                    |                                                                      | n is an important selective feature                                    | 23         |  |  |  |

|   | 3.3                                                                    |                                                                      | ating the saliency by center-surround operations                       | 25         |  |  |  |

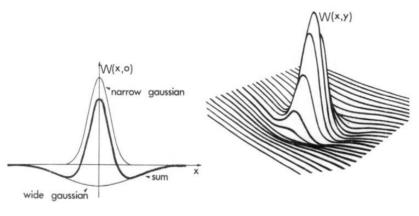

|   |                                                                        | 3.3.1                                                                | Center-surround operation found in the central nervous system          | 26         |  |  |  |

|   |                                                                        | 3.3.2                                                                | Theoretical consideration of ganglion cell's receptive field's weight  | 07         |  |  |  |

|   |                                                                        | <b>C</b> 1                                                           | parameters                                                             | 27         |  |  |  |

|   | 3.4                                                                    | Conclu                                                               | usion & Discussion                                                     | 30         |  |  |  |

| 4 |                                                                        |                                                                      | d experiments & their results                                          | 31         |  |  |  |

|   | 4.1                                                                    |                                                                      | ments incorporating center-surround                                    | 31         |  |  |  |

|   |                                                                        | 4.1.1                                                                | Stimulating inhibitory and excitatory synapses of a single neuron with |            |  |  |  |

|   |                                                                        |                                                                      | computer generated spike trains                                        | 31         |  |  |  |

|   |                                                                        | 4.1.2                                                                | Carrying out center-surround operation with stimuli provided by the    | <b>.</b> . |  |  |  |

|   |                                                                        |                                                                      | Dynamic Vision Sensor                                                  | 36         |  |  |  |

|              | 4.2             | Testing the generation of scan paths                            | 43 |  |  |  |  |  |

|--------------|-----------------|-----------------------------------------------------------------|----|--|--|--|--|--|

|              |                 | 4.2.1 Covert attention experiments                              | 43 |  |  |  |  |  |

|              |                 | 4.2.2 Overt attention experiments                               | 46 |  |  |  |  |  |

|              |                 | 4.2.3 Conclusion                                                | 48 |  |  |  |  |  |

|              | 4.3             | The neuromorphic selective attention system in action           | 49 |  |  |  |  |  |

|              |                 | 4.3.1 The details of the neuromorphic attention system          | 49 |  |  |  |  |  |

|              |                 | 4.3.2 Experiments                                               | 52 |  |  |  |  |  |

|              |                 | 4.3.3 The center-surround operation is essential for the system | 57 |  |  |  |  |  |

|              | 4.4             | Conclusion                                                      | 57 |  |  |  |  |  |

| 5            | Disc            | Discussion & Conclusions                                        |    |  |  |  |  |  |

|              | 5.1             | The system's context: Vision                                    | 59 |  |  |  |  |  |

|              | 5.2             | The presented system achieves different goals                   | 60 |  |  |  |  |  |

|              | 5.3             | The system in its historic context                              | 61 |  |  |  |  |  |

|              | 5.4             | The system compare to state-of-the-art                          | 65 |  |  |  |  |  |

|              | 5.5             | Possible application of the system                              | 66 |  |  |  |  |  |

|              | 5.6             | Outlook: Next possible steps                                    | 67 |  |  |  |  |  |

|              | 5.7             | Final Summary                                                   | 68 |  |  |  |  |  |

| Bibliography |                 |                                                                 |    |  |  |  |  |  |

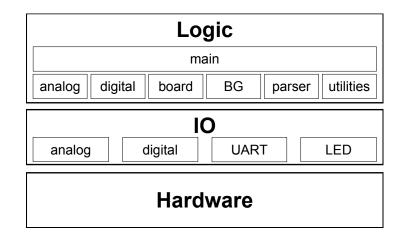

| Α            | AMC             | DA board firmware                                               | 79 |  |  |  |  |  |

|              | A.1             | Firmware structure                                              | 79 |  |  |  |  |  |

|              | A.2             | Programming the AMDA board's microcontroller                    | 82 |  |  |  |  |  |

| В            | B Abbreviations |                                                                 |    |  |  |  |  |  |

# **List of Figures**

| 1.1  | Schematic drawing of the visual attention model by Koch and Ullman [1985]                     | 3  |

|------|-----------------------------------------------------------------------------------------------|----|

| 2.1  | Client-server architecture to control AMDA boards                                             | 10 |

| 2.2  | The Address Event Representation bus                                                          | 11 |

| 2.3  | The organization of the mapper's memory                                                       | 14 |

| 2.4  | General schematic of an example multi-chip setup                                              | 15 |

| 2.5  | Addressing schema                                                                             | 17 |

| 2.6  | IF2DWTA chip topology                                                                         | 19 |

| 2.7  | SAC diagram                                                                                   | 20 |

| 3.1  | Saliency-based visual attention model                                                         | 23 |

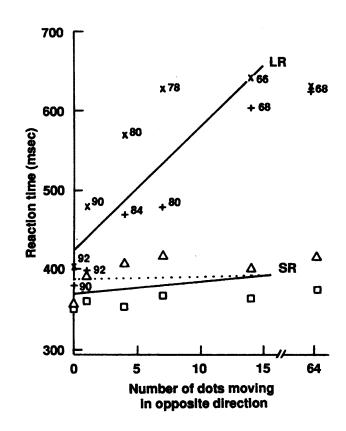

| 3.2  | Reaction times as a function of number of distractors                                         | 25 |

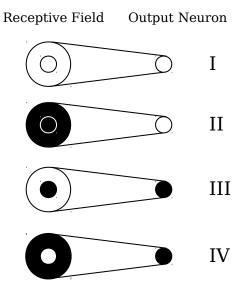

| 3.3  | Modeling the center-surround receptive field of a retinal ganglion cell                       | 26 |

| 3.4  | Extreme cases of ganglion cells with their receptive fields                                   | 28 |

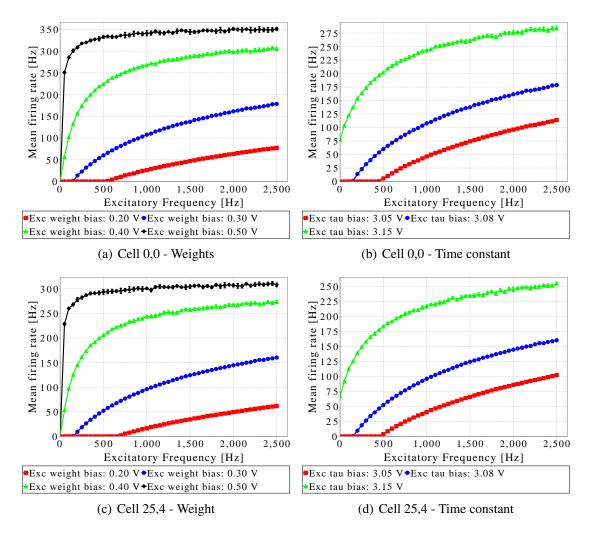

| 4.1  | Exploration of the excitatory synapse of the IF2DWTA chip                                     | 33 |

| 4.2  | Comparison of two methods of the neuron's excitation                                          | 34 |

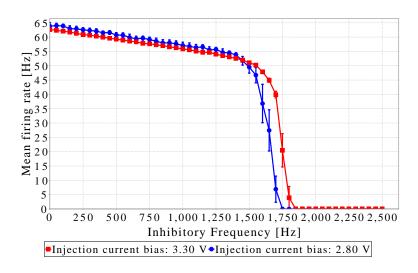

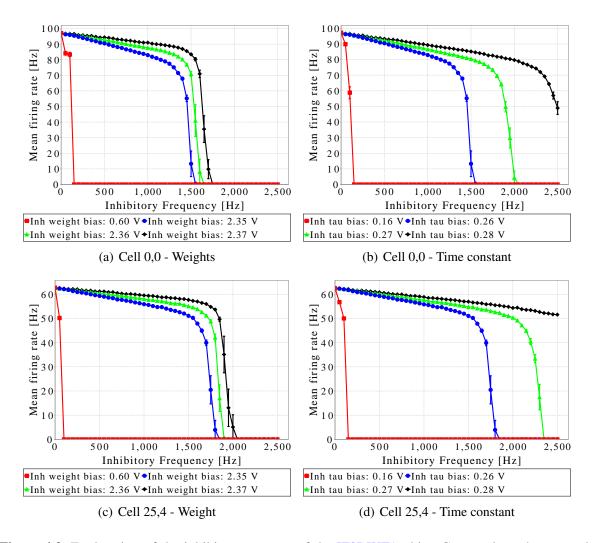

| 4.3  | Exploration of the inhibitory synapse of the IF2DWTA chip                                     | 35 |

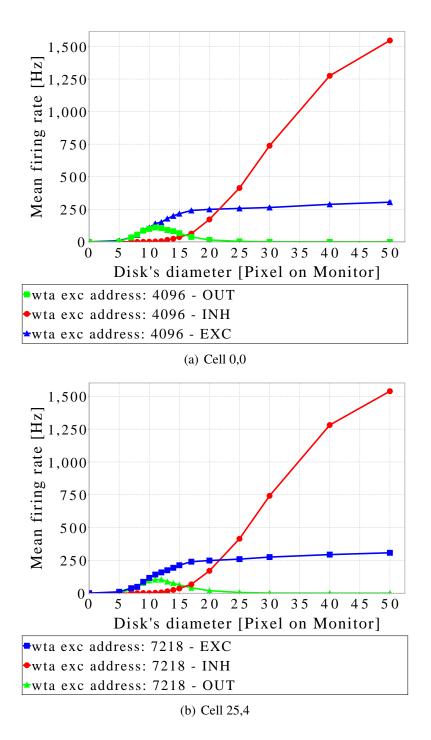

| 4.4  | "On"-cell experiments                                                                         | 38 |

| 4.5  | "Off"-cell experiments                                                                        | 40 |

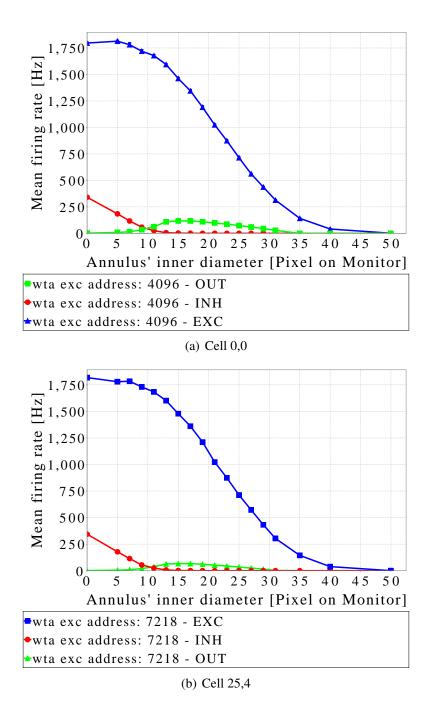

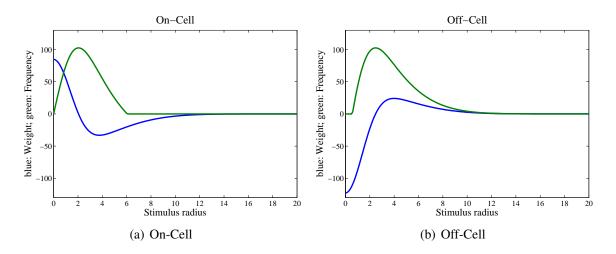

| 4.6  | Simulating "on"- and "off"-cell responses                                                     | 41 |

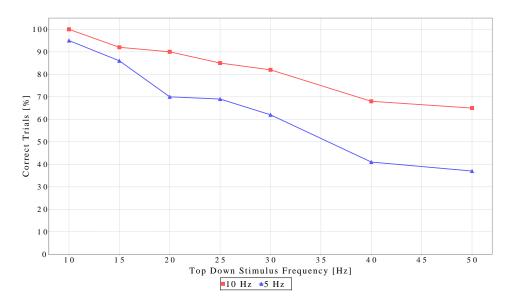

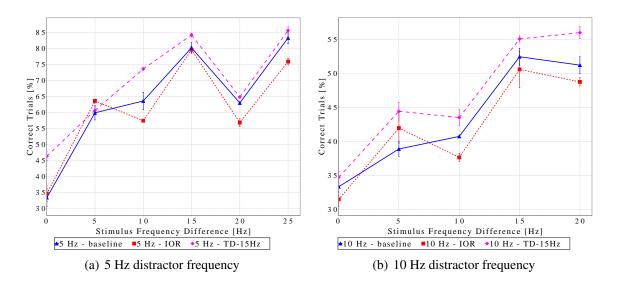

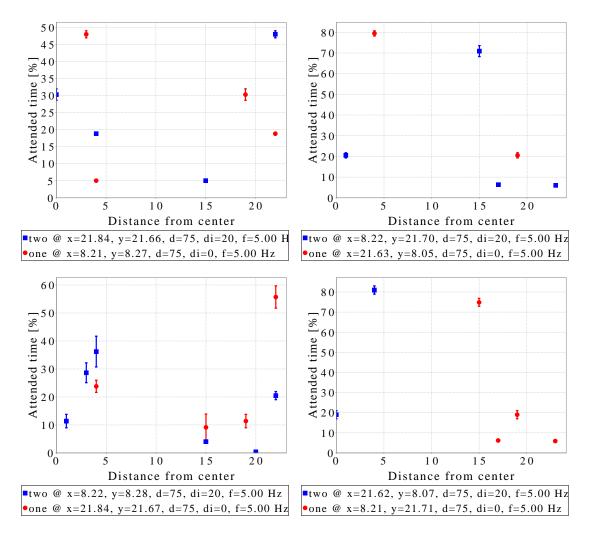

| 4.7  | Percentage of correct trials for different distractor frequencies                             | 44 |

| 4.8  | Percentage of correct trials for different baseline distractor and target stimulus            |    |

|      | frequencies                                                                                   | 46 |

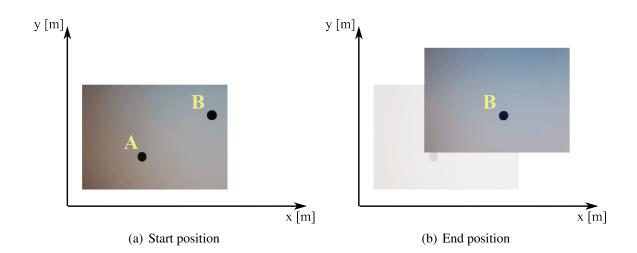

| 4.9  | Overt attention control experiment                                                            | 47 |

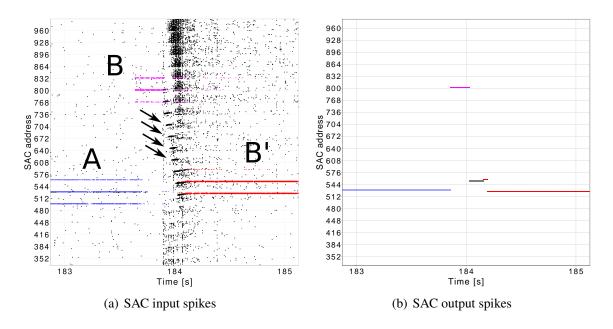

| 4.10 | Raster plots of spikes representing the SAC input and output                                  | 48 |

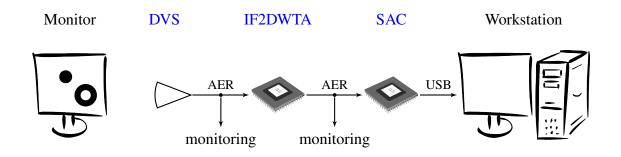

| 4.11 | Schematic of the neuromorphic attention system setup                                          | 50 |

| 4.12 | Schematic of the neuromorphic attention system's mapping                                      | 50 |

| 4.13 | Snap-shot of the stimulus and the event streams within the neuromorphic at-<br>tention system | 53 |

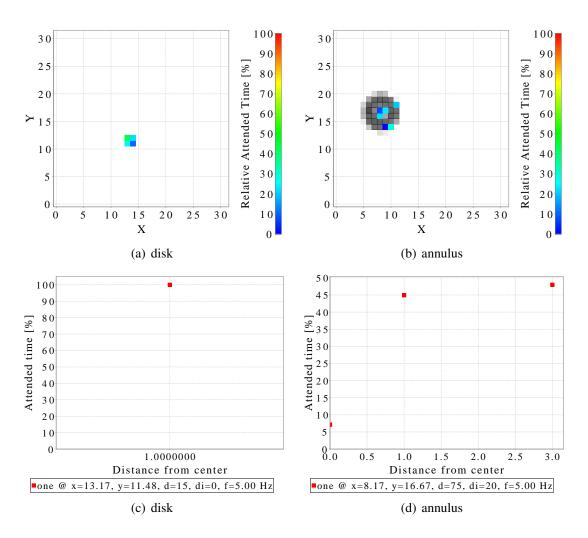

| 4.14 | Preferred stimuli presented to the neuromorphic attention system                              | 54 |

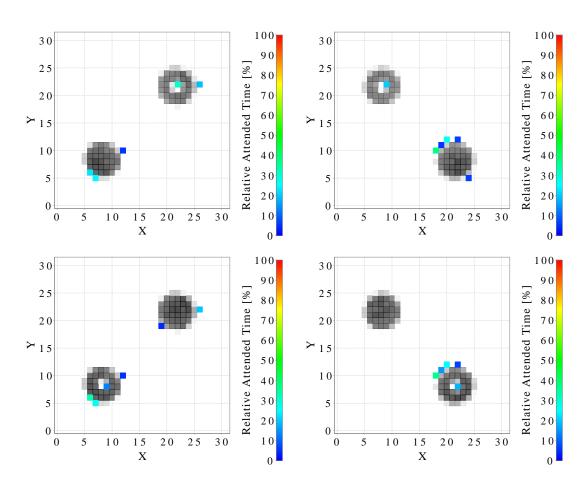

|      | Preferred vs non-preferred stimulus                                                           | 55 |

|      | Preferred vs non-preferred stimuli: distance from attended pixel to stimulus'                 | 55 |

|      | center                                                                                        | 56 |

| A.1  | Schematic of AMDA firmware                                                                    | 81 |

# **List of Tables**

| A.1 | Description of the content of the code files in the IO part    | 79 |

|-----|----------------------------------------------------------------|----|

| A.2 | Description of the content of the code files in the logic part | 80 |

## **1** Introduction

Even if our brain's whole computational capacity would be assigned to the visual system it could not process all the information provided by our retinas quickly enough to allow us to interact with our environment in real time [Tsotsos, 2005, Rensink et al., 1997]. Nevertheless, humans are able to react to visual stimuli within a few hundred milliseconds [Posner et al., 1980]. What is the brain's method to circumvent its limited resources but still allow us to interact in real time with our environment? The method is called selective attention: A preprocessing mechanism selects parts of the visual scene that are salient. Only salient regions are then processed by higher level brain areas. Usually more than one region in the visual scene is considered as salient. Hence the preprocessing mechanism is able to select more than one region and guide the higher level regions in a sequential manner through its selection. Salient regions are parts of the visual scene that are important to the observer. The importance is determined by the appearance and relation of visual features such as color, motion, orientation, size and others [Wolfe and Horowitz, 2004]. For example on the road red stop lights in front of us in a rainy and therefore mainly gray day will attract our attention. In these cases the saliency is driven from the input to the visual system. This is referred to the term "bottom-up" in the literature. The importance of a region does not only arise from the visual scene itself but is strongly influenced by the context of a task the observer performs. If we are looking for a friend at the crowded train station and know that she wears a red hat we bias our attention system such that we will recognize red objects more easily. This possibility to influence our attention system is referred to the term "top-down" [Connor et al., 2004].

Similar problems arise when constructing a vision systems for a robot to interact with its surrounding environment in real time: With today's technology it is easy to equip even small mobile devices with visual sensors able to provide huge amounts of data. But the processing of this data exceeds the available computational resources by orders of magnitudes. Especially in mobile applications the main constraints are due to the need of low power consumption and/or space restrictions. The problem of such devices is to identify regions within their visual space to which it is beneficial for them to allocate the limited processing resources to perform computationally expensive algorithms like character or face detection. The application of the strategy found in biology is a possible solution to that problem. The goal of this thesis is to implement a low power system using the described method inspired by biology to guide a technical system to locations for further investigations.

### 1.1 Models of selective attention

Several models of visual selective attention have been proposed during the last years. In this context one has to consider different issues and experimental paradigms: "space vs. object-

based attention, filtering tasks and visual search" [Heinke and Humphreys, 2005]. In this case the goal is to find locations in the visual space which are salient. Therefore computational models performing a space based visual search algorithm are of interest.

Many models describe attention as a spotlight that "shines" light onto a spatial defined part of the visual scene's computational representation leaving the non-attended parts in "shade". Strong support for such models comes from experiments that show that target detection times decrease when a valid cue is presented in advance [Eriksen and Hoffman, 1972, Posner et al., 1980].

One of the most influential models following these lines is the "feature integration theory" developed by Treisman and Gelade [1980]. The authors assume that visual perception is devided into two functionally independent and sequential stages. The first processing stages processes features and is preattentive. Features are values on different dimensions like color, orientation, spatial frequency etc. All features are processed in parallel, automatic and independently across the whole visual space. In a second processing stage different features at an attended location are combined and integrated to form objects.

Based on this theory two important streams of models were developed. Wolfe et al. propose a model for the visual search problem whereas several authors developed a series of models based on a proposal by Koch and Ullman.

Wolfe et al. [1989] cite several other authors and carry out a series of visual search experiments by themselves where the reaction time of subjects does not increase as expected with the number of distractors. Based on these observations they propose a model where the parallel and the serial stages are not completely separate: in cases where conjunctions of features define a target the parallel processing stage cannot distinguish distractors from targets. In the proposed model the result of the parallel stage's calculation is used to divide the objects into possible candidates for targets and distractors. Then the serial stage picks the target out of the candidates. This is much more efficient than picking the target out of all available objects. For this to work the parallel stage needs to know about the properties of the target object. This model was extended and optimized several times to be able to predict a even broader variety of experiments by the authors: Wolfe [1994], Wolfe and Gancarz [1997], Wolfe [2001, 2006].

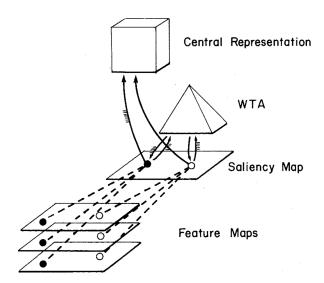

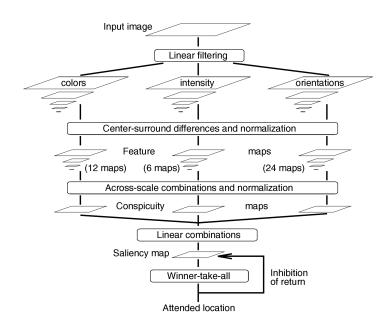

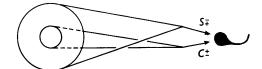

Based on Treisman's "feature integration theory" Koch and Ullman [1985] proposed a visual attention model: One of the authors' goal was to develop a model that can be implemented in a biologically plausible way. As Fig. 1.1 shows the model describes two stages: According to Treisman's theory the first stage performs operation on the whole visual space in parallel: For visual features like e.g. color, orientation and light intensity the first stage analyzes the whole visual scene. The output of this computation is a map per feature. These feature maps are combined into a saliency map. For each location in the visual scene this global map encodes the conspicuity. The model's second stage selects the location with highest conspicuity values from the saliency map. Koch and Ullman propose a network that performs a maximum operation on the map using "biologically motivated assumptions" [Koch and Ullman, 1985]. The result of the Winner-Take-All network is then the location within the visual scene with highest conspicuity. This location is transmitted to the central representation. Since only one location at a time can be selected and transmitted to the central representation this stage works sequentially.

Itti et al. [1998] describe a detailed implementation of Koch and Ullman [1985]'s model

**Figure 1.1:** Schematic drawing of the visual attention model by Koch and Ullman [1985]. The calculation of the feature maps as well as the saliency map is executed in parallel. The WTA networks picks the region with highest values of the saliency map and forwards its location to the central representation. (from Koch and Ullman [1985])

(see Fig. 3.1). Their attention model focus less on the biological plausibility but rather on the implementation details for simulations executed on computers. The model describes three processing stages: First, color, intensity, and orientation filters are applied to an image at different scales. In a second step, center-surround operations identify spatial discontinuities for each modality. The output of these operations is then combined to create a saliency map. Finally, a WTA network selects from the saliency map the region with maximum values. One method to not only select the region with highest saliency values but also other regions with high saliency values is IOR: After the WTA network chose a region its saliency values are set to zero. Then the WTA network will choose the region with the second highest saliency values. After its selection, again, this region is inhibited in the saliency map to be able to choose the third most salient regions. By this process a so-called scan path is created: The WTA chooses sequentially the regions with highest saliency values in a decreasing order. This model is used extensively and different details were subject for further investigation during the last recent years (e.g. Itti and Koch [2001b]). The model is often used as a basis for different extensions (e.g. Frintrop [2006]).

## 1.2 Selective attention models are implemented using different technologies

There are usually several different means to implement such models. Especially at the beginning of the development – to build a first proof of concept – a software implementation on workstations is considered. This solution stands out due to its flexibility: almost any computational problem can be solved by either using software packages or by writing own programs. Especially programming languages like Python [van Rossum, 1995] or MATLAB are feasible because they combine advanced computationally powerful built-in functions with an easy to learn syntax. Furthermore, today's computers provide enough power to run complex models as well as the possibility to trace back problems in their implementation. Example software implementations of Itti et al. [1998]'s model are iNVT<sup>1</sup> [Itti, 2004] using C++ or the Saliency Toolbox<sup>2</sup> [Walther, 2006] using MATLAB were developed during the last years. VOCUS [Frintrop, 2006] is another example of a software implementation using a different computation for the combination of intensity and color maps.

Later in development when a working proof of concept should be put into its "production" environment workstation are often too bulky and demand too much power especially if talking about mobile environments. Hence other approaches have to be considered. There are several possibilities: from implementations using microcontrollers via approaches based on Field Programmable Gate Arrays (FPGAs) to solutions with fully custom made Very Large Scale Integration (VLSI) devices. All these approaches have advantages and disadvantages. If the time of development is in focus usually solutions based on microcontrollers are quicker implemented than solutions based on FPGAs or a fully customized VLSI design. The customized design offers other advantages: Since only the functionalities that are really needed are included on such a device the design can be optimized for low power consumption. Considering computational power solutions based on a fully customized VLSI design achieves usually greater operation speeds than FPGA or microcontroller based solutions. These comparisons are true for digital implementations. When a solution based on a fully customized VLSI design achieves VLSI design is considered also analog or mixed analog/digital implementations are possible.

Brajovic and Kanade [1998] developed an analog two dimensional visual sensor implemented in VLSI technology that is able to track targets. The chip chooses from its visual input space the region with highest light intensity and locks on it. When the source of the light moves the chip is able to follow the target and reports its position in chip coordinates constantly. The authors argue that their chip implements a "rudimentary visual attention system"[Brajovic and Kanade, 1998]: It chooses objects based on their high light intensity which is one of several possible saliency feature in many models of visual attention.

Morris and DeWeerth [1997] designed similar devices: In their paper they present a one dimensional 20 pixel attention system implemented using analog VLSI technology. Because Brajovic and Kanade [1998] are more interested in a reliable tracking than a biological inspired attention system the authors did not implement the inhibition of a selected target as suggested by Koch and Ullman [1985]. Morris and DeWeerth [1997] implemented circuits that perform the Inhibition of Return (IOR) operation. In Morris et al. [1998] the authors extend their approach by being able to not only perform selective attention on a pixel but on a object basis. Therefore their chip groups several pixel to a larger pixel that is entitled as an object. Finally, the same group also developed a two dimensional version of their chip that is presented in Wilson et al. [1999].

The two mentioned approaches share as common property: they are both based on analog VLSI technology. Ouerhani et al. [2002] claim to present the first full implementation of the

<sup>&</sup>lt;sup>1</sup>http://ilab.usc.edu/toolkit

<sup>&</sup>lt;sup>2</sup>http://www.saliencytoolbox.net

visual attention model by Itti et al. [1998] in hardware: They present a Single Instruction Multiple Data (SIMD) analog/digital chip able to calculate feature maps at different scales, executing the center-surround operation and fusing the maps to a saliency map. Instead of implementing an IOR operation their implementation selects the most salient regions at once and transfer them via a Direct Memory Access (DMA) interface to a workstation. Further details to their implementation is described in Ouerhani and Hügli [2003].

An emerging field of technology that is in particular suited for systems with limitations in space and/or power is Neuromorphic Engineering [Mead, 1989]. As the name suggests Neuromorphic Engineering tries to emulate neurons with the help of electronic devices. Neuromorphic VLSI chips make use of transistors operating in the subthreshold regime to build low-power neuronal processing systems that emulate physical properties of biological neurons. Neuromorphic chips contain therefore electronic analogs of synapses and neurons that use spikes for both computation and communication. The latter is implemented by routing these spikes by a digital, asynchronous event based bus among chips and workstations.

This technology was also used to implement visual attention systems: Based on his work presented in Indiveri [1999] and Indiveri [2000b] the author presents a stand alone two dimensional neuromorphic attention chip [Indiveri, 2000a]. Instead of the work presented above this chip does not incorporate a sensor itself – it needs sensory input from external sources interfaced with the Address Event Representation (AER) bus. This allows to use the attention chip with other sensory modalities than only visual. The chip is comprised of  $8 \times 8$  cells interconnected with a WTA network. This network chooses the cell with the highest input amongst the others. The WTA current is fed to the neuronal circuit connected to the winning cell. The generated events are sent via the AER bus off chip. Also the IOR feature is implemented by making use of the cell's output neuron. Based on this work Bartolozzi [2007] developed a chip similar to the described one but with a larger number of cells ( $32 \times 32$ ). This chip is also used in this thesis.

## 1.3 The problem addressed: a neuromorphic implementation of a selective attention system

As described in the previous section neuromorphic engineering was already used to implement parts of an visual selective attention model [Indiveri, 1999, 2000a,b, Bartolozzi, 2007]. All these systems are based on the theoretical attention model proposed by Itti et al. [1998]. They implement the model's last stage and hence expect a saliency map as input.

In this thesis I extend previous approaches by implementing also the second stage – the center-surround operations – with the help of neuromorphic chips. Therefore, I build on the work of Bartolozzi [2007] to extend the infrastructure necessary to operate neuromorphic chips and incorporate a second neuromorphic chip within the system. Combining the creation of the saliency map with the existing mechanisms for choosing salient regions from the saliency map creates a selective attention system fully implemented with neuromorphic hardware.

This implementation is important for several reasons: It shows that it is possible to im-

plement a model with several stages with neuromorphic hardware. Furthermore the implementation shows that it is possible to use neuromorphic hardware for a useful task, namely to identify and localize salient regions in a visual input space in real time with low-power devices.

## 1.4 Thesis outline

This thesis is structured in three parts. In Chap. 2 I describe the toolkit used to implement the proposed neuromorphic selective attention system. It consists of a device that is able to set parameters and enables the communication for the neuromorphic chips. Furthermore the communication infrastructure that connects multiple neuromorphic device and workstations is addressed. Finally, I describe briefly the used neuromorphic devices themselves. In Chap. 3 I describe the model on which the system is based on in detail. Then I reason about the limitations of the presented attention system given that the sensor used is not able to detect color and static images. Then I evaluate theories of center-surround operations that researchers of cat's retina proposed. Even though their insights were collected in the eye I use their results to implement the necessary operations for my selective attention system. In Chap. 4 I describe experiments conducted. My approach is to test first the building blocks of the neuromorphic system and then show the results obtained by combining the different pieces. The thesis ends with a conclusion to summarize the findings and point out the most important achievements.

# 2 Neuromorphic VLSI infrastructure necessary for the selective attention system's implementation

A broad variety of neuromorphic hardware, such as neuromorphic chips, neuromorphic sensors, and their controlling infrastructure, was developed at the Institute of Neuroinformatics (INI) recently. The following chapter introduces the hardware that is used throughout this thesis, and presents my contributions to the infrastructure developed to use neuromorphic chips and systems. I describe how a single neuromorphic chip can be put into operation. Because I use more than one neuromorphic device I will introduce the communication infrastructure that connects chips and workstations, also starting from a single chip, to multi-chip setups.

## 2.1 How are neuromorphic devices controlled?

Neuromorphic Very Large Scale Integration (VLSI) chips make use of transistors operating in the subthreshold domain to build low-power neuronal processing systems that emulate physical properties of biological neurons. Neuromorphic chips contain therefore electronic analogs of synapses and neurons that use spikes for both computation and communication [Mead, 1989].

#### 2.1.1 Controlling a single neuromorphic chip: the AMDA board

The core idea of a neuromorphic chip is to emulate biological neurons and synapses with mixed analog/digital circuits in silicon [Mead, 1989]. The neuromorphic chips' parameters, such as the synapses' time constants and weights or the neurons' leaks or refractory periods, can be adjusted. This is necessary because at design time, not all parameters are known and it allows to use the chips for several applications. Changing a parameter of an electronic circuit means changing a voltage or a current on the device. Because it is easier to control voltages, current parameters are usually translated into voltage biases by using a current source on the device controlled by a voltage. The question of how few tens of parameters on a small chip can be controlled can be answered in several ways. One possibility is to put the chip on a Printed Circuit Board (PCB) equipped with controllable voltage sources such as potentiometers or Digital–to–Analog Converters (DACs) and connect their outputs with the input pads of the chip. Another possibility is to equip the chip with a bias generator, a circuitry that generates the necessary analog voltages on-chip [Delbruck and Van Schaik, 2005]. The information

of which voltage values to generate are transmitted to the bias generator by a simple digital interface, the Serial Peripheral Interconnect (SPI) bus.

Besides the parameters of a neuromorphic chip there is the problem of sending and receiving input and output signals to and from the chip. In the majority of animals the neurons communicate amongst each other with short electronic pulses called spikes. This communication method is also emulated by neuromorphic chips: Both, the input and the output signals to the neuromorphic chips are implemented digitally to mimic the spikes in biology. In contrast to an analog signal where a value is encoded e.g. by a voltage that lies between ground and the supply voltage, a digital signal is encoded in a binary fashion by a number of lines where the voltage for a single line can only be either ground or the supply voltage (high). If the line's voltage lies in between it is either considered invalid or interpreted either as ground or high. The means of connecting the digital lines of two different communication partners together is called a bus. One bus used to connect neuromorphic chips is called Address Event Representation (AER) bus.

Because both tasks, sending and receiving of in- and output signals as well as controlling the chip's parameters, have to be solved for almost every neuromorphic chip a standardized mean of providing these functionalities helps avoiding repeated development. Hence a PCB providing the necessary environment, meaning supply voltage, voltages controlling the neuromorphic chip's parameters, and the necessary communication interfaces for in- and outputs, was developed at INI: the AER Motherboard with D/A converters (AMDA). The idea is to have an advanced basis board with all necessary equipment with an easy to implement interface to different neuromorphic chips. Then after designing a new neuromorphic chip one can create a typically simple PCB – a so called daughter board – for this particular neuromorphic chip that can be put on the basis board. The interface between the AMDA and its daughter boards consists of three 64-pin sockets. Their purpose is to carry the daughter board and ensures the electrical connections between both PCBs. Note that typically only one daughter board is put on one AMDA board.

To create the necessary environment for neuromorphic chips the AMDA board is equipped with several devices: For the in- and outputs to and from the chip, the board provides two 20-pin connectors implementing the AER bus controlled by a Complex Programmable Logic Device (CPLD). The different voltages for the different parameters are created by 96 DACs. Analog voltages can be converted into digital values by eight Analog–to–Digital Converters (ADCs). Furthermore it is possible to set four digital pins and read from four digital pins. The first can be used e.g. to transmit voltage values to a built-in bias generator. All these components run at 3.3 V and are powered via an external power supply at 5 V.

How are all these electronic devices on the AMDA board controlled so that they can in turn control the parameters of the neuromorphic chip? The solution is a microcontroller sitting on the AMDA board with a connection to the user's workstation. On the one hand the micro-controller – an Atmel Mega128 – communicates with the electric components providing the environment for the neuromorphic chip via optical couplers. They separate the electric components electrically from the microcontroller to avoid crosstalk and other disturbing electrical influences between the purely digital microcontroller realm and the part of the AMDA board providing the neuromorphic chip's environment. On the other hand, the microcontroller is connected via a Serial-to-USB converter to a workstation from where the users sends com-

mands to adjust voltages and receives information about the state of the neuromorphic chip's environment. The second purpose of the connection between workstation and microcontroller is to provide its necessary power. Whenever the USB connector of an AMDA board is plugged into a Linux workstation a service program (udevd) reads the AMDA board's ID and creates a device file of the form /dev/amdaboardID where ID is replaced with the actual board ID. First, this methods makes it easy for programs running on the workstation to identify connected AMDA boards. Second, this device file is the interface for other programs to control the board's functions. If a board is disconnected, the same service program ensures that the generated device file is removed from the workstation's file system.

As part of my PhD project, I developed the firmware that runs on the AMDA microcontroller to manage the environment for the neuromorphic chips (see Appendix A). The principle design objective pursued during developing this software was to keep its complexity as low as possible and to move higher level functions (such as controlling the bias generator) to the controlling workstation. The firmware receives commands from the workstation and parses them. Depending on the command the necessary electric components to perform the requested action are then activated. After performing an action the firmware sends a reply message back to the workstation to confirm the action's execution. In case of an error an error message is sent back. Because each command sent results in a response message only one program can reliably communicate with the AMDA boards via its device file: If more programs read and write messages from and to one device file it is possible that one reads the response of the other and gets wrong values or assumes a malfunction. A possible solution to this problem is presented in the next section.

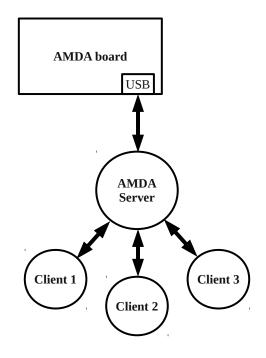

#### AMDA - server

The interface to the AMDA board seen from the workstation is a device file. In a common use case, a user would set up a GUI to visualize the bias voltages applied to the neuromorphic chip connected to the AMDA board. At the same time the user might run additional scripts that load predefined bias values to the chip and carry out experiments. Because both happen in parallel several programs would attempt to read and write commands to the same device file. Therefore, chances of interference are high. To manage such use cases, a possible solution is that only one program writes and reads messages to the device file and provides means to other programs to communicate with the AMDA board indirectly via this program. Because all messages have to be processed by this program it is able to handle possible interferences. Such a program is called a server program and the programs that communicate with this server are called clients (compare Fig. 2.1). This solution is a common paradigm in the world of information technology. In collaboration with other members of the team that use this infrastructure I developed such a client-server system.

The server is implemented using the programming language Python [van Rossum, 1995]. Clients communicate with the server via a TCP network connection. Therefore the client programs do not have to run on the workstation connected to the AMDA board but can be located anywhere in the network. This allows that users can work with the hardware controlled by this AMDA server remotely. Another advantage of using a standard network interface is that clients can be programmed in any programming language that supports handling network con-

Figure 2.1: To allow several programs to communicate with the AMDA board, a client-server architecture is used.

nections. Besides providing a single communication channel to the AMDA board(s) attached to it, e.g. to transmit new bias voltages values, the server also makes sure that values set by one client are distributed also to the other clients registered for the same board. With this method it is ensured that all clients operate always with up-to-date values.

To make it more convenient for the users the server starts whenever the first AMDA board is connected to a workstation. The same service program that creates the device files for the AMDA boards checks whether an AMDA server runs on the machine. If not the service program starts an instance of the server. If a server is already running it sends a message to the server requesting it to update its internal database with the newly connected AMDA board. When a AMDA board is disconnected from the server the service program also informs the server to remove the unlinked board from the database. This automatic update mechanism guaranties that the server is always "aware" of all connected AMDA boards that can be accessed by client programs.

To use neuromorphic chips they have to be put into a well defined environment: Few tens of parameters have to be set up by appropriate bias voltages. Also the communication to the chip's synapses and the spikes from the neurons has to be ensured. The last section described in detail the means of providing the bias voltages with the help of a standardized PCB, the AMDA board. I highlighted my contributions to this infrastructure in form of the board's firmware and the development of a server-client system allowing several programs to control the environment's bias values at the same time. The next section is going to focus on the second part of the environment by answering the question of how to handle the in- and outputs to and from the neuromorphic chip.

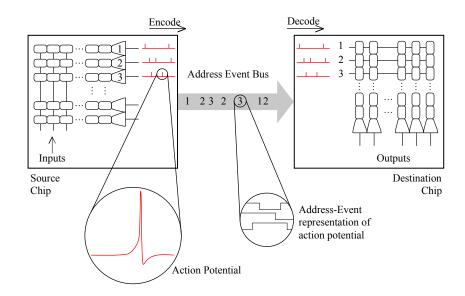

**Figure 2.2:** Whenever a neuron on the source chip generates an action potential, the neuron's address is transmitted by a digital bus to the destination chip. On the destination chip the addressed synapse generates a current that can be used for further computation. (Adopted from Deiss et al. [1998])

# 2.1.2 Communication to the neuromorphic device via the AER bus

In biological nervous systems neurons communicate with each other mainly by transmitting short electronic pulses, called action potentials or spikes which are generated at the axon hillock. These spikes are transmitted via the axon to the synapses that connect the neuron with its target neurons. This mechanism is reproduced by the electronic circuits of neuromorphic hardware: whenever the membrane potential of a silicon neuron crosses its threshold voltage it generates an action potential. In biology the spike would then be transmitted by a single wire – the axon – to the target neurons. Because one wants to be able to change the network topology after creating a neuromorphic chip, e.g. to use this chip for different applications with different neuronal networks, a more flexible approach than connecting neurons with wires defined at design time has to be taken (see Fig. 2.2): On the input side each synapse that should be accessible externally is encoded with an unique address. Whenever an address is sent to the chip a circuitry called arbiter resolves the address and generates a pulse at the synapse. Then an acknowledge signal is sent to the sender. Because the arbiter reacts immediately to incoming addresses it is not necessary to encode time separately: whenever a spike is sent it is applied, hence time encodes itself. On the output side, each neuron that should be able to send events to a receiver is encoded by an address. Similar to the input arbiter an output arbiter creates an address value of the neuron that generated the spike and sends the address immediately to a receiver. The receiver response with an acknowledge signal. Just like in biology the activity within neuronal networks working on neuromorphic hardware should be sparse in space and time. Therefore it is an unlikely case that more than one neuron spikes exactly at the same time point. Nevertheless, the output arbiter has to handle this case: it will choose one of the events to be sent first and will then send the other one. Because the digital circuitry that handles the spike communication works in the range of nanoseconds in contrast to the neurons that work in the order of milliseconds the time shift of an event does not affect the computation of the neurons on the neuromorphic chips considerably.

To connect senders and receivers of addresses a bus is used. Since it is not necessary to encode time explicitly the bus works in an asynchronous fashion: every spike event is immediately transmitted, whenever it is generated. Because only the address of an event emitting neuron is transmitted, the bus is called Address Event Representation (AER) bus. One of the first detailed descriptions can be found in Sivilotti [1991] and Mahowald [1992]. The input and output events to and from the chips uses the parallel AER (pAER) bus. The pAER bus is a straight forward implementation, that uses one wire per bit to transmit, plus one wire for each, request and acknowledge, i.e. the flow control signals.

In a multi-chip setup the communication amongst several neuromorphic chips at a time has to be ensured. Due to more chips producing more events the available bandwidth has to be increased. Therefore a more powerful implementation of AER, serial AER (sAER), was developed [Fasnacht et al., 2008]. Instead of using one wire per bit the sAER uses two pairs of wires to transmit 32 bit addresses serially. One pair is used for the data the other pair transmits flow-control signals. With this approach it is possible to achieve events rates up to 78.125 MHz for 32 bit address events. Because the AMDA boards are not equipped with sAER ports, the boards have to be extended by an AMDA EXtension board (AEX). These extension boards provide both a transmitting and receiving sAER port, two pAER ports and an USB port to communicate with a workstation.

Events are transmitted between AMDA and / or AEX boards in real-time. Since processing on workstations is not real-time capable, events transmitted to a workstation require their timing information to be preserved explicitly. Therefore the AEX has a built-in time counter with a 128 ns resolution. The counter is started as soon as the device file on the workstation is opened. Then the AEX assigns to each event that is transmitted to the workstation a 32 bit timestamp. A Field Programmable Gate Array (FPGA) controls the on-board communication. The AEX boards have to be powered externally with a 5 V power supply or they share the same power supply used by the AMDA board.

#### AEX – server

A workstation is able to monitor events generated by a neuromorphic chip connected to an AEX through the USB port. At the same time it is possible to stimulate synapses on the setup by sending events generated on the workstation to the AEX. Like the driver of the AMDA board the AEX driver provides a device file on the Linux workstation to provide a method to communicate with the AEX board, i.e. send stimulus events and monitor events. Again, if several programs want to read or write to the AEX, there is a high chance of interference. Similar to the client-server-architecture developed for the AMDA boards, I developed an AEX server to solve this problem. As opposed to the AMDA server, much more data, in form of address events, has to be written and read. Therefore one network port for reading and another one for writing is provide to client programs. This approach also reduces complexity of the clients' development because only the communication to the necessary functionality

(monitoring and/or stimulating), needs to be implemented.

Besides the bias voltages that have to be provided to a neuromorphic chip the communication in form of events to and from the chip has to be established. This is done by different implementations of the AER protocol. To let several client programs on a workstation communicate with one neuromorphic chip at the same time, I developed a client-server system: the AEX server. The address event schema is the basis to define different network topologies. The routing itself is executed by a specialized device that is described in the next section.

#### 2.1.3 Address translating: the AER mapper

A single chip setup consists of an AMDA board carrying the neuromorphic device, and an AEX board that transmits and receives events to and from the workstation. In this type of setup the workstation can generate stimulus events with the necessary addresses and can interpret the received addresses. If more than one chip is used, a device to translate the output addresses from the source chip to the input addresses of the destination chip is required. In Fasnacht and Indiveri [2011] the authors describe a mapper that is able to do this translation. It uses a PCI card equipped with a FPGA to communicate with the AEX boards: it has one sAER port to receive events and another one to send events. The memory of the workstation carrying the PCI card is configured such that it can be used as a look-up table. Whenever the device receives an address event it looks up the destination address(es) in the workstation's memory. Events are then emitted from the mapper to these addresses. The time necessary for this look-up operation is very small compared to the time constants of neurons or synapses: 0.8 µs.

The workstation provides 2 Gib of memory for the mapper's look-up table. For each input address, it is possible to define up to 512 output addresses (see Fig. 2.3). Each output address needs 32 bits to be defined. Therefore the input address space is 20 bits. This is less than the possible 32 bits address space that the AEX boards offer, but it is sufficient for the current setups: the pAER connections from and to the AMDA boards provide only 16 bits! Also the mapper's output address space does not offer the full 32 bit: The first bit is defined as the "stop"-bit. It is used to tell the mapper that this address is the last one to emit. The next seven bits are defined as "probability" bits. If they are all set – corresponding to a value of 127 – the mapper will always emit an event with the given address. If the value is smaller the mapper will only emit an event with a probability of  $p = \frac{value}{127}$ . Therefore if a received event should not generate any output event the first entry in the corresponding table should be 0x8000 0000. Finally, the remaining 24 bit define the output address.

Based on previous work, I developed a C library to generate the mapping table in the workstation's memory. Based on this library, the tools setMapping, addMapping, clearMappingTable, printDebugMappingTable, and printMappingTable were developed. Mapping information is saved in regular text files. The mapping tables have an input address and an output address separated by a space per line. In this case, the probability of sending an event to the output address if an event with the corresponding input address was given is set to one. To define a probability, a third column with values between 0 and 127 has to be added to each line.

By putting the mapper into a multi-chip setup a user can manipulate the addresses of events transmitted within the setup. This can be used to the user's advantage to define connections

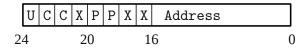

**Figure 2.3:** The organization of the mapper's look-up table in the workstation's memory. Each entry has 32 bit. The first bit is the "stop"-bit (SP). The next seven bits define the probability (PROB) of emitting an event to the output address. For a given input address, it is possible to define up to 512 output addresses. The maximum input address is 2<sup>20</sup> (0xF FFFF).

between different neuromorphic chips to specify a network topology.

# 2.1.4 How do multiple neuromorphic devices communicate amongst each other?

After describing the tools to control the parameters of neuromorphic chips and the devices that enable AER communication, in the following section I describe how these boards can be combined to build a setup consisting of multiple neuromorphic devices. The main question to answer is how several neuromorphic chips with different addressing schemes can be combined in a system to build logical networks of neurons for different applications. I use the term logical network to describe networks of neurons and synapses that a user develops to solve a certain task. In contrast the physical networks are the networks built with the electronic components, the AEX boards and the mapper described in the last sections.

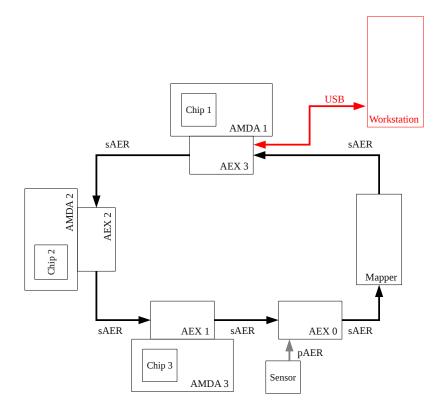

The first question to answer is the physical network topology that the AEX boards and the

**Figure 2.4:** General schematic of an example multi-chip setup: Up to four AEX boards and one mapper communicate to each other in a ring structure implemented by sAER links (the arrows show the transmission direction). The AEX 3 board additionally has a USB connection to the controlling workstation. This connection allows two functions: First, one can monitor events in the multi-chip setup. Second, events can be inserted to stimulate synapses on chips in the system. The AMDA boards communicate with their corresponding AEX via pAER (not shown explicitly). Neuromorphic sensors can also be incorporated into the system: they insert their events via a pAER link into the ring as shown on the AEX 0 board. The USB connections from the workstation to the AMDA boards to control the chips' parameters are not shown.

mapper will form. The constraints are the following:

- 1. Each AEX has one sAER port for receiving and one sAER port for transmitting events. The same is true for the mapper. Because there is only one output port available, there is no choice for the devices amongst several outputs where to send an event: Therefore there is no possibility to route events within the sAER bus.

- 2. It should be possible for every event in the system, independent of where it was generated, to reach every AEX board so that every event can be sent to every neuromorphic device connected to an AEX board. Additionally, to generate arbitrary logical network topologies with different neuromorphic chips it is necessary that all events in the system pass the mapper since this is the device used to manipulate addresses. Note that the AEX boards are also able to change addresses; in contrast to the mapper where it is easy to change the mapping tables reprogramming an AEX board is time consuming and hence not practicable to use it for establishing logical networks.

With a ring topology (see Fig. 2.4) all constraints can be fulfilled. This means that every device in the ring is connected with one successor. The output of the last one is connected to the first. (Since it is a ring, calling a device first or last is ambiguous anyway.) To monitor and/or insert events into the multi-chip system, one AEX is connected to a workstation via USB.

#### Each chip uses a specific channel

In an experimental setup with several neuromorphic devices it is necessary to know which device emitted which event and to which device a specific event is targeted to. Since the communication between different neuromorphic devices is achieved by the AEXs, events from/to two different AEXs have to be distinguished. Hence, the addresses generated by the neuromorphic devices are extended by an AEX specific tag. This tag is an ID, i.e. a number, that distinguishes different AEXs. The IDs are shown in Fig. 2.4. Because current neuromorphic devices uses up to 16 bit to address their synapses and neurons, the bits greater than 16 are used for this tagging.

The firmware running on the AEX' FPGA enables the routing between the different communication ports of the AEX. For each of the 6 routes from one port to another the firmware provides a set of filters:

1. Every received event has to pass a filter:

$$a_{min} \le a \le a_{max}$$

where *a* is the incoming address value,  $a_{min}$  a minimal address value and  $a_{max}$  a maximum address value.

2. If an event matches both conditions, the following operations are applied:

$$a' = (a \& m_{and}) \mid m_{or}$$

where a' is the resulting address value that is forwarded, & is the bitwise "AND" operator with the corresponding mask  $m_{and}$  and | is the bitwise "OR" operator with the corresponding mask  $m_{or}$ .

Given these rules, I developed an addressing schema for an efficient and flexible ring traffic (see Fig. 2.5):

Figure 2.5: Addressing schema: U: USB-flag, C: consumer, P: producer, X: free to user

• USB-flag: The AEX that communicates with the workstation via USB only forwards events to the workstation if this flag is set. Since this flag is at bit position 23, it can only be set by using an appropriate mapping on the mapper (the mapper only accepts events with bit length of 20 or smaller but is able to transmit events with a bit length of 24). With the help of that bit, the user can decide which events she wants to monitor. This is especially helpful when there is a lot of traffic within the ring: since the USB bandwidth is lower than the sAER bandwidth, the user can specify the interesting subset of events to be transmitted to the workstation.

To achieve this functionality, appropriate minimal and maximal addresses  $a_{min}$  and  $a_{max}$  and masks  $m_{and}$  and  $m_{or}$  have to be applied to the route from the incoming sAER-port to the USB-port.

- In bit 21 and 22 up to four target AEXs are encoded. By using appropriate  $a_{min}$  and  $a_{max}$  for the route from the input sAER-port to the output sAER-port, these two bits can be compared to the AEX' ID. If the event's and the AEX' IDs match, the channel information is removed from the event's address and it is sent to the pAER output port of the AEX. Thereby the event is removed from the traffic within the ring. This reduces the overall traffic within the ring. If the IDs do not match, the event is forwarded to the output sAER-port.

- Whenever an AEX receives an event at its input pAER port, it add its ID into the bits 18 and 19 and inserts the tagged event into the ring. This is done by an appropriate mask  $m_{or}$  in the pAER sAER route.

- A user of the addressing schema is free to use the bits in Fig. 2.5 marked with a 'X' for her own purpose. For example, if it becomes necessary to address more than 4 AEX, then the user could extend the channel bits with bit 20 and bit 17 respectively. In this case bit 16 can be used for other purposes.

By using this addressing schema it is possible to establish almost arbitrary connection between neurons on different neuromorphic devices. Due to the use of the filtering capabilities of the AEX boards it reduces the activity within the ring considerably. Since there are still unused bits in the address space it is possible to extend the schema to be used for up to eight AEX boards.

# 2.2 The three different neuromorphic devices used in this thesis

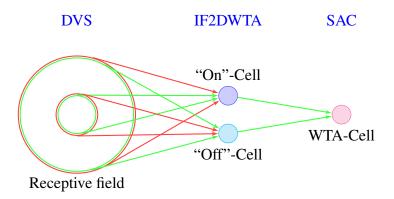

The multi-chip setup used in this work comprises of three different neuromorphic devices: The first is the Dynamic Vision Sensor (DVS), the second is a general purpose neuromorphic chip called Integrate & Fire 2–Dimensional WTA (IF2DWTA), and the third is a chip designed to detect maxima in its input: the Selective Attention Chip (SAC).

#### 2.2.1 The DVS: a visual neuromorphic sensor

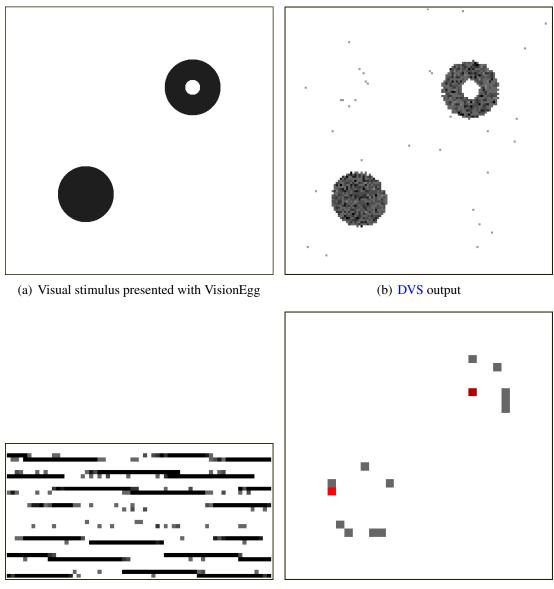

The DVS is the  $128 \times 128$  pixel sensor described in Lichtsteiner et al. [2008]. This sensor responds to temporal changes in the logarithm of local image intensity, thus encoding relative temporal changes in contrast, rather than absolute illumination (as in conventional cameras).

Thanks to the logarithmic compression, the DVS is able to detect contrast changes as low as 20% with a dynamic range spanning over 5 decades. Each pixel in the DVS performs this computation independently (local gain control), allowing the DVS to optimally respond to scenes with non-homogeneous illumination (e.g. outdoors or in environments with uncontrolled illumination). An important feature of the DVS, which makes it radically different from the sensors used in conventional machine vision approaches is the way it transmits output signals: signals are not scanned out on a frame-by-frame basis. Rather, the address of a pixel is transmitted on a shared digital bus, as soon as that pixel senses a difference in contrast. This "event" is written on the bus as it happens, in a completely asynchronous fashion. Each pixel address is written on the AER bus in real time, and potential conflicts (cases in which multiple pixels attempt to access the shared bus at the same time) are managed by an on-chip arbiter. As the DVS only transmits data when pixels sense sufficient contrast changes, redundancy in the data is strongly reduced (e.g. no data is transmitted and no bandwidth is used when there is no change in the visual scene). This produces a sparse image coding and optimizes the use of the communication channel, as well as the post-processing and storage effort. This, combined with the real-time asynchronous output nature of the DVS ensures precise timing information and low latency [Lichtsteiner et al., 2008] yet requires a much lower bandwidth than used by frame-based image sensors of equivalent time resolution [Delbruck, 2008].

The sensor is mounted on a PCB developed by Ángel Jiménez that provides access to the sensor's pAER bus. Therefore it can be easily incorporated into AER based hardware communication infrastructures.

#### 2.2.2 A "general purpose" neuromorphic chip: the IF2DWTA

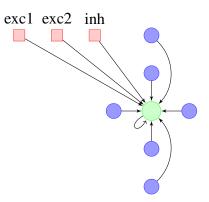

The IF2DWTA chip was developed by Elisabetta Chicca and Giacomo Indiveri. It contains a sheet of  $32 \times 64$  neurons. Each neuron is equipped with ten synapses, of which three can be accessed via AER. Two of the accessible synapses are excitatory, whereas the third is implemented as an inhibitory synapse. One synapse is connected recurrently to the neuron's output; the remaining six receive input from the nearest neighbors in both, x- and y-direction and the second nearest neighbors in y- direction (see Fig. 2.6). All synapses of one group,

**Figure 2.6:** The built-in connections of the IF2DWTA: every neuron is recurrently connected to itself. Additionally it receives input from its first nearest neighbors in both, x- and y- direction as well as the second nearest neighbors in y-direction. Finally, it can receive input from synapses that can be targeted from the AER bus: two are excitatory, one inhibitory. Red squares represent AER accessible synapses, blue circles neighboring neurons, and the green circle is the considered neuron.

e.g. the inhibitory synapses, share one weight that can be set via the AMDA board. Therefore the chip has ten different bias values for the ten groups of synapses.

The IF2DWTA was developed to provide a two dimensional Winner–Take–All (WTA) chip that is implemented by using a sheet of spiking neurons. By decoupling of some of the built-in connections, it is also possible to use the chip for several one dimensional WTAs. If all built-in connection strenths are set to zero, all neurons work independently. With the help of AER, the chip can then be used for any neuronal network that needs not more than two excitatory synapses and one inhibitory synapse per neuron.

Due to a bug in the acknowledge lines of the inhibitory synapses only half of them can be used: Only the synapses in the columns 0, 1, 4, 5, 8, 9, ..., 28, 29 work reliably.

The IF2DWTA was fabricated using a standard AMS  $0.35 \,\mu m$  CMOS process, and covers an area of about  $15 \, mm^2$ .

#### 2.2.3 A "selective attention chip": the SAC

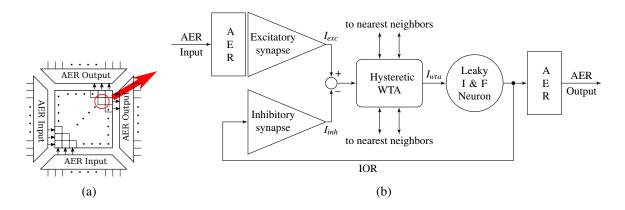

The SAC was developed to implement part of Itti et al. [1998]'s model of attention. Chiara Bartolozzi described it in detail in her PhD thesis [Bartolozzi, 2007].

The chip is comprised of an array of  $32 \times 32$  cells with AER digital circuits as well as analog neuromorphic circuits that implement silicon synapses, neurons, and additional signal processing stages. Figure 2.7(b) shows the block diagram of an SAC cell: each cell in the array receives input sequences of spikes; an input excitatory synapse integrates the spikes into an excitatory current  $I_{exc}$  which is then fed into a hysteretic WTA circuit [Indiveri, 2001]. The hysteretic WTA network compares the input currents of all cells and activates only the cell receiving the largest input current, while suppressing the output of all other cells. The winning cell will then produce a constant output current  $I_{wta}$ , which is independent of the

Figure 2.7: SAC diagram. (a) The SAC consists an array of 32 × 32 cells providing its computational resources and communicates with other hardware via AER receiver-transmitter circuits.

(b) Block diagram of one SAC cell. Each cell receives AER spikes from the input bus and competes for saliency by means of a hysteretic winner-take-all network connected to its neighbors via lateral connections. The winning cell sends its address to the output AER bus and self-inhibits via a local inhibitory synapse. All blocks are implemented with hybrid analog/digital circuits described in Bartolozzi and Indiveri [2009].

input, and source it to the cell's leaky Integrate & Fire (I&F) neuron. This circuit, fully characterized in Indiveri et al. [2006], produces voltage pulses (spikes) at a rate which is proportional to it's input current. Each time a spike is emitted from a neuron, it's address is sent off-chip via AER. In parallel, the spikes of the I&F neuron are sent to the cell's inhibitory synapse which generates a current  $I_{inh}$ . This implements a negative feedback loop in which the current integrated from the output spikes  $I_{inh}$  is subtracted from the excitatory input current  $I_{exc}$ . The net input current to the winning cell therefore decreases until another cell wins the competition. This self-inhibition implements a known mechanism in selective attention models named Inhibition of Return (IOR). It allows the network to shift from the currently attended stimulus to a different one, selecting sequentially the most active regions of the input space in order of decreasing activity, reproducing the attentional scan path [Itti and Koch, 2001a].

The SAC was fabricated using a standard AMS  $0.35 \,\mu m$  CMOS process, and covers an area of about  $10 \, mm^2$ .

### 2.3 Conclusion & Discussion

Throughout this chapter I described different hardware and infrastructure that is used for this thesis. I started with the environment for a neuromorphic chip: To let it work few tens of parameters in the form of voltages have to be set. Furthermore input events have to be transmitted to the device and the resulting output has to be handled. For a single neuromorphic chip this can be done by an AMDA board. For this PCB I developed the firmware and a serverclient communication infrastructure. If more than one chip should be used the AMDA board has to be extended by an AEX since this board provides a more powerful bus. Together with a mapper, an address translating device, one can build a multi-chip setup. By following the addressing schema I developed the setup can deal with devices that create events at a high frequency. An example for such a device is the Dynamic Vision Sensor (DVS), a neuromorphic vision sensor that I use in my project. I close this chapter with the descriptions of the other two neuromorphic chips used, the IF2DWTA and the SAC.