DISS. ETH NO. 23280

# Medium Voltage AC-DC Converter Systems for Ultra-Fast Charging Stations for Electric Vehicles

A thesis submitted to attain the degree of DOCTOR OF SCIENCES of ETH ZURICH

(Dr. sc. ETH Zurich)

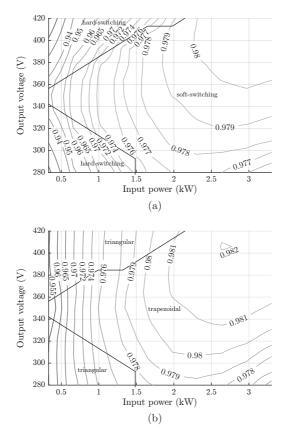

presented by

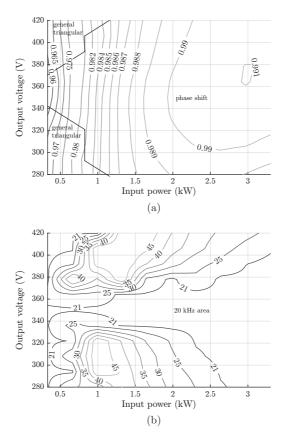

FELIX THOMAS JAUCH MSc ETH EEIT, ETH Zurich

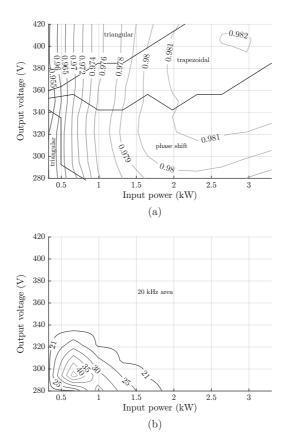

born on 19.01.1986 citizen of Villmergen AG, Switzerland

accepted on the recommendation of

Prof. Dr. Jürgen Biela, examiner Prof. Dr. ir. Johan Driesen, co-examiner

## Acknowledgement

First of all, I would like to thank Prof. Dr. Jürgen Biela for giving me the opportunity to do my doctoral thesis at the Laboratory for High Power Electronic Systems. I appreciate being one of the first team members of the new institute founded in 2010 and I am really grateful for the numerous inspiring and instructive discussions during the research work. I want to express my great gratitude also to Prof. Dr. ir. Johan Driesen for his interest in the thesis and being part of the examination committee. I highly value his suggestions and contributions resulting from the evaluation of the thesis.

The thesis was carried out in the context of the project Ultra-Fast Charging of Electric Vehicles (UFCEV) where I would like to thank Swisselectric Research and the Competence Center Energy and Mobility (CCEM) very much for their strong financial support of the work.

Furthermore, I would like to thank my students Daniel Christen, Marco Knaus, Dominik Neumayr and Simon Werffeli as well as our technician Emir Arnautović for their substantial contributions in terms of hardware and software work on the prototype systems.

Many thanks also go to my colleagues and friends at ETH Zurich for supporting me with their technical advices and also for providing a lively and enjoyable work and leisure atmosphere. Specifically, I thank all the members of the institute Sebastian Blume, Johannes Burkard, Christoph Carstensen, Daniel Christen, Simon Fuchs, Dominic Gerber, André Hillers, Tõnis Hõbejõgi, Michael Jaritz, Andreas Jehle, Dorca Lee, David Leuenberger, Dimosthenis Peftitsis, Jacqueline Perez, Tobias Rogg, Peng Shuai, Milos Stojadinovic and Jonas Wyss. Moreover, I thank David Boillat, Ralph Burkart, Matthias Kasper and Roger Wiget for the great time we had during our studies at ETH Zurich.

Finally, I give my sincere thanks to my parents Andrea and Thomas and my brothers Andreas and Clemens for their strong support and for always motivating me in any situation. A big thanks also goes to my partner Simone for her love and patience.

Felix Thomas Jauch Zurich, January 2016

### Abstract

The environmental impact of petroleum-based transportation infrastructure gained more and more significance during the last decade as fossil fuel powered vehicles lead to high emissions of  $CO_2$  and other greenhouse gases. With the electric mobility becoming a real solution for a sustainable future by using renewable energy sources, the emissions of carbon and in general greenhouse gases can be substantially reduced in order to mitigate the induced ecological effects.

For today's electric vehicles already featuring suitable (but limited) ranges and having advantages over vehicles driven by internal combustion engines as higher engine efficiency, regenerative braking and reduced noise emission, the key element for their success are the charging systems as well as the battery technology. To overcome the range limitations given through the long charging times so-called ultra-fast charging stations have to be developed with a charging power of several 100 kW preferably connected to the medium voltage AC grid which substantially increase the autonomy and the flexibility of electric vehicle drivers.

After presenting a brief motivation for the topic of the electric mobility in **Chapter 1** together with today's charging methods as well as available charging infrastructure, state-of-the-art research approaches for an ultra-fast charging station for electric vehicles with integrated energy storages are summarized.

In **Chapter 2** the design aspects for an ultra-fast charging station are given from which concepts for the realization are developed and the specifications and requirements for the power electronic converter system and the energy storage can be stated.

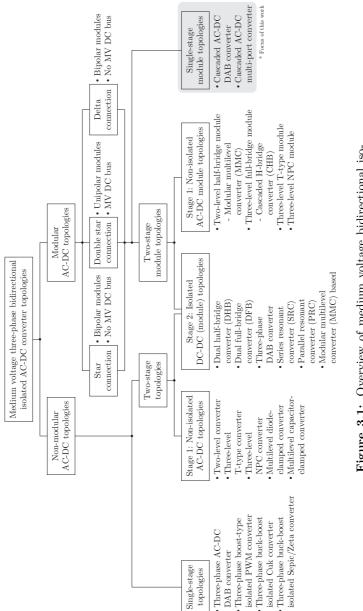

Then, state-of-the-art medium voltage bidirectional isolated AC-DC converter topologies suitable for the grid interface of an ultra-fast charging station are evaluated in **Chapter 3** with the focus set on the integration of a battery energy storage system as well as the integration of the galvanic isolation on module level from which two single-stage converter systems are identified for a further investigation.

The first converter system is the cascaded AC-DC dual active bridge

converter for a split battery energy storage system proposed in **Chap**ter 4. For the topology, suitable modulation and control schemes both on module as well as on system level are developed and a hardware prototype of a module is designed and built to experimentally verify the proposed modulation schemes. The overall battery energy storage system is simulated to validate the given theoretical analysis.

The second converter system is the cascaded AC-DC multi-port converter for a split battery energy storage system introduced in **Chapter 5**. For a three-phase AC-DC multi-port converter module, a new modeling approach for the power flows at the AC and the DC ports is presented and suitable modulation schemes are developed. Moreover, the converter module is simulated applying the different modulation schemes to validate the given theoretical analysis.

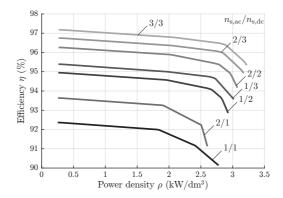

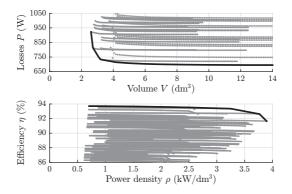

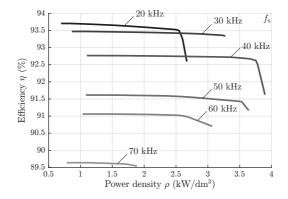

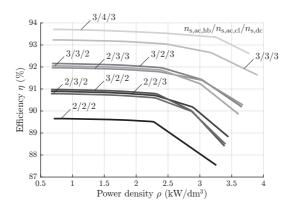

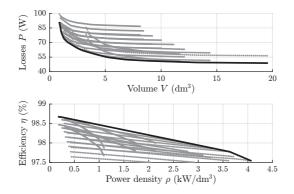

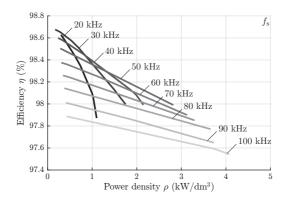

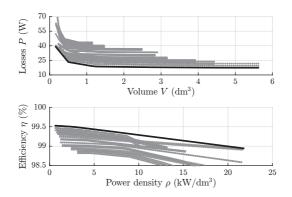

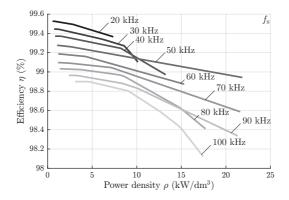

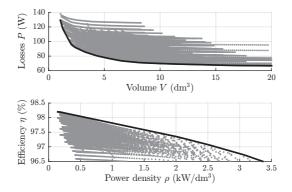

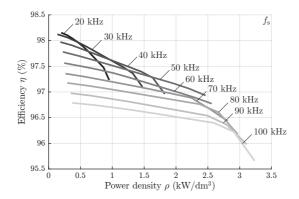

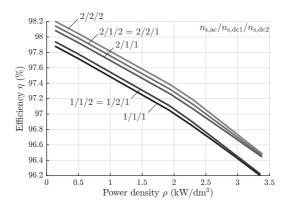

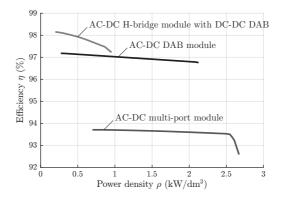

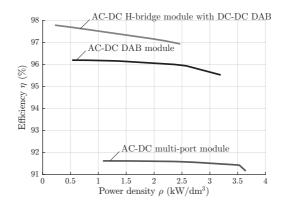

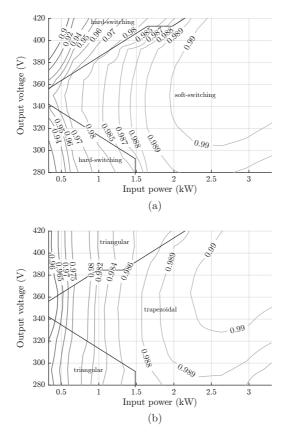

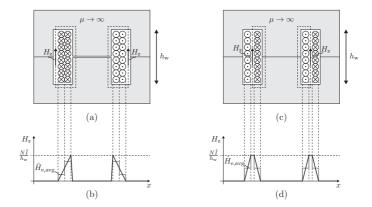

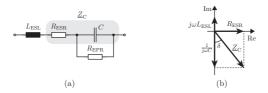

For the comparison of the proposed single-stage converter systems on module level to the state-of-the-art two-stage solution utilizing an AC-DC H-bridge module connected to a DC-DC dual active bridge converter in terms of efficiency and power density, a multi-objective optimization is implemented and the underlying power component models are described in **Chapter 6**. From the optimization results obtained the efficiencies achieved at a power density of 2.5 kW/L are for the single-stage AC-DC dual active bridge module 96.6%, for the single-stage AC-DC multi-port module 93.5% and for the two-stage AC-DC H-bridge module connected to a DC-DC dual active bridge converter 97.1%.

Finally, **Chapter 7** summarizes and concludes the main achievements of the thesis and presents an outlook on possible future research work.

# Kurzfassung

Im letzten Jahrzehnt gewannen die Auswirkungen der auf Erdöl basierten Transportinfrastruktur auf die Umwelt mehr und mehr an Bedeutung. Fahrzeuge betrieben mit fossilen Brennstoffen führen zu hohen Emissionen von  $CO_2$  und weiteren Treibhausgasen. Mit der Elektromobilität eröffnen sich Möglichkeiten für eine nachhaltige Zukunft durch den Einsatz erneuerbarer Energiequellen, um die Emissionen von Kohlenstoff und im Allgemeinen von Treibhausgasen wesentlich reduzieren zu können.

Heutige Elektrofahrzeuge verfügen bereits über eine angemessene wenn auch eingeschränkte Reichweite und bieten einige Vorteile gegenüber Fahrzeugen mit Verbrennungsmotoren wie eine höhere Motoreffizienz, das regenerative Bremsen sowie die reduzierte Geräuschemission. Das Schlüsselelement für den Erfolg sind die Ladesysteme sowie die Batterietechnologie. Um die Limitierung der Reichweite durch die langen Ladezeiten zu überwinden, müssen Schnellladestationen mit einer Ladeleistung von einigen 100 kW, vorzugsweise für den Anschluss an das AC Mittelspannungsnetz, entwickelt werden. Somit können die Autonomie und die Flexibilität der Benutzer von Elektrofahrzeugen gesteigert werden.

Nach einer kurzen Motivation zum Thema Elektromobilität in **Kapitel 1** mit ihren heutigen Lademethoden sowie der vorhandenen Ladeinfrastruktur, werden aktuelle Forschungsansätze für eine Schnellladestation für Elektrofahrzeuge mit integriertem Energiespeicher vorgestellt. In **Kapitel 2** werden die Designaspekte für eine Schnellladestation diskutiert, mit Hilfe derer Realisierungskonzepte erarbeitet und die Spezifikationen und Anforderungen an das leistungselektronische Konvertersystem und den Energiespeicher aufgestellt werden können. Danach werden in **Kapitel 3** bidirektionale isolierte AC-DC Konvertertopologien für die Mittelspannungsanbindung gemäss dem Stand der Technik hinsichtlich der Verwendung in einer Schnellladestation evaluiert mit dem Fokus der Integration eines Batteriespeichersystems sowie der Integration der galvanischen Trennung auf Modulebene. Zur weiteren Betrachtung werden zwei einstufige Konvertersysteme identifiziert. Das erste Konvertersystem stellt den kaskadierten AC-DC Dual Active Bridge Konverter für ein gesplittetes Batteriespeichersystem vorgeschlagen in **Kapitel 4** dar. Für die Topologie werden geeignete Modulationsund Steuerverfahren auf Modul- sowie Systemebene entwickelt, welche mittels dem Design und Aufbau eines Hardwareprototyps experimentell verifiziert werden. Zudem wird das gesamte Batteriespeichersystem simuliert, um die theoretische Analyse zu validieren.

Das zweite Konvertersystem stellt den kaskadierten AC-DC Multi-Port Konverter für ein gesplittetes Batteriespeichersystem eingeführt in **Kapitel 5** dar. Für ein dreiphasiges AC-DC Multi-Port Konvertermodul werden ein neuer Modellierungsansatz für die Leistungsflüsse an den AC und DC Ports beschrieben sowie geeignete Modulationsverfahren entwickelt. Des Weiteren wird ein Konvertermodul zur Verifikation der theoretischen Analyse der verschiedenen Modulationsverfahren simuliert.

Zum Vergleich der vorgeschlagenen einstufigen Konvertersysteme auf Modulebene mit dem zweistufigen Ansatz der Stand der Technik bestehend aus einem AC-DC Vollbrückenmodul verbunden mit einem DC-DC Dual Active Bridge Konverter hinsichtlich Effizienz und Leistungsdichte wird in **Kapitel 6** eine mehrkriterielle Optimierung implementiert sowie die zugrundeliegenden Modelle der Leistungskomponenten erläutert. Anhand der Resultate der Optimierung kann bei einer Leistungsdichte von  $2.5 \, \text{kW/L}$  mit dem einstufigen AC-DC Dual Active Bridge Konvertermodul eine Effizienz von 96.6 %, mit dem einstufigen AC-DC Multi-Port Konvertermodul eine Effizienz von 93.5 % und mit dem zweistufigen AC-DC Vollbrückenmodul verbunden mit einem DC-DC Dual Active Bridge Konverter eine Effizienz von 97.1 % erreicht werden.

Abschliessend werden in **Kapitel 7** die wichtigsten Errungenschaften dieser Arbeit zusammengefasst und ein Ausblick auf mögliche zukünftige Forschungsthemen gegeben.

# Glossary

#### Abbreviations

| 2D                   | <br>Two Dimensional                                   |

|----------------------|-------------------------------------------------------|

| 3D                   | <br>Three Dimensional                                 |

| AC                   | <br>Alternating Current                               |

| CHAdeMO              | <br>Charge de Move                                    |

| CHB                  | <br>Cascaded H-Bridge Converter                       |

| CSPI                 | <br>Cooling System Performance Index                  |

| DAB                  | <br>Dual Active Bridge                                |

| DC                   | <br>Direct Current                                    |

| DFB                  | <br>Dual Full-Bridge                                  |

| DHB                  | <br>Dual Half-Bridge                                  |

| DUT                  | <br>Device Under Test                                 |

| EMI                  | <br>Electromagnetic Interference                      |

| $\mathbf{EPR}$       | <br>Equivalent Parallel Resistance                    |

| ESL                  | <br>Equivalent Series Inductance                      |

| $\mathbf{ESR}$       | <br>Equivalent Series Resistance                      |

| $\mathrm{EV}$        | <br>Electric Vehicle                                  |

| FEM                  | <br>Finite Element Method                             |

| $\operatorname{FET}$ | <br>Field-Effect Transistor                           |

| FPGA                 | <br>Field-Programmable Gate Array                     |

| HVDC                 | <br>High Voltage Direct Current                       |

| IEC                  | <br>International Electrotechnical Commission         |

| IGBT                 | <br>Insulated-Gate Bipolar Transistor                 |

| iGSE                 | <br>Improved Generalized Steinmetz Equation           |

| IT                   | <br>Isolé Terre                                       |

| LUT                  | <br>Lookup Table                                      |

| LV                   | <br>Low Voltage                                       |

| $\mathrm{MF}$        | <br>Medium Frequency                                  |

| MMC                  | <br>Modular Multilevel Converter                      |

| MOSFET               | <br>Metal-Oxide-Semiconductor Field-Effect Transistor |

| MV                   | <br>Medium Voltage                                    |

| NEDC          | <br>New European Driving Cycle                  |

|---------------|-------------------------------------------------|

| NPC           | <br>Neutral Point Clamped                       |

| OSG           | <br>Orthogonal System Generator                 |

| PCB           | <br>Printed Circuit Board                       |

| $\mathbf{PF}$ | <br>Power Factor                                |

| PFC           | <br>Power Factor Correction                     |

| PLL           | <br>Phase-Locked Loop                           |

| PRC           | <br>Parallel Resonant Converter                 |

| PWM           | <br>Pulse Width Modulation                      |

| RMS           | <br>Root Mean Square                            |

| SOC           | <br>State of Charge                             |

| SOGI          | <br>Second Order Generalized Integrator         |

| SRC           | <br>Series Resonant Converter                   |

| SST           | <br>Solid State Transformer                     |

| STATCOM       | <br>Static Synchronous Compensator              |

| THD           | <br>Total Harmonic Distortion                   |

| V2G           | <br>Vehicle to Grid                             |

| VHDL          | <br>Very High Speed Integrated Circuit Hardware |

|               | Description Language                            |

| ZCS           | <br>Zero Current Switching                      |

| ZVS           | <br>Zero Voltage Switching                      |

#### Mathematical notation

| x               | <br>Instantaneous value of $x$                                  |

|-----------------|-----------------------------------------------------------------|

| X               | <br>RMS or DC value of $x$                                      |

| $\hat{X}$       | <br>Peak value of $x$                                           |

| $\underline{X}$ | <br>Complex phasor $Ae^{j\phi}$ of $x = A\cos(\omega t + \phi)$ |

| $\overline{X}$  | <br>Complex conjugate of phasor $\underline{X}$                 |

| $X^*$           | <br>Reference RMS or DC value of $x$                            |

| $\hat{X}^*$     | <br>Reference peak value of $x$                                 |

| x'              | <br>x referred to the primary or the AC side of a transformer   |

$x_{bi}$  ... Value of x belonging to a module i in phase b

# Table of Contents

| 1        | Intr | oducti  | ion                                         | 1         |

|----------|------|---------|---------------------------------------------|-----------|

|          | 1.1  | Motiv   | ation                                       | 1         |

|          | 1.2  | Objec   | tives and contributions                     | 8         |

|          | 1.3  | Outlin  | ne of the thesis                            | 10        |

|          | 1.4  |         | f publications                              | 12        |

| <b>2</b> | Ult  | ra-Fast | t Charging Station for Medium Voltage Grids | 15        |

|          | 2.1  | Design  | n aspects                                   | 15        |

|          |      | 2.1.1   | Utilization                                 | 16        |

|          |      | 2.1.2   | EV battery capacity                         | 16        |

|          |      | 2.1.3   | Charging time                               | 17        |

|          |      | 2.1.4   | Galvanic isolation                          | 18        |

|          |      | 2.1.5   | Summary and discussion                      | 18        |

|          | 2.2  | Conce   | epts for realization                        | 19        |

|          |      | 2.2.1   | Medium voltage DC bus                       | 20        |

|          |      | 2.2.2   | Integrated battery energy storage           | 22        |

|          |      | 2.2.3   | Focus of this work                          | 22        |

|          | 2.3  | Specif  | ications and requirements                   | 23        |

|          |      | 2.3.1   | Charging power                              | 23        |

|          |      | 2.3.2   | Energy storage                              | 25        |

| 3        | Bid  | irectio | nal Isolated AC-DC Converter Topologies     | <b>27</b> |

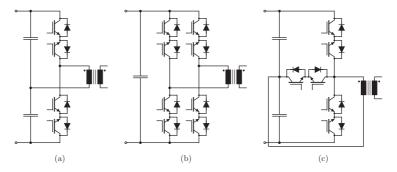

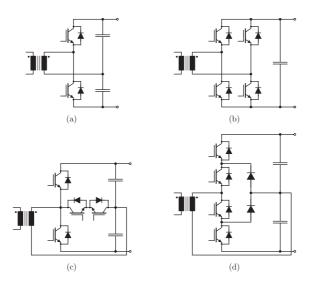

|          | 3.1  |         | nodular AC-DC topologies                    | 29        |

|          |      | 3.1.1   | Two-stage topologies                        | 30        |

|          |      | 3.1.2   | Single-stage topologies                     | 32        |

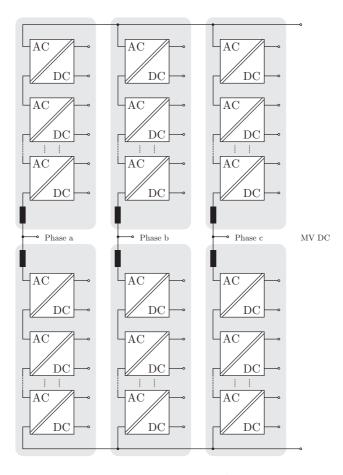

|          | 3.2  | Modu    | lar AC-DC topologies                        | 34        |

|          |      | 3.2.1   | Star connection                             | 34        |

|          |      | 3.2.2   | Double star connection                      | 42        |

|          |      | 3.2.3   | Delta connection                            | 47        |

|          | 3.3  | Topol   | ogy selection                               | 47        |

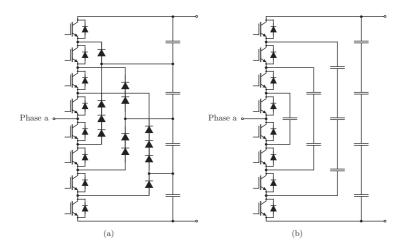

|          |      | 3.3.1   | Multilevel converters                       | 48        |

|          |      | 3.3.2   | Phase modularity and scalability            | 48        |

|          |      | 3.3.3   | Integration of galvanic isolation           | 49        |

|   |     | 3.3.4  | Single versus double star connection             | 49  |

|---|-----|--------|--------------------------------------------------|-----|

|   |     | 3.3.5  | Focus of this work                               | 53  |

| 4 | Cas | caded  | AC-DC Dual Active Bridge Converter               | 55  |

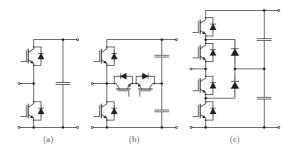

| • | 4.1 |        | rter topology                                    | 55  |

|   | 1.1 | 4.1.1  | From two-stage to single-stage module            | 58  |

|   |     | 4.1.2  | AC-DC dual active bridge module topologies       | 58  |

|   | 4.2 |        | ting principle                                   | 61  |

|   |     | 4.2.1  | Module level                                     | 61  |

|   |     | 4.2.2  | System level                                     | 63  |

|   | 4.3 |        | le modulation schemes                            | 64  |

|   | -   | 4.3.1  | ZCS/ZVS modulation with fixed switching fre-     | -   |

|   |     |        | quency                                           | 66  |

|   |     | 4.3.2  | ZVS modulation with variable switching frequency | 75  |

|   | 4.4 | Conve  | rter control                                     | 82  |

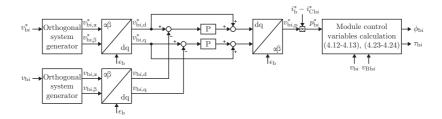

|   |     | 4.4.1  | Grid and phase PLLs                              | 84  |

|   |     | 4.4.2  | Grid current control                             | 84  |

|   |     | 4.4.3  | Phase SOC balancing                              | 84  |

|   |     | 4.4.4  | Battery SOC balancing                            | 86  |

|   |     | 4.4.5  | Module voltage control                           | 87  |

|   | 4.5 | Modul  | le design                                        | 88  |

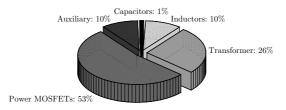

|   |     | 4.5.1  | Power components                                 | 89  |

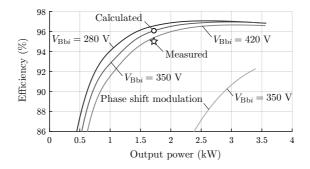

|   |     | 4.5.2  | Efficiency calculations                          | 92  |

|   |     | 4.5.3  | Hardware prototype                               | 94  |

|   |     | 4.5.4  | Experimental verification                        | 98  |

|   | 4.6 | System | n simulation                                     | 103 |

|   | 4.7 | Summ   | ary and conclusion                               | 107 |

| 5 | Cas | caded  | AC-DC Multi-Port Converter                       | 111 |

| 0 | 5.1 |        | uction to multi-port converters                  | 111 |

|   | 5.2 |        | rter topology                                    | 112 |

|   | 0.2 | 5.2.1  | Module topology                                  | 114 |

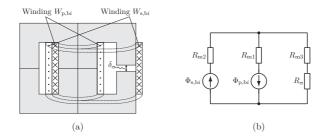

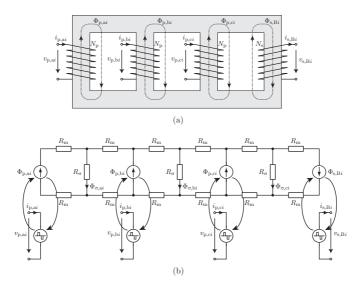

|   |     | 5.2.1  | Transformer arrangements                         | 116 |

|   | 5.3 | -      | ting principle                                   | 121 |

|   | 0.0 | 5.3.1  | Module level                                     | 121 |

|   |     | 5.3.2  | System level                                     | 123 |

|   | 5.4 |        | ing of power flows                               | 124 |

|   | 0.1 | 5.4.1  | Power flow between two ports                     | 125 |

|   |     | 5.4.2  | Power flow at AC ports                           | 128 |

|   | 5.5 |        | le modulation schemes                            | 129 |

|   | -   |        |                                                  | -   |

|              |     | 1                                                                                                                                                             | 30        |

|--------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

|              |     | 5.5.2 ZVS modulation $\ldots \ldots \ldots$   | 39        |

|              |     | 5.5.3 Alternative modulations $\ldots \ldots \ldots \ldots \ldots \ldots 14$                                                                                  | 48        |

|              | 5.6 | Module design 14                                                                                                                                              | 48        |

|              |     | 5.6.1 Power components $\ldots \ldots \ldots$ | 49        |

|              |     | 5.6.2 Efficiency calculations                                                                                                                                 | 54        |

|              | 5.7 | Module simulation                                                                                                                                             | 56        |

|              |     | 5.7.1 Fundamental phasor modulation 1                                                                                                                         | 56        |

|              |     |                                                                                                                                                               | 60        |

|              | 5.8 |                                                                                                                                                               | 64        |

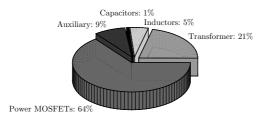

| 6            | Мu  | lti-Objective Optimization and Comparison 16                                                                                                                  | 37        |

| -            | 6.1 |                                                                                                                                                               | <u>39</u> |

|              | 6.2 | -                                                                                                                                                             | 73        |

|              | 0.2 |                                                                                                                                                               | 73        |

|              |     |                                                                                                                                                               | 75        |

|              |     | 1                                                                                                                                                             | . o<br>36 |

|              | 6.3 | 1                                                                                                                                                             | 36        |

|              | 0.0 | 1 1                                                                                                                                                           | 92        |

|              |     | 1                                                                                                                                                             | 94        |

|              | 6.4 | -                                                                                                                                                             | 94        |

|              | -   | 1                                                                                                                                                             | 95        |

|              |     | 0                                                                                                                                                             | 97        |

|              |     | 6.4.3 AC-DC H-bridge module with DC-DC dual active                                                                                                            |           |

|              |     | 0                                                                                                                                                             | 99        |

|              | 6.5 |                                                                                                                                                               | )5        |

|              | 6.6 | -                                                                                                                                                             | 07        |

| _            | a   |                                                                                                                                                               |           |

| 7            |     | nclusion and Outlook 20                                                                                                                                       |           |

|              | 7.1 | 2                                                                                                                                                             | )9        |

|              | 7.2 | Outlook                                                                                                                                                       | 15        |

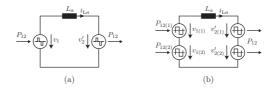

| $\mathbf{A}$ | DC  | -DC Dual Active Bridge Converter 21                                                                                                                           | .7        |

|              | A.1 | Converter topology                                                                                                                                            | 17        |

|              | A.2 | Modulation schemes                                                                                                                                            | 18        |

|              |     |                                                                                                                                                               | 18        |

|              |     | A.2.2 Trapezoidal current mode modulation 21                                                                                                                  | 19        |

|              |     | A.2.3 Triangular current mode modulation                                                                                                                      | 20        |

|              | A.3 | Converter optimization                                                                                                                                        | 22        |

|              |     | A.3.1 Design example                                                                                                                                          | 22        |

|    |       | A.3.2  | Optimization procedure  | <br>224 |

|----|-------|--------|-------------------------|---------|

|    |       | A.3.3  | Optimization results    | <br>226 |

| в  | Loss  | s Mod  | els of Power Components | 233     |

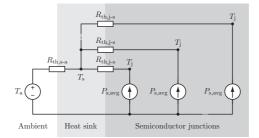

|    | B.1   | Semice | onductor devices        | <br>233 |

|    |       | B.1.1  | IGBT losses             | <br>233 |

|    |       | B.1.2  | MOSFET losses           | <br>235 |

|    |       | B.1.3  | Gate drive losses       | <br>236 |

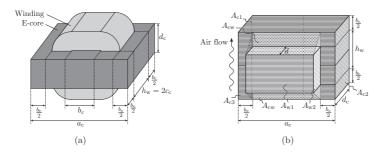

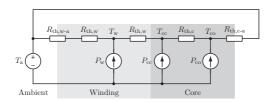

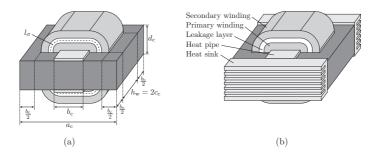

|    | B.2   | Induct | tive components         | <br>237 |

|    |       | B.2.1  | Winding losses          | <br>237 |

|    |       | B.2.2  | Core losses             | <br>242 |

|    | B.3   | Capac  | pitors                  | <br>243 |

| Bi | bliog | graphy |                         | 263     |

# Introduction

#### 1.1 Motivation

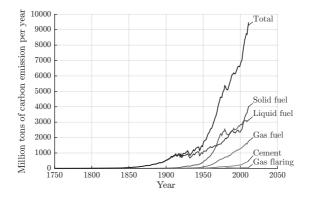

During the last decade the environmental impact of petroleum-based transportation infrastructure gained more and more significance. Fossil fuel powered vehicles lead to high emissions of  $CO_2$  and other greenhouse gases. The global emission of carbon per year is still growing drastically as depicted in **Fig. 1.1** from 1750 to 2011 with the liquid fuels exhibiting a significant part of over 3000 million tons a year [1].

Figure 1.1: Development of the global carbon emission per year given in million tons from 1750 to 2011 [1] originating from gas flaring, cement production as well as gas fuel, liquid fuel and solid fuel consumption.

In order to reduce the emissions of carbon and in general greenhouse gases to mitigate the induced ecological effects, the electric mobility plays an important role in our future transportation infrastructure together with the use of renewable energy sources like hydro power, solar energy or wind power. The electric mobility is becoming a real solution for a sustainable future in combination with the use of renewable energy sources.

Today's electric vehicles (EVs) already feature suitable (but limited) ranges and have advantages over vehicles driven by internal combustion engines as higher engine efficiency, regenerative braking and reduced noise emission. Moreover, EVs can serve as distributed energy storage integrated into the grid for vehicle to grid (V2G) applications in order to provide energy to the grid in times of shortages.

In Switzerland, the number of registered EVs is growing steadily from year to year [13]. **Tab. 1.1** gives a summary of EVs with 4-5 seats available on the market in early 2015 with their range as well as their

| Model                          | $\mathbf{Range}^{a}$ | Battery            | Battery              |

|--------------------------------|----------------------|--------------------|----------------------|

|                                |                      | capacity           | $\mathbf{voltage}^b$ |

| BMW i3                         | $190\mathrm{km}$     | $18.8\mathrm{kWh}$ | $360\mathrm{V}$      |

| Fiat 500e                      | $210\mathrm{km}$     | $24\mathrm{kWh}$   | $364\mathrm{V}$      |

| Ford Focus Electric            | $162\mathrm{km}$     | $23\mathrm{kWh}$   | $325\mathrm{V}$      |

| Kia Soul EV                    | $212\mathrm{km}$     | $27\mathrm{kWh}$   | $360\mathrm{V}$      |

| Mercedes-Benz B-Class Electric | $200\mathrm{km}$     | $28\mathrm{kWh}$   | 240 V                |

| Mitsubishi i-MiEV              | $150\mathrm{km}$     | $16\mathrm{kWh}$   | 330 V                |

| Nissan Leaf                    | $199\mathrm{km}$     | $24\mathrm{kWh}$   | $360\mathrm{V}$      |

| Renault Zoe                    | $210\mathrm{km}$     | $22\mathrm{kWh}$   | $400\mathrm{V}$      |

| Tesla Model S 70D              | $442\mathrm{km}$     | $70\mathrm{kWh}$   | $375\mathrm{V}$      |

| VW e-Golf                      | $190\mathrm{km}$     | $24.2\mathrm{kWh}$ | 323 V                |

Table 1.1: Electric vehicles with 4-5 seats available on the market (early 2015) with their range and battery specifications [2–11]. All of them are using the lithium-ion battery technology.

$^a{\rm The}$  range is given for the New European Driving Cycle (NEDC) set out in UN/ECE Regulation No. 83 for the Type~I~test~[12].

<sup>&</sup>lt;sup>b</sup>Nominal battery voltage.

battery capacity and voltage according to the manufacturers brochures. Most of the available EVs feature ranges of around 200 km given for the New European Driving Cycle (NEDC) which lead to battery capacities of more or less 24 kWh. All of the listed EVs are using the lithium-ion battery technology.

The charging methods for an EV range from a battery swap over inductive up to conductive charging as schematically depicted in **Fig. 1.2**. The battery swap seems to be the simplest solution, at least in theory. In practice it is not beneficial since the manufacturers apply different batteries with different specifications depending on the EV model.

**Figure 1.2:** State-of-the-art charging methods for an EV: (a) battery swap, (b) inductive charging, (c) conductive charging with AC or DC current.

The company Better Place founded 2007 in Israel proposed a battery swapping system where an EV driver does not own the battery. The customer is charged a monthly fee for the battery and the electricity based on the driven kilometers comparable to a mobile phone contract [14]. Despite the interest the company gained from various analysts and investors, the business model could not be realized for the EV mass market. The company shut down its business in 2013 [15].

Also Tesla Motors worked on a battery swapping station which allows to change the battery of the Model S in about 90 seconds [16]. The station became operational in January 2015 but is not reaching the popularity as the electric superchargers Tesla provides [17].

In contrast to the mechanical replacement of the EV battery for charging, electric energy can be transferred from a charging station to the EV battery either inductive or conductive. Inductive power transfer (IPT) systems feature a contactless energy transfer from a transmitting coil to a receiving coil based on the operating principle of a transformer. Limiting factors of such systems for EVs are often the required space of the receiver coil in the vehicle as well as the mechanical positioning of the coils in the charging station what strongly influences the transmission efficiency [18]. Moreover, inductive charging involves health risks from the induced electric fields in human tissue so that the magnetic stray field has to be limited.

Besides presented laboratory prototypes of IPT systems for the electric mobility in scientific literature [19,20], various companies are working on inductive charging stations for EVs as for instance Bombardier with their PRIMOVE systems [21], Siemens with their induction-based charging solution SIVETEC CIS [22] as well as many car manufacturers like Audi, BMW and Toyota [23].

The conventional and most popular way of charging an EV battery represents the conductive charging. The IEC 61851-1 standard defines the slow AC charging *mode 1* and *mode 2* from the low voltage (LV) distribution grid with a standard single- or three-phase power outlet with typical phase currents of 16 A and 32 A [24,25]. The AC charging *mode 3* covers slow and fast AC charging from a specific EV socket outlet at an AC charging station either at home or at public places [25]. The currents per phase are typically below 63 A [24]. Besides the AC charging modes the IEC 61851-1 standard defines also the fast DC charging *mode 4* with currents up to 400 A which is derived from the CHAdeMO standard [24–26].

DC fast charging stations and EVs supporting the CHAdeMO standard with a charging power of around 50 kW are already well established on the market. Over 50% of EVs sold in Europe from 2010 to 2014 are compliant with the CHAdeMO standard [27]. More than 50 different charger manufacturers as for instance ABB, Fuji Electric, Hitachi, Schneider or Siemens offer CHAdeMO DC charging stations as a part of their product portfolios for providing energy to EVs of different brands and models [27]. With the CHAdeMO charging system an EV battery can be almost fully charged in 15 to 30 minutes. Depending on the EV model the charging process takes 5 to 10 minutes for a 40 km to 60 km drive. Besides the CHAdeMO charging stations, Tesla Motors develops its own DC superchargers with a charging power up to 120 kW [28]. A 30 minutes charging operation of the Model S equates to a range of about 270 km.

With the available fast charging solutions, the range of fully electric cars is still limited compared to conventional fossil fuel powered cars. Today's classic mid-size diesel cars with seats for 4-5 adults exhibit an average tank capacity of 60 L that allows to travel distances of more

than 1000 km [29]. Compared to the EVs available on the market in early 2015 (see **Tab. 1.1**) the range of common diesel cars is about a factor 5 higher.

In order to increase the autonomy and the flexibility of EV drivers, the range limitations given through the long charging times can be mitigated by the development of so-called ultra-fast charging stations. Such stations would be able to charge an EV battery with charging rates up to  $5 \,\mathrm{kWh/min}$ , so that a charging time of 5 minutes equates to a range of about 200 km. These systems can be placed at key nodes in the road traffic network to provide electricity to the EV drivers faster than the conventional charging infrastructure. The required charging power for ultra-fast charging lies in the range of several 100 kW given by the target charging rate which is supplied by high power electronic converter systems preferably connected to the medium voltage (MV) grid.

State-of-the-art high power charging systems exist for electric buses as for example the eBus system from Siemens [30] with a charging power up to 450 kW which is connected to the LV or the MV grid. The offboard charging station consists of a structural mast for an inversely mounted pantograph where the bus is charged in 6 to 8 minutes depending on the state of charge (SOC) of the battery.

The TOSA 2013 bus project in Geneva with the power electronics from ABB applies stationary batteries at the bus stops which are charged with 50 kW power from the LV grid [31]. The batteries of the bus are then charged via a 400 kW high power charger during a 15 seconds discharge of the stationary energy storage. Additionally, at the terminal stop of the bus a charging power of 200 kW is available for a full recharge.

Moreover, Heliox from the Netherlands offers DC ultra-fast charging systems from 120 kW up to 2.5 MW for electric public transport systems running with 700 V [32]. The electric connection is made by a pantograph mounted on the roof of an electric bus.

Besides high power charging solutions for the public transport, the charging power available for the individual EV traffic is still limited. The most public charging stations feature no more than six charging ports with an output power below 150 kW as for example the worldwide supercharger network of Tesla [28], the solar powered Fastned charging network in the Netherlands [33] or the ChargePoint network in the United States [34]. For large-scale charging stations for instance at

highways where several EVs have to be charged simultaneously in a reasonable time, the required charging power reaches a few MW. For such systems the connection to the grid has to be done on the MV level since the currents drawn from the LV grid would become too high.

Research in the area of large-scale charging stations is mainly focusing on concepts applying a DC bus where several chargers, energy storage and renewable energy generation can be attached [35–38]. The proposed architecture in [35] consists of a bipolar DC bus which is coupled via an AC-DC converter and a step-down transformer to the MV grid. At the DC bus several fast charging DC-DC converters providing energy to the EVs as well as a battery energy storage system and renewable energy generation from wind and solar power are connected. Furthermore, in [36] a flywheel energy storage system as part of a fast charging station to mitigate the adverse effects of high power charging for the grid is investigated.

The use of energy storage in an ultra-fast charging station is not only useful to flatten the power demand from the grid during charging activities, moreover it is in general beneficial in the context of smart grid applications for the future energy distribution grid due to the increasing integration of renewable energy sources [39]. The inherently fluctuating and stochastic nature of renewable energy sources demands the placement of energy storage as part of the grid in order to ensure balancing supply and demand [40–42].

Besides the well-known energy storage systems using the potential energy of water (pumped hydroelectric storage systems [43]), in recent years additional concepts based on compressed air [43], flywheels [43, 44], thermal energy storage in molten salt [43, 45] as well as electrochemical storage in batteries [43, 44] have been investigated. The battery based systems offer the advantages of a high energy and power density, a high cycle efficiency as well as being location-independent and easily scalable [43]. Such systems also become more and more important in grid applications for load leveling providing fast frequency regulation [46]. In order to store considerable amounts of energy and ensure the dynamic control of power, suitable high power electronic equipment connecting the storage batteries to the grid plays an important role.

State-of-the-art battery energy storage systems at high power levels are usually connected to the MV grid. Because of the comparable high voltage level, multilevel converter systems are advantageous due to lower harmonics and reduced filtering effort, robust operation and reduced switching losses. Furthermore, no bulky transformers providing voltage adaptation are necessary.

Especially modular converter systems as the modular multilevel converter (MMC) [47] as well as the cascaded H-bridge converter (CHB) [48] offer the benefit to easily split and distribute the battery energy storage among several modules [49–51]. The storage battery is either attached directly to the module DC link [51] or connected via a (iso-lated) DC-DC converter [49].

Moreover, a modular converter system can be easily scaled according to the specified voltage and power levels. To decrease system downtime in case of a failure, a modular approach offers built-in redundancy which can be considered in the converter and control design process [52]. Additionally, by using standard components in each module manufacturing costs can be kept low.

The functionality of a split battery energy storage system connected to the MV grid can be further extended to an ultra-fast charging station based on the MMC or the CHB [53, 54]. For both converter systems bidirectional isolated DC-DC converters connecting the module DC link to the storage battery provide galvanic isolation and voltage adaptation. With the introduced isolation stage the insulation requirements of the battery packs are reduced and their negative rails can be grounded. Moreover, by applying non-isolated DC-DC converters with their outputs paralleled a high charging power for EVs becomes available. The grid-side introduced isolation stage guarantees further the compliance with EV charging standards (see Section 2.1.4).

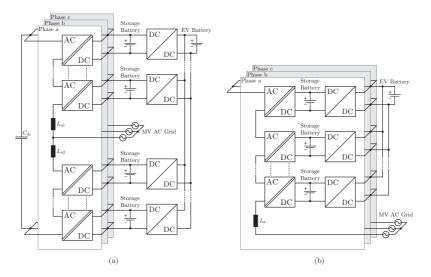

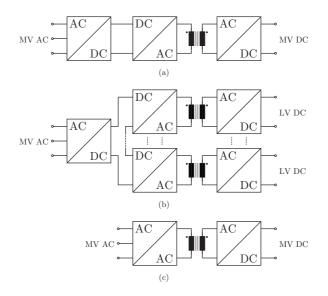

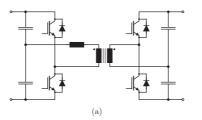

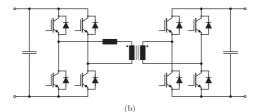

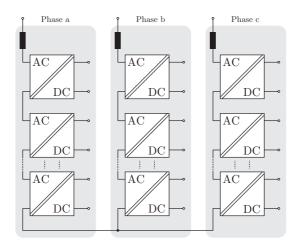

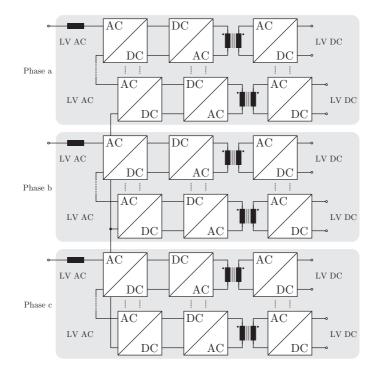

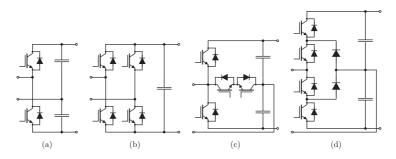

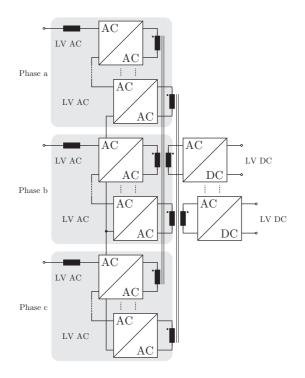

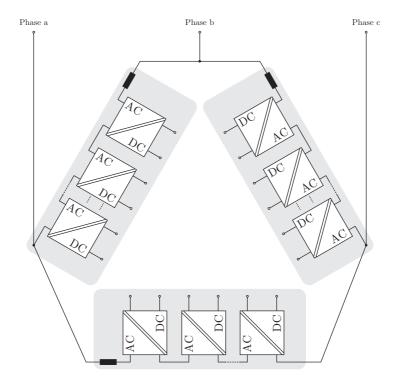

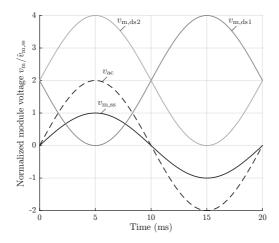

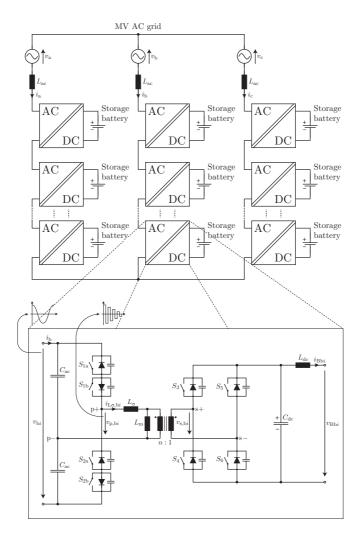

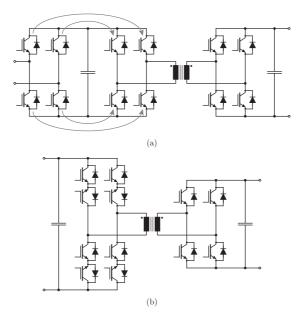

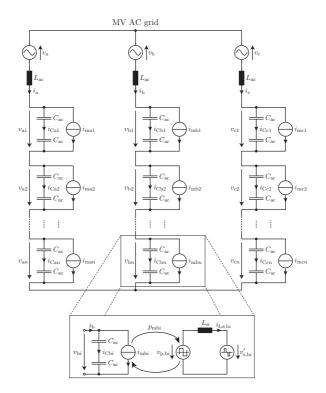

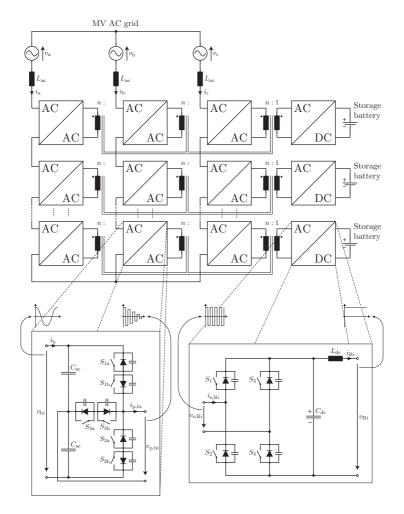

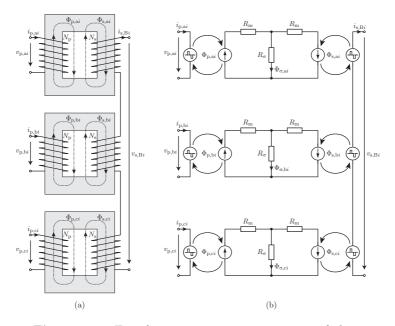

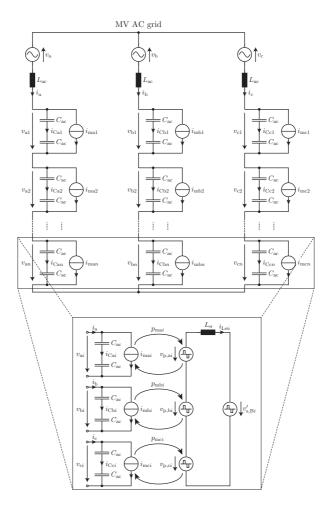

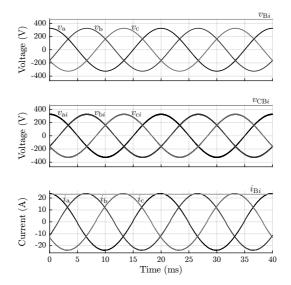

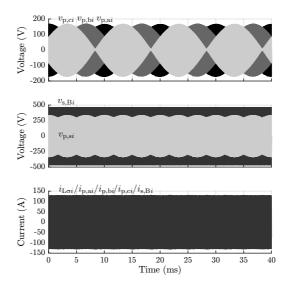

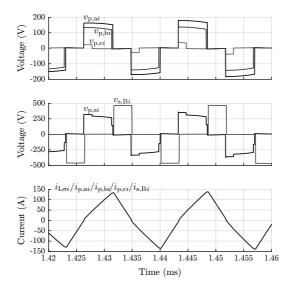

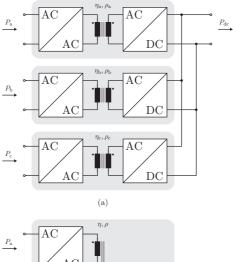

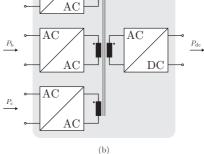

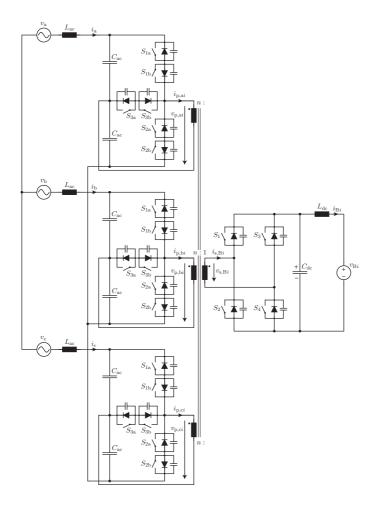

The split battery energy storage system as an integral part of an ultra-fast charging station for EVs offers considerable potential for this research work. Especially in the field of modular power electronic converter systems, the integration of module-level galvanic isolation opens possibilities for the investigation of single-stage isolated module topologies and the derived overall converter system. Fig. 1.3 depicts two possibilities of an ultra-fast charging station based on a split battery energy storage system with integrated galvanic isolation on module level. The outputs of the non-isolated DC-DC converters are paralleled, so that a high charging power for the EV battery becomes available.

Besides the evaluation on topology level, modulation and control schemes can be developed considering soft-switching conditions for the general applied semiconductor devices of IGBTs and MOSFETs. Furthermore, top-level control algorithms that ensure balancing the SOCs of the storage batteries in the context of the modular converter system can be studied.

Figure 1.3: Ultra-fast charging station based on a split battery energy storage system applying the modular multilevel converter (MMC) in (a) and the cascaded H-bridge converter (CHB) in (b). The required galvanic isolation between the grid and the EV battery (see Section 2.1.4) is realized on the grid-side module level. With non-isolated DC-DC converters connecting the storage batteries to the EV battery a high charging power for a short charging process becomes available.

#### 1.2 Objectives and contributions

The objective of this thesis is to develop, analyze and identify realization concepts and converter topologies for an ultra-fast charging station for electric vehicles with an integrated split battery energy storage system connected to a MV AC grid. The focus lies on the development and the electric as well as magnetic modeling of grid-connected modular converter systems with integrated galvanic isolation on the module level. For the promising module topologies new modulation schemes utilizing soft-switching are developed, analyzed, optimized and verified with a hardware prototype and/or in simulation. The main contributions of this thesis are given in the following.

# New concept of a three-phase cascaded AC-DC (two-port) dual active bridge converter which is modular on the phase level

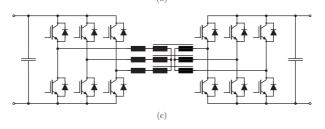

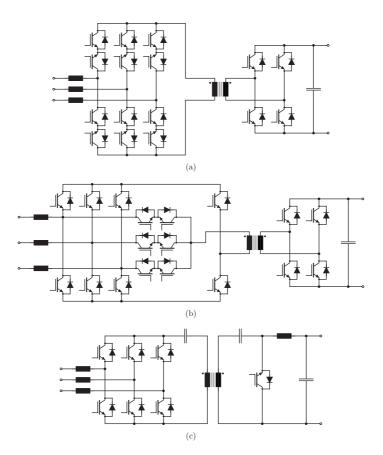

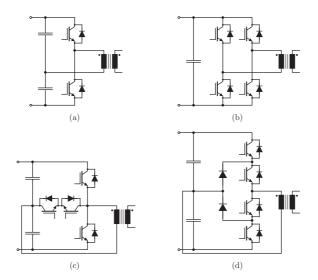

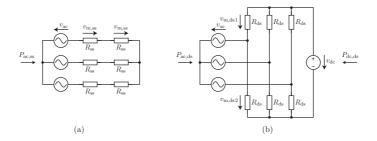

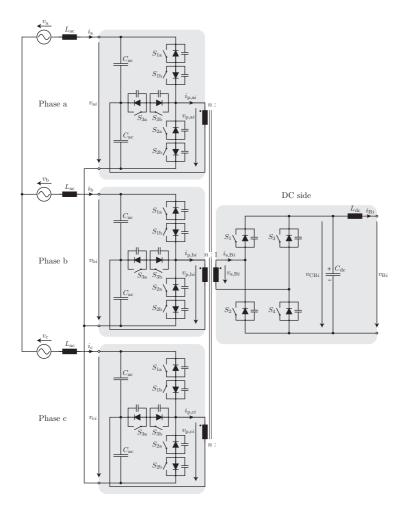

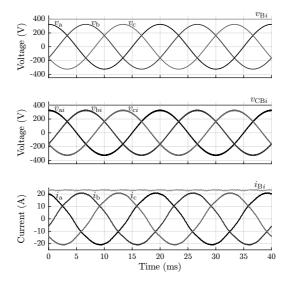

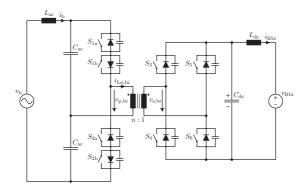

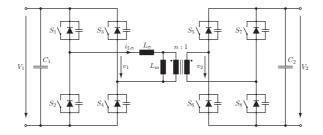

- ▶ Based on the state-of-the-art cascaded H-bridge converter and the well-known DC-DC/AC-DC dual active bridge converter, a *new phase-modular concept of a cascaded AC-DC dual active bridge converter* for a split battery energy storage system is developed (Chapter 4, Section 4.1, **Fig. 4.1**), modeled and its operating principle analyzed (Chapter 4, Section 4.2) and validated in simulation (Chapter 4, Section 4.6).

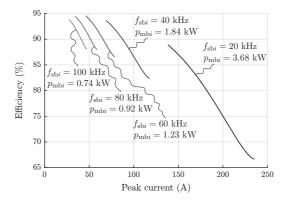

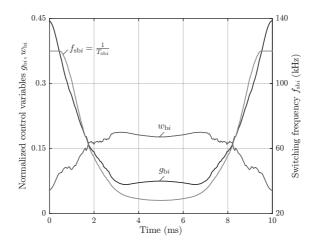

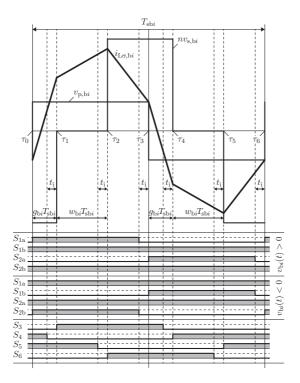

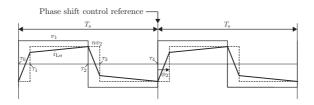

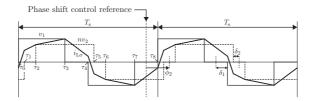

- ▶ For the proposed concept, a single-phase AC-DC dual active bridge converter as module is investigated. A *modulation scheme* that allows soft-switching for all semiconductor devices over the full AC mains period considering also the variation of the switching frequency is developed and optimized (Chapter 4, Section 4.3.2).

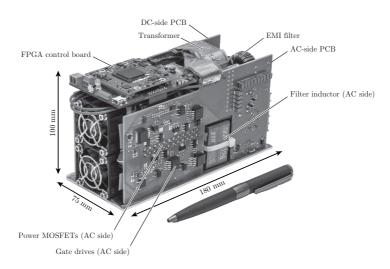

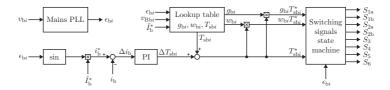

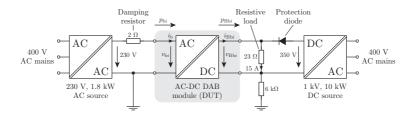

- ▶ For the module, a hardware prototype of a single-phase AC-DC dual active bridge converter is designed and implemented for the experimental verification of the proposed modulation scheme with variable switching frequency (Chapter 4, Section 4.5).

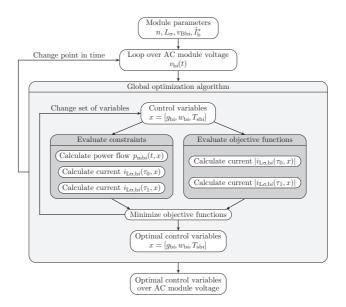

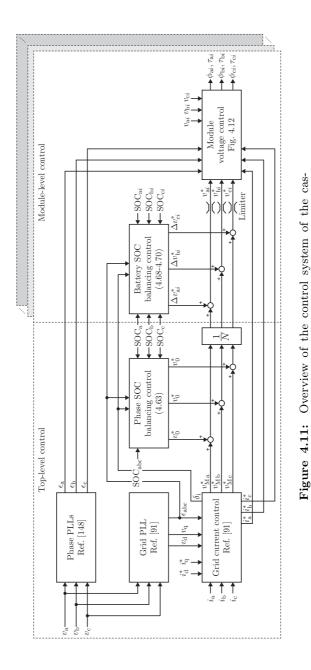

- ▶ Finally for the proposed concept, the *converter control structure* of a split battery energy storage system is investigated. For controlling the grid currents and the state of charges of the batteries the control structure is designed (Chapter 4, Section 4.4) as well as implemented and validated in simulation (Chapter 4, Section 4.6).

# New concept of a three-phase cascaded AC-DC multi-port converter which is modular on the phase level

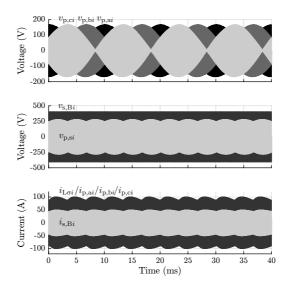

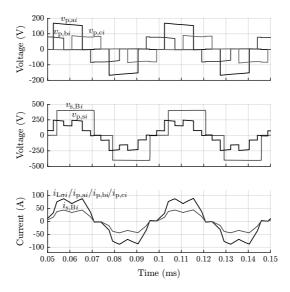

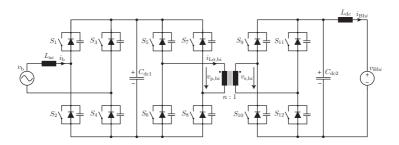

▶ Based on the state-of-the-art cascaded H-bridge converter and known DC-DC multi-port converters (typically three-port systems), a *new phase-modular concept of a cascaded AC-DC multiport converter* for a split battery energy storage system is developed (Chapter 5, Section 5.2, **Fig. 5.1**), modeled and its op-

erating principle analyzed (Chapter 5, Section 5.3) as well as a converter module simulated (Chapter 5, Section 5.7).

- ▶ A new generalized modeling approach of the power flows in a multi-port converter with an arbitrary number of ports connected in series (e.g. dual active bridge converter) is developed (Chapter 5, Section 5.4). The modeling approach leads to analytical power flow equations including all possible modulation schemes.

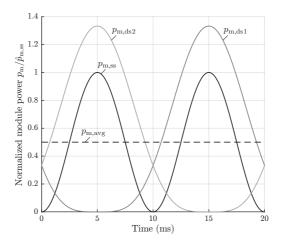

- ▶ For the proposed concept, a three-phase AC-DC multi-port converter module is investigated and *new modulation schemes* are developed, analyzed, modeled and optimized: Firstly based on a fundamental wave approach (Chapter 5, Section 5.5.1) and secondly considering soft-switching conditions for all semiconductor devices over the full AC mains period (Chapter 5, Section 5.5.2). The proposed modulation schemes are validated in simulation (Chapter 5, Section 5.7).

# Multi-objective optimization and comparison of the converter modules for the proposed concepts

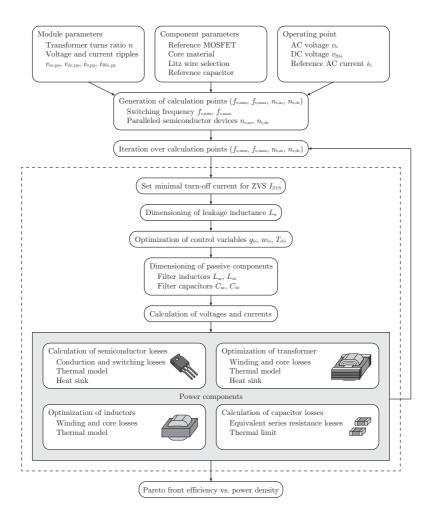

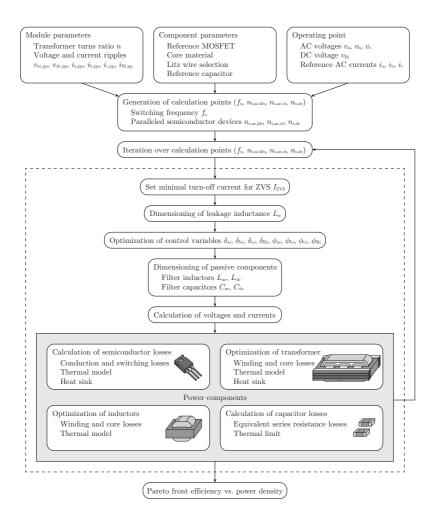

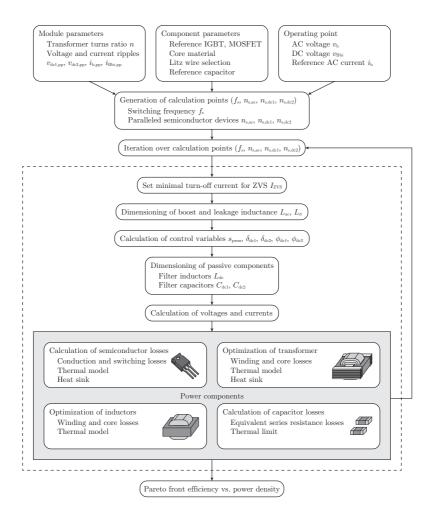

- ▶ A multi-objective optimization of the proposed converter systems on the module level (Chapter 6, Section 6.1) applying state-ofthe-art power component models in the electric, magnetic and thermal domain (Chapter 6, Section 6.2) is implemented. Finally, the converter modules are compared and discussed concerning efficiency and power density (Chapter 6, Section 6.4, Section 6.5).

- ▶ Additionally, a general optimization of the modulation scheme for a DC-DC dual active bridge converter design example applying the new modeling approach of the power flows (Chapter 5, Section 5.4) is carried out (Appendix A, Section A.3). Besides the clamping intervals and the phase shift, also the variation of the switching frequency is considered for the control.

#### 1.3 Outline of the thesis

The thesis covers all valuable achievements of the investigations of medium voltage converter systems for an ultra-fast charging station for electric vehicles combined with a split battery energy storage system.

**Chapter 1** starts with a motivation for the topic of the electric mobility and presents the state-of-the-art charging methods as well as today's available charging infrastructure. For an ultra-fast charging station for electric vehicles, state-of-the-art research approaches with integrated energy storage are summarized.

**Chapter 2** presents the design aspects for an ultra-fast charging station for electric vehicles from which concepts for the realization are developed and the specifications and requirements for the converter system and the energy storage can be stated.

**Chapter 3** evaluates state-of-the-art medium voltage bidirectional isolated AC-DC converter topologies suitable for the grid interface of an ultra-fast charging station for electric vehicles with the focus on the integration of a battery energy storage system as well as the integration of the galvanic isolation on module level.

**Chapter 4** proposes a new cascaded AC-DC dual active bridge converter for a split battery energy storage system. For the topology, suitable modulation and control schemes both on module as well as on system level are developed. A hardware prototype of a module is designed and built to experimentally verify the proposed modulation schemes. The overall battery energy storage system is simulated to validate the given theoretical analysis.

**Chapter 5** introduces a new cascaded AC-DC multi-port converter for a split battery energy storage system. For a three-phase AC-DC multi-port converter module, a new modeling approach for the power flows at the AC and the DC ports is presented and suitable modulation schemes are developed. The converter module is simulated to validate the given theoretical analysis.

**Chapter 6** presents a multi-objective optimization and comparison of the proposed converter systems on module level in terms of efficiency and power density. Besides the applied models of the power components the optimization procedure for each converter module is shown. Finally, the obtained optimization results are discussed and the proposed converter modules compared to the conventional two-stage AC-DC H-bridge module connected to a DC-DC dual active bridge converter.

**Chapter 7** summarizes and concludes the main achievements of the thesis and presents an outlook on possible future research work.

**Appendix A** recapitulates state-of-the-art modulation schemes for DC-DC dual active bridge converters and presents a general optimization of a DC-DC dual active bridge converter design example based on the new modeling approach for the power flows. Besides the clamping intervals and the phase shift also the variation of the switching frequency for control is considered in the optimization.

**Appendix B** covers the loss models of the power components used for the calculations throughout the thesis including semiconductor losses for IGBTs and MOSFETs, inductor and transformer losses in terms of skin effect, proximity effect and core losses as well as capacitor losses.

#### 1.4 List of publications

Different parts of this thesis including texts, tables, figures and equations have been previously published in scientific publications in international journals and conference proceedings. The publications are listed in the following.

#### Conference papers

- F. Jauch, J. Biela, Bidirectional Isolated ZVS DC-DC Converter with Nonpulsating Input & Output Current, 11th Brazilian Power Electronic Conference (COBEP), Natal, Brazil, September 11-15, 2011.

- F. Jauch, J. Biela, An Innovative Bidirectional Isolated Multi-Port Converter with Multi-Phase AC Ports and DC Ports, 5th EPE Joint Wind Energy and T&D Chapters Seminar, Aalborg, Denmark, June 28-29, 2012.

- 3. F. Jauch, J. Biela, Single-Phase Single-Stage Bidirectional Isolated ZVS AC-DC Converter with PFC, 15th International Power

Electronics and Motion Control Conference and Exposition (EPE-PEMC), Novi Sad, Serbia, September 4-6, 2012.

- F. Jauch, J. Biela, Modelling and ZVS Control of an Isolated Three-Phase Bidirectional AC-DC Converter, 15th European Conference on Power Electronics and Applications, Lille, France, September 3-5, 2013.

- F. Jauch, J. Biela, Generalized Modeling and Optimization of a Bidirectional Dual Active Bridge DC-DC Converter including Frequency Variation, International Power Electronics Conference (ECCE Asia), Hiroshima, Japan, May 18-21, 2014.

- F. Jauch, J. Biela, Novel Isolated Cascaded Half-Bridge Converter for Battery Energy Storage Systems, 16th European Conference on Power Electronics and Applications, Lappeenranta, Finland, August 26-28, 2014.

- D. Christen, F. Jauch, J. Biela, Ultra-Fast Charging Station for Electric Vehicles with integrated split Grid Storage, 17th European Conference on Power Electronics and Applications, Geneva, Switzerland, September 8-10, 2015.

#### Journal papers

- F. Jauch, J. Biela, Generalized Modeling and Optimization of a Bidirectional Dual Active Bridge DC-DC Converter Including Frequency Variation, IEEJ Journal of Industry Applications, vol. 4, no. 5, pp. 593-601, 2015

- F. Jauch, J. Biela, Combined Phase Shift and Frequency Modulation of a Dual Active Bridge AC-DC Converter with PFC, IEEE Transactions on Power Electronics, accepted for publication

#### Patents

1. F. Jauch, J. Biela, Konverterschaltung und Verfahren zum Ansteuern einer Konverterschaltung, CH 706 337 A2, April 2, 2012.

# Ultra-Fast Charging Station for Medium Voltage Grids

2

In the design process of an ultra-fast charging station for the medium voltage grid, the requirements and the specifications according to the intended application area have to be evaluated first. Main factors like the amount of electric vehicles (EVs) to be charged during a specific time, the average energy content of an EV battery and the desired charging time per energy unit play an important role. Based on these aspects, concepts for the realization of an ultra-fast charging station can be developed.

#### 2.1 Design aspects

When designing an ultra-fast charging station several aspects have to be taken into account including

- ▶ the amount of EVs to be charged during a specific time,

- ▶ the average energy content of an EV battery,

- ▶ the desired/required charging time per energy unit,

- ▶ meeting the EV battery galvanic isolation standards [55, 56].

The first three aspects define the required charging power the station has to deliver to the EV whereas the fourth one guarantees compliance with standards for safety reasons. In the following, two scenarios of an ultra-fast charging station are discussed - a large charging station near Table 2.1: Ultra-fast charging station scenarios for a large charging station near highways and a small charging station in urban regions. It is assumed that the battery capacity for EVs charging at a highway station is higher because of long distance drives compared to EVs charging in urban regions.

| Parameter                                      | Large station                  | Small station    |  |

|------------------------------------------------|--------------------------------|------------------|--|

|                                                | near highways                  | in urban regions |  |

| EVs per day                                    | 200                            | 50               |  |

| EVs charging in parallel                       | 6                              | 1                |  |

| Typical battery capacity                       | $48\mathrm{kWh}$               | 24 kWh           |  |

| Charging rate                                  | $9.6\mathrm{kWh}/\mathrm{min}$ | 4.8 kWh/min      |  |

| Charging power per $EV^a$                      | $576\mathrm{kW}$               | 288 kW           |  |

| Total charging power <sup><math>b</math></sup> | $3.46\mathrm{MW}$              | 288 kW           |  |

<sup>a</sup>Effective charging power not covering losses.

<sup>b</sup>Total effective charging power not covering losses.

highways and a small charging station in urban regions. The scenarios are summarized in **Tab. 2.1**.

#### 2.1.1 Utilization

In [57,58] Monte Carlo simulations of different utilization scenarios of an ultra-fast charging station are performed. The utilizations range from 50 EVs per day up to 200 EVs per day which are based on typical traffic density distributions in Switzerland. In this work, the utilization of a small charging station is assumed to be 50 EVs per day whereas for the large charging station 200 EVs per day are considered.

#### 2.1.2 EV battery capacity

The typical battery energy content of a medium-sized EV is assumed to be 24 kWh which is exactly the median of the listed EVs in **Tab. 1.1** available on the market in early 2015. This battery capacity allows driving around 200 km. Due to the limited range, such EVs are especially used in urban regions. Travelling long distances require higher ranges and therefore an increased battery capacity. With the Tesla Model S 70D listed in **Tab. 1.1** ranges over 400 km are possible. Nevertheless, it is currently the only available EV with such a high range and a relatively large battery capacity of 70 kWh. For the large charging station, it is assumed that the typical battery capacity is around 48 kWh since near highways especially EVs driving long distances are charged. The average consumption of these EVs is considered to be 12 kWh/100 km for the New European Driving Cycle (NEDC) [12].

#### 2.1.3 Charging time

In the European 400 V AC low voltage distribution grid<sup>1</sup>, currents at home or at workplaces are often limited to 16 A per phase/socket. For instance with a  $3.3 \,\mathrm{kW}$  single-phase charger<sup>2</sup> the charging process for a typical medium-sized EV takes up to 8 h for a full battery recharge [26]. With a three-phase connection the available charging power is increased to 10 kW so that the charging time can be reduced by a factor of 3. Nevertheless, it stays in the range of a few hours.

Considering such long charging times, especially for long distance drives, the EV loses its practical application. Drivers have to fundamentally change their habits and adapt to the restricted mobility what is rather difficult to achieve. For this reason, fast charging modes are established to cut down charging times, so that drivers feel comfortable when they can recharge whenever they like.

The CHAdeMO standard defines DC fast charging with voltages up to 500 V and currents up to 120 A [26] which is covered by the *charging mode* 4 according to the IEC 61851-1 standard [25]. Furthermore, in the IEC 61851-1 standard AC fast charging from the 400 V low voltage grid is covered with phase currents of 32 A and 63 A respectively [24–26]. Increasing the charging power to 50 kW according to the CHAdeMO standard [27], EV batteries can be recharged in 20 min to 30 min depending on their capacities. Many manufacturers of EVs and charging stations deliver their products compliant with the CHAdeMO standard. In spring 2015, already 8'000 CHAdeMO charging stations are placed all over the world [27].

The focus of this work is on DC ultra-fast charging which means to cut down charging times to 5 min for a typical EV battery with 24 kWh [57]. This leads to a charging rate of 4.8 kWh/min which requires a charging power of 288 kW for a lossless charging process. This is the

<sup>&</sup>lt;sup>1</sup>230 V phase voltage and 400 V phase-to-phase voltage.

<sup>&</sup>lt;sup>2</sup>Power electronic converter with an efficiency of 90 %.

scenario considered for a small charging station. For large charging stations near highways a 5 min charging process for an EV battery with double the capacity is assumed. The required effective charging power is then given by  $576 \,\mathrm{kW}$ .

#### 2.1.4 Galvanic isolation

The galvanic isolation requirement for EV chargers between the AC distribution grid and the EV battery is commonly related to safety issues [55]. In [56] case studies investigate the outcome of a human touching the AC line while he/she is connected to the EV chassis ground. Simulations show that for non-isolated chargers a person gets shocked while for isolated chargers with no connection from the neutral to the ground this is not the case.

In case of DC chargers with a direct coupling to the EV battery, the IEC 61851-23 standard states the isolation requirements between the AC distribution grid and the EV battery [30, 59]. The output side of the DC charging system has to be designed as an unearthed DC power supply (IT system) with insulation monitoring.

For ultra-fast charging stations with an integrated energy storage and comparable low grid power connection [60] it is more beneficial to integrate the galvanic isolation in the low power frontend converter connected to the grid than in the high power charging converter itself from the efficiency point of view.

#### 2.1.5 Summary and discussion

For a charging station the required charging power is mainly determined by the EV battery capacity and the charging rate. Especially for DC ultra-fast charging the charging power is relatively high compared to a DC fast charging station compliant with the CHAdeMO standard. Furthermore, with increasing charging currents the resistive losses caused by internal battery cell resistances as well as contact resistances grow. The faster the charging process, not only the more effective charging power is required, but also the power to cover the losses is increased.

Considering a battery pack with an internal resistance  $r_{\text{bat}}$  and an open-circuit voltage  $v_{\text{bat}}$  (mainly dependent on the state of charge (SOC)), the required charging power delivered from the power electronic system is given by

$$P_{\rm ch} = \frac{1}{t_{\rm ch}} \int_0^{t_{\rm ch}} v_{\rm bat}(t) i_{\rm ch}(t) + i_{\rm ch}(t)^2 r_{\rm bat}(t) \, \mathrm{d}t \tag{2.1}$$

where  $t_{\rm ch}$  represents the charging time.  $v_{\rm bat}$  and  $r_{\rm bat}$  depend on the non-linear characteristic of the battery pack and vary according to the applied charge pattern. With conversion efficiencies  $\eta_{\rm g}$  of an AC-DC grid interface and  $\eta_{\rm ch}$  of a connected DC-DC charger the grid power input is

$$P_{\rm g} = \frac{P_{\rm ch}}{\eta_{\rm g}\eta_{\rm ch}}.$$

(2.2)

Using a three-phase connection to the 400 V low voltage distribution grid would lead to phase currents in excess of 400 A for ultra-fast charging of one EV which results in an overload of the copper cables [61]. A reasonable approach for an ultra-fast charging station in public areas should therefore focus on medium voltage grid connections so that also several EVs in parallel could be charged. Furthermore, buffering of energy should be considered, especially for times when the grid power is limited or energy from distributed generation has to be stored. Hence, the integration of energy storage can lead to a reduction of the rated power of the station. The energy for the charging process is then partly or fully drawn from an intermediate energy storage.

Addressing the battery technology, ultra-fast charging requires comparable high power densities of the battery cells. Optimizations of lithium-ion cells in [62] show that with an increased power density the energy density of the cell rapidly drops. In general it is a trade-off between power density and energy density when designing a lithium-ion cell. The faster a cell can be charged, the lower its energy density is. For an EV suitable for ultra-fast charging, this means also a drastic increase in weight.

#### 2.2 Concepts for realization

In the following, two concepts for the realization of an ultra-fast charging station for the medium voltage AC grid are given. First, a solution based on a medium voltage DC bus which suits large charging stations for instance near highways is presented. Secondly, an integrated charging solution based on a battery storage system connected directly to the medium voltage AC grid is introduced. This solution is mainly intended to be used in urban regions with a low amount of charging slots. Both concepts basically exhibit an AC-DC grid interface and one or more energy transfer units for charging the EV batteries.

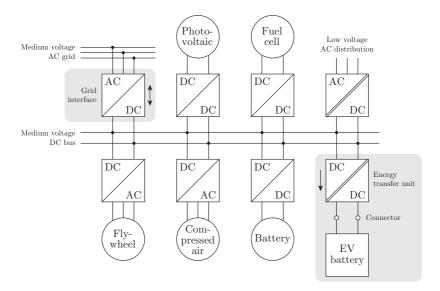

Figure 2.1: Ultra-fast charging station concept with a medium voltage DC bus suitable for large electric charging stations near highways. The station consists mainly of a non-isolated AC-DC grid interface to couple the DC bus to the medium voltage AC grid and an isolated DC-DC energy transfer unit for charging the EV battery. Additionally, energy storage can be attached to the DC bus such as flywheels, compressed air storage or battery storage systems. The station could also provide energy to EVs from own generation such as photovoltaic panels or fuel cells.

#### 2.2.1 Medium voltage DC bus

A concept of an ultra-fast charging station with a medium voltage DC bus is depicted in **Fig. 2.1**. The DC bus allows the connection of energy storage like flywheels, compressed air storage, battery storage systems, ultra-capacitors and so on. Furthermore, the station can include own

generation for instance from renewables like solar or wind power. The various storage medias and generation units are directly coupled to the DC bus by non-isolated AC-DC or DC-DC converters respectively. The DC bus could also be seen as a DC grid around big cities with a large amount of distributed generation and interfaces to an AC or even a DC low voltage distribution grid.

Besides generation and storage units, a non-isolated AC-DC grid interface couples the station to the medium voltage AC grid. The DC-DC energy transfer unit serves as a high power charging converter where also the galvanic isolation from the DC bus is integrated. The AC-DC grid interface is capable of bidirectional power flow whereas the DC-DC energy transfer unit only delivers power to the EV battery. For vehicle to grid applications, one could also think of a bidirectional energy transfer unit.

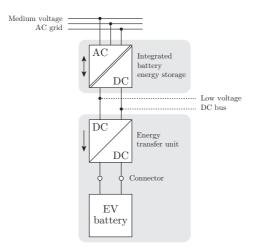

Figure 2.2: Ultra-fast charging station concept with an integrated battery energy storage suitable for urban electric charging stations. The station consists of an isolated AC-DC grid interface where storage batteries are included. The non-isolated DC-DC energy transfer unit connects the AC-DC converter to the EV battery for charging operation.

#### 2.2.2 Integrated battery energy storage

In Fig. 2.2 a concept of an ultra-fast charging station with integrated battery energy storage suitable for urban regions is shown. The AC-DC grid interface integrates the galvanic isolation from the medium voltage AC grid as well as storage batteries to provide sufficient energy for the charging process in times with low grid power available.

The grid interface basically combines the purposes of charging EVs and storing energy from the grid. Especially with the increasing generation from renewables, energy storage systems become an important part of the electricity infrastructure in order to maintain the stable operation of the grid in the long run.

The DC-DC energy transfer unit connects the grid interface to the EV battery and is non-isolated as the isolation stage is already included in the grid interface. The converter provides unidirectional power flow as long as no vehicle to grid applications are needed. An additional low voltage DC bus is available where the voltage fluctuates with the SOC of the storage batteries. This could be used for instance for powering auxiliaries like the charging control.

#### 2.2.3 Focus of this work

Due to range limitations and relatively long charging times of EVs compared to fossil fuel powered cars, the large-scale application of EVs is still developing very slowly. Nevertheless, in urban regions where driving distances are short and EVs exhibit long parking times at home or at work the electric mobility gains interest. In and around big cities more and more charging infrastructure will be established in the next few years. Besides slow and fast charging of EVs, also the demand for ultra-fast charging will increase.

Therefore, this work focuses on an ultra-fast charging station with an integrated battery energy storage system as shown in **Fig. 2.2** for the application in urban regions. For the AC-DC grid interface, power electronic converter topologies and modulation schemes are developed, optimized and evaluated concerning achievable efficiency and power density. The main goal is the integration of the galvanic isolation into state-of-the-art converter topologies in order to reduce the number of conversion stages. The DC-DC energy transfer unit is not covered in this work. A possible approach is described in [60] where an ultra-fast charging station for the low voltage distribution grid is presented.

# 2.3 Specifications and requirements

For an ultra-fast charging station with an integrated battery energy storage system (see **Fig. 2.2**), detailed specifications and requirements are derived in the following. These are relevant for selecting and developing suitable power electronic converter systems in this work. In **Tab. 2.2** the AC-DC grid interface parameters are summarized.

First of all, the voltage level of the AC medium voltage grid and the rated power of the AC-DC converter are specified. According to IEC 60038 voltage standards [63] a nominal system voltage of 6.6 kV is considered. Due to the integrated battery energy storage in the AC-DC grid interface the nominal power can be lower than the charging power listed in **Tab. 2.1**. In this work, the nominal grid power is fixed to 150 kW and the energy storage sized depending on the charging power as shown in the following.

# 2.3.1 Charging power

In order to size the energy storage, the total charging power considering the losses in the EV battery pack has to be determined. Assuming a constant open-circuit battery pack voltage  $V_{\rm bat}$ , a constant internal resistance  $R_{\rm bat}$  and a constant DC current  $I_{\rm ch}$  during the ultra-fast

Table 2.2: Specifications and requirements for the AC-DC grid interface with an integrated battery energy storage system used in an ultra-fast charging station in urban regions (see Fig. 2.2).

|                 | Parameter                | Value               |

|-----------------|--------------------------|---------------------|

| AC-DC converter | AC grid voltage          | $6.6\mathrm{kV}$    |

|                 | Nominal output power     | $150\mathrm{kW}$    |

|                 | Galvanic isolation       | Required            |

|                 | Bidirectional power flow | Required            |

| Battery storage | Storage capacity         | 1 MWh               |

|                 | Battery technology       | Lithium-ion         |

|                 | Battery voltage          | $< 1000 \mathrm{V}$ |

**Table 2.3:** Parameters for an ultra-fast charging process of a typical EV battery pack built with lithium-ion polymer cells. The data corresponds to the Nissan Leaf battery pack which includes cells from AESC [64,65].

| Open-circuit voltage     | $V_{\rm bat}$     | $360 V^a$               |

|--------------------------|-------------------|-------------------------|

| Internal resistance      | $R_{\rm bat}$     | $125\mathrm{m}\Omega^b$ |

| Charging current         | $I_{\rm ch}$      | 800 A                   |

| Effective charging power | $P_{\rm ch,eff}$  | $288\mathrm{kW}$        |

| Charging losses          | $P_{\rm ch,loss}$ | 80 kW                   |

| Charging power           | $P_{\rm ch}$      | $368\mathrm{kW}$        |

| Charging efficiency      | $\eta_{ m ch}$    | 78%                     |

<sup>a</sup>The nominal cell voltage of the AESC lithium-ion polymer cell is 3.75 V [65].

<sup>b</sup>The internal battery pack resistance is approximated by the measurements given in [64]. The number of cells in series is  $N_{\text{cell},s} = 96$  and the number of strings in parallel  $N_{\text{cell},p} = 2$  [64].

charging process, (2.1) simplifies to

$$P_{\rm ch} = V_{\rm bat} I_{\rm ch} + I_{\rm ch}^2 R_{\rm bat} = P_{\rm ch,eff} + P_{\rm ch,loss}.$$

(2.3)

The required charging power consists of an effective part  $P_{\rm ch, eff}$  to deliver energy to the battery cells as well as a resistive part  $P_{\rm ch, loss}$  that covers the losses. The internal resistance  $R_{\rm bat}$  of the battery pack depends on the number of cells connected in series  $N_{\rm cell,s}$ , the strings connected in parallel  $N_{\rm cell,p}$  and the cell resistance  $R_{\rm cell}$  given by the manufacturer and is written as

$$R_{\rm bat} = \frac{N_{\rm cell,s} R_{\rm cell}}{N_{\rm cell,p}}.$$

(2.4)

Given the effective charging power  $P_{\rm ch,eff} = 288 \,\rm kW$  from **Tab. 2.1** and an average battery voltage  $V_{\rm bat} = 360 \,\rm V$ , the DC charging current is calculated to be  $I_{\rm ch} = 800 \,\rm A$ . With the internal battery pack resistance  $R_{\rm bat} = 125 \,\rm m\Omega$  of the Nissan Leaf [64], the required charging power yields  $P_{\rm ch} = 368 \,\rm kW$  which leads to a charging efficiency of  $\eta_{\rm ch} = 78 \,\%$ . The results are summarized in **Tab. 2.3**.

#### 2.3.2 Energy storage

The charging power  $P_{\rm ch}$  given in (2.3) can be divided into two parts: The power  $P_{\rm g}$  delivered from the grid and the power  $P_{\rm s}$  from the battery energy storage (energy  $E_{\rm s}$  delivered during  $t_{\rm ch}$ ). This leads to

$$P_{\rm ch} = \eta_{\rm ch} \left( \eta_{\rm g} P_{\rm g} + P_{\rm s} \right) = \eta_{\rm ch} \left( \eta_{\rm g} P_{\rm g} + \frac{E_{\rm s}}{t_{\rm ch}} \right) \tag{2.5}$$

with  $\eta_{\rm ch}$  being the efficiency of the DC-DC energy transfer unit and  $\eta_{\rm g}$  the efficiency of the AC-DC grid interface. Assuming a fixed grid power  $P_{\rm g}$  and  $N_{\rm ev}$  EVs to be charged per day from the grid and the energy storage, the required energy buffer can be determined as

$$E_{\rm bess} = N_{\rm ev} E_{\rm s} = N_{\rm ev} \left( \frac{P_{\rm ch} t_{\rm ch}}{\eta_{\rm ch}} - \eta_{\rm g} P_{\rm g} t_{\rm ch} \right).$$

(2.6)

With this calculation the buffer will be empty after 24 h without recharging operation between the EV charging processes. The time available for recharging the energy buffer is

$$T_{\rm bess} = 24\,\mathrm{h} - N_{\rm ev}t_{\rm ch} \tag{2.7}$$

from which the recharging constraint

$$E_{\rm bess} \le \eta_{\rm g} P_{\rm g} T_{\rm bess} = \eta_{\rm g} P_{\rm g} \left( 24 \,\mathrm{h} - N_{\rm ev} t_{\rm ch} \right) \tag{2.8}$$

arises that guarantees the buffer to be recharged during a day. The maximum number of EVs that can be charged a day is reached at the equality of the recharging constraint. There,  $T_{\rm bess}$  gets minimal so that the recharging operation exactly covers the energy which is consumed by the EVs charged during a day.

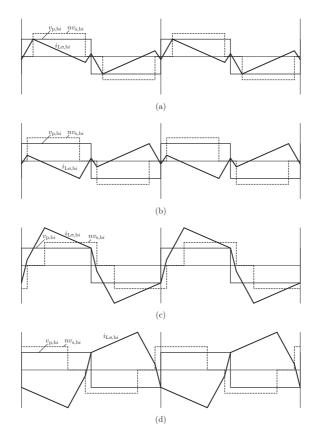

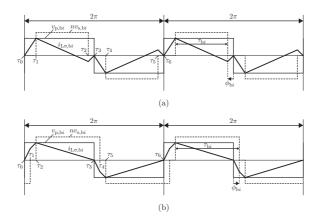

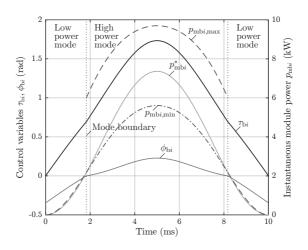

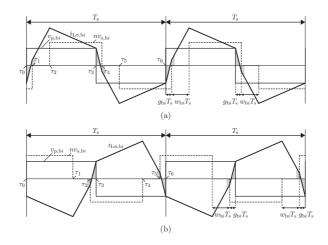

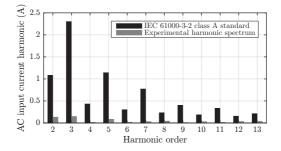

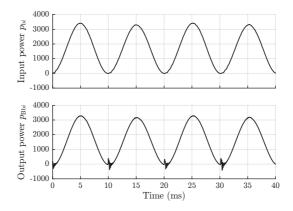

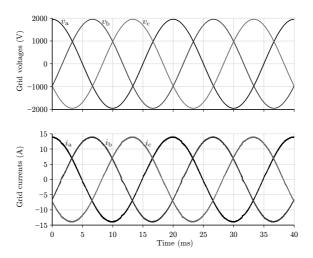

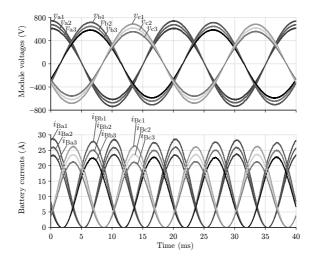

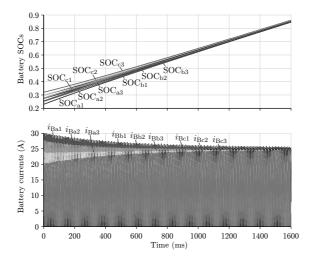

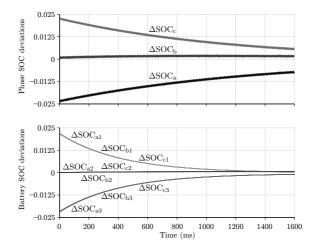

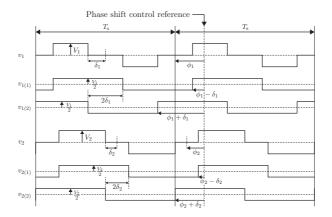

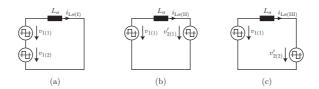

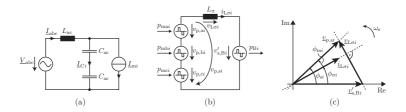

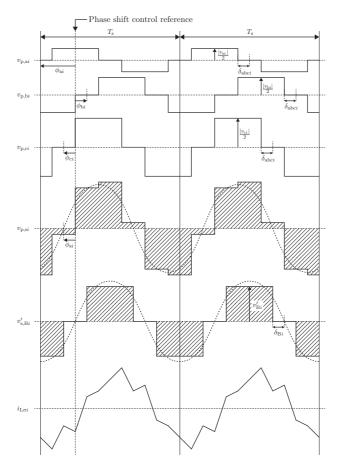

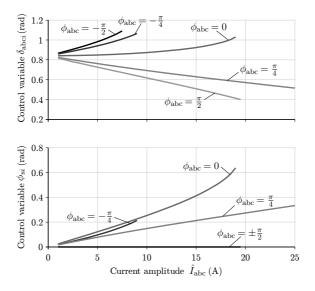

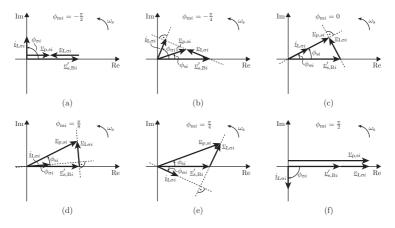

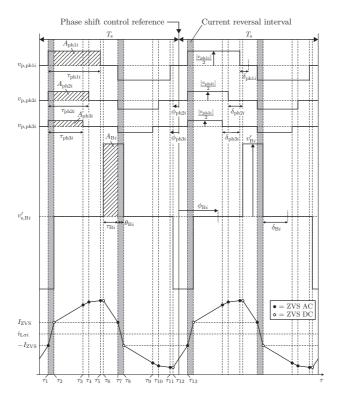

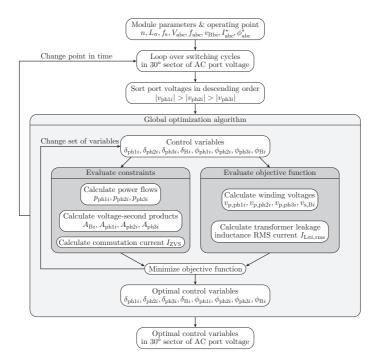

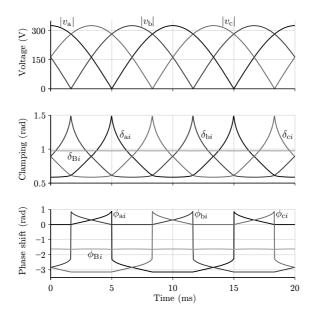

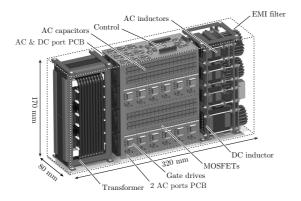

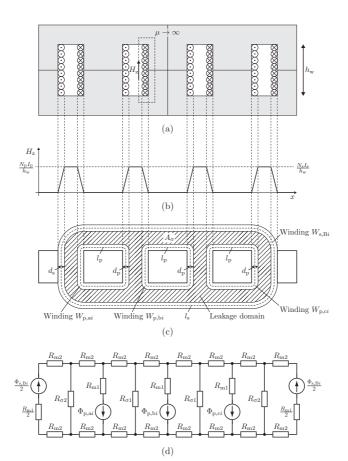

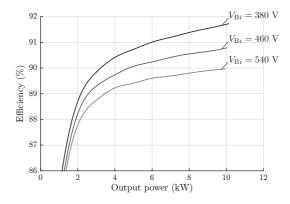

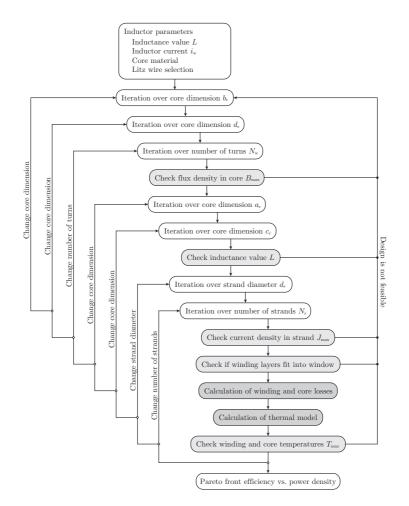

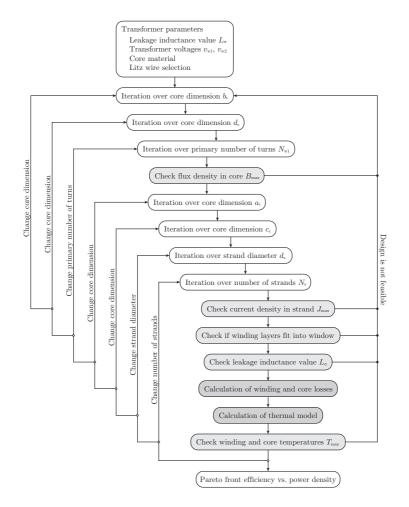

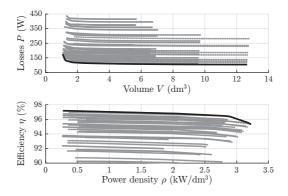

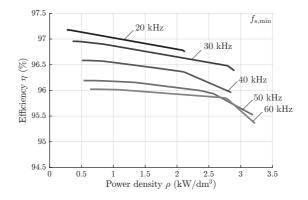

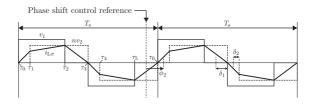

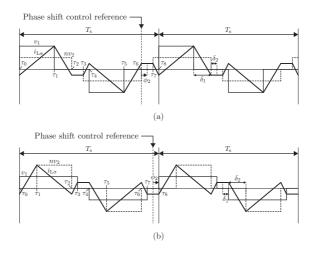

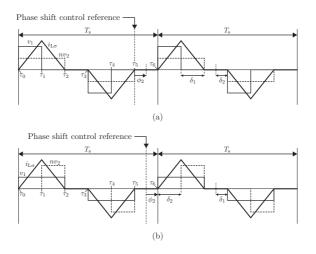

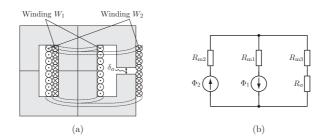

The numerical evaluation of (2.6) for the grid power  $P_{\rm g} = 150 \,\rm kW$ , the charging power  $P_{\rm ch} = 368 \,\rm kW$ , converter efficiencies  $\eta_{\rm g} = \eta_{\rm ch} = 95 \,\%$ , a charging time of  $t_{\rm ch} = 5 \,\rm min$  and  $N_{\rm ev} = 50$  leads to the required energy storage  $E_{\rm bess} = 1 \,\rm MWh$ .