# Blackboxing Performance Monitoring Units

**Master Thesis**

Author(s):

Lin, Denny

**Publication date:**

2016

Permanent link:

https://doi.org/10.3929/ethz-a-010725643

Rights / license:

In Copyright - Non-Commercial Use Permitted

# Master's Thesis No. 152

Systems Group, Department of Computer Science, ETH Zurich

# **Blackboxing Performance Monitoring Units**

by Denny Lin

Supervised by Prof. Timothy Roscoe Gerd Zellweger

March 2016-September 2016

# **Abstract**

Due to the complexity of modern hardware, computer programs often cause complicated interactions when scheduled together. Users therefore frequently turn to specialized tools such as Performance Monitoring Units (PMUs) for diagnosing system issues. However, PMUs themselves are complex, so they require domain knowledge and a good understanding of the underlying hardware to use. Such obstacles prevent PMUs from seeing more widespread use.

In this thesis, a survey of PMUs investigates the various intricacies involved in selecting performance events and configuring performance counters. Major problems include the limited number of performance counters relative to the number of measurable performance events, abstruse definitions of performance events, and the processor-specific nature of PMUs.

Numerous grouping techniques which associate similar objects are explored with a view of reducing the event space. We also experiment with classification algorithms to automatically detect interference and remove the need for human interpretation of events and counter measurements. Moreover, proposals in this thesis are designed with portability, i.e., the applicability of methods to different machines, in mind.

All in all, we show the complexity of PMUs is a manageable problem and select procedures can be automated, which opens up the possibility of abstracting away PMU details from users.

# **Contents**

| Ał | Abstract                 |                                        |    |  |  |  |  |

|----|--------------------------|----------------------------------------|----|--|--|--|--|

| 1  | Intr                     | oduction                               | 1  |  |  |  |  |

|    | 1.1                      | Motivation                             | 1  |  |  |  |  |

|    | 1.2                      | Objectives                             | 3  |  |  |  |  |

|    | 1.3                      | Outline                                | 3  |  |  |  |  |

| 2  | Background 4             |                                        |    |  |  |  |  |

| _  | 2.1                      | Preliminaries                          | 4  |  |  |  |  |

|    |                          | 2.1.1 Performance Monitoring Units     | 4  |  |  |  |  |

|    |                          | 2.1.2 Tools                            | 6  |  |  |  |  |

|    | 2.2                      | Related Work                           | 7  |  |  |  |  |

|    | ۷.۷                      | 2.2.1 Performance Applications of PMUs | 7  |  |  |  |  |

|    |                          | 2.2.2 Other Applications of PMUs       | 8  |  |  |  |  |

|    | 2.3                      | Discussion                             | 9  |  |  |  |  |

|    | 2.0                      | Discussion                             |    |  |  |  |  |

| 3  | Sur                      | vey of PMUs                            | 10 |  |  |  |  |

|    | 3.1                      | Vendor Documentation                   | 10 |  |  |  |  |

|    | 3.2                      | Tools                                  | 11 |  |  |  |  |

|    |                          | 3.2.1 perf_event                       | 11 |  |  |  |  |

|    |                          | 3.2.2 libpfm                           | 13 |  |  |  |  |

|    |                          | 3.2.3 PAPI                             | 14 |  |  |  |  |

|    | 3.3                      | 3 Portability                          |    |  |  |  |  |

|    | 3.4                      | 4 Performance Overhead                 |    |  |  |  |  |

|    | 3.5                      | Case Study: Scheduling                 | 15 |  |  |  |  |

|    |                          | 3.5.1 Preliminaries                    | 16 |  |  |  |  |

|    |                          | 3.5.2 Results                          | 16 |  |  |  |  |

|    | 3.6                      | Case Study: Interference               | 19 |  |  |  |  |

|    |                          | 3.6.1 Cache Interference               | 19 |  |  |  |  |

|    |                          | 3.6.2 Memory Interference              | 20 |  |  |  |  |

|    | 3.7                      | Discussion                             | 22 |  |  |  |  |

| 4  | Event Space Reduction 24 |                                        |    |  |  |  |  |

| -  | 4.1                      | Preliminaries                          | 24 |  |  |  |  |

|    | ***                      | 4.1.1 Applications                     | 24 |  |  |  |  |

|    |                          | 4.1.2 Ranchmarks                       | 25 |  |  |  |  |

|   |      | 4.1.3   | Event Selection and Measurement                    | 26 |

|---|------|---------|----------------------------------------------------|----|

|   |      | 4.1.4   | Data Representation                                | 26 |

|   | 4.2  | Dime    | nsionality Analysis                                | 27 |

|   |      | 4.2.1   | Subspace Dimensionality and Approximation Error    | 28 |

|   |      | 4.2.2   | Projection of Data Points onto Subspaces           | 28 |

|   | 4.3  | Event   | Similarity                                         | 30 |

|   |      | 4.3.1   | Euclidean Distance                                 | 31 |

|   |      | 4.3.2   | Correlation Coefficient                            | 31 |

|   | 4.4  | Event   | Correlation                                        | 32 |

|   |      | 4.4.1   | Graph Representation                               | 33 |

|   | 4.5  | Event   | Grouping                                           | 34 |

|   |      | 4.5.1   | Connected Components                               | 34 |

|   |      | 4.5.2   | Minimum Clique Cover                               | 35 |

|   |      | 4.5.3   | Greedy Maximum Clique Cover                        | 36 |

|   |      | 4.5.4   | <i>k</i> -means Clustering with Euclidean Distance | 38 |

|   |      | 4.5.5   | <i>k</i> -means Clustering with Correlation        | 39 |

|   | 4.6  | Comp    | parison of Grouping Methods                        | 41 |

|   |      | 4.6.1   | Validity and Effectiveness                         | 41 |

|   |      | 4.6.2   | Inference of Similar Events                        | 42 |

|   |      | 4.6.3   | Summary                                            | 43 |

|   | 4.7  | Discu   | ssion                                              | 44 |

| 5 | Into | rforonc | ee Detection                                       | 45 |

| 3 | 5.1  |         | e Detection                                        |    |

|   | 5.1  | 5.1.1   | Training and Classification                        |    |

|   |      | 5.1.2   | Classification of Interference                     |    |

|   | 5.2  |         | fication with Events                               | 47 |

|   | J.Z  | 5.2.1   | Training and Test Sets                             | 47 |

|   |      | 5.2.1   | Complete Event Set                                 |    |

|   |      | 5.2.3   | Correlated Event Set                               |    |

|   |      | 5.2.4   | Uncorrelated Event Set                             |    |

|   | 5.3  |         | fication with Groupings                            | 49 |

|   | 5.5  | 5.3.1   | Training and Test Sets                             | 50 |

|   |      | 5.3.2   | Group Leaders                                      | 50 |

|   |      | 5.3.3   | Connected Components                               | 51 |

|   |      | 5.3.4   | Minimum Clique Cover                               | 51 |

|   |      | 5.3.5   | Minimum Clique Cover Approximation                 | 52 |

|   |      | 5.3.6   | Greedy Maximum Clique Cover                        | 52 |

|   |      | 5.3.7   | <i>k</i> -means Clustering with Euclidean Distance | 52 |

|   |      | 5.3.8   | <i>k</i> -means Clustering with Correlation        | 52 |

|   | 5.4  |         | fication of Unknown Applications                   | 53 |

|   | J.1  | 5.4.1   | Training and Test Sets                             | 54 |

|   |      | 5.4.2   | Classification of Unknown Applications             | 54 |

|   | 5.5  |         | ssion                                              | 54 |

|   |      |         |                                                    |    |

| 6  | Future Work              | 56 |  |

|----|--------------------------|----|--|

| 7  | Conclusion               | 58 |  |

| A  | Benchmark Configurations | 59 |  |

| В  | Event Space              | 62 |  |

| Bi | Bibliography             |    |  |

# 1 Introduction

This thesis explores PMUs and presents an automated process for selecting performance events and assessing the validity of selected events in the context of interference detection. The proposed methods are intended to be applicable to any given machine.

#### 1.1 Motivation

There is no doubt computer systems have become increasingly complex in recent years. We have witnessed the advent of multicore processors, and multiprocessor machines are now commonplace. To complicate matters, the ever-widening gap between processor and memory speeds has resulted in intricate memory hierarchies.

Since one fundamental goal of users and programmers is to fully utilize available hardware resources, these changes have inevitably increased their burden, for the underlying hardware has become more difficult to understand. Nevertheless, this problem is manageable as vendor documentation is widely available, and there are tools such as hwloc [6] which provide information pertaining to processor topologies including cache levels and sizes and NUMA nodes.

Thus the real challenge is not understanding the hardware itself, but the interactions between applications running on top of the hardware. One contributing factor to this problem is the aforementioned intricacies of hardware; another is the complexity of modern workloads themselves. First, modern workloads consist of heterogeneous tasks. For instance, enterprises often run a mix of batch jobs and latency-sensitive applications in data centers. Second, the additional parallelism in multicore processors has given rise to the number of multithreaded programs. Needless to say, understanding the interactions caused by a mix of heterogeneous, parallel applications within a complex system is not a trivial task.

While there are various categories of interactions, each with its own characteristics, we are primarily concerned with interactions of a specific nature, namely, those that cause performance degradations. There are many shared resources within systems (e.g., CPU caches, processor interconnects, and memory buses), and these frequently become points of contention. Due to the power wall, CPU manufacturers are using extra transistors gained from Moore's law to introduce

1.1 Motivation 1 Introduction

more parallelism in the form of additional cores instead of increasing clock speeds. Parallel applications have therefore gained popularity, but this trend has aggravated resource contention.

How to mitigate resource contention to limit the impact on performance is now an important question. Although it is possible to monitor applications and observe the consequences of their interactions, devising a method which is applicable to all applications and scenarios is nontrivial. An alternative approach is to monitor components in hardware, and others have shown PMUs can be employed to avoid resource contention. However, the usage of PMUs presents a whole new set of challenges.

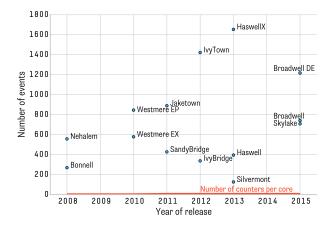

Figure 1.1: Number of counters and events of Intel microarchitectures.

Figure 1.1 shows the number of events and counters of Intel microarchitectures over time. The following observations can be made:

- 1. The number of available counters has remained relatively constant.

- 2. The number of countable events greatly exceeds the number of available counters.

- 3. Each microarchitecture supports different events.

The first observation necessitates the careful selection of events since we can only collect a handful of data points. However, there are typically hundreds of events, and users rarely possess the domain knowledge required to understand event definitions. As a result, the problem is not caused merely by the scarcity of counters, but also a consequence of the multitude of events. Furthermore, a good understanding of the underlying hardware is often essential for interpreting event counts, which raises the entry bar even higher. Another issue is performance events are processor-specific, which prevents the use of performance counters on a large scale.

In summary, we view PMUs as an invaluable tool, but significant hurdles must be cleared for them to become accessible to users. Specifically, the number of events which need to be measured must be small, but the selection of events is presently too cumbersome. In addition, portability is an unsolved problem despite 1.2 Objectives 1 Introduction

the development of various libraries. We aim to address these issues so that details of PMUs can be hidden from users.

# 1.2 Objectives

**Survey of PMUs:** Previous work has shown PMUs are invaluable tools with applications ranging from scheduling improvements to problem troubleshooting. However, they focus solely on the applications of PMUs and do not provide sufficient insight into PMUs themselves. Therefore, we begin by conducting a detailed survey of PMUs to uncover issues which hinder their adoption by users. This includes case studies of how PMUs are used in practice.

**Event Space Reduction:** It is important to note PMUs vary from processor to processor. Regardless, they all share one common trait: the number of measurable performance events greatly exceeds the number of available performance counters. As such, we apply grouping techniques which prune redundant events. This is to address the problem of having a limited number of counters.

**Interference Detection:** While PMUs have been shown to be useful in a number of contexts, we evaluate selected events based on their ability to detect interference. Event values are collected into samples which are supplied to a binary classifier. The accuracy of the classifier enables us to determine the effectiveness of the various grouping methods. This approach opens up the possibility of automatically selecting events for users.

**Portability:** Previous applications of PMUs are mostly machine-dependent. However, this must change if PMUs are to see more widespread use. Although the grouping methods and evaluation of event groupings in this thesis were applied on a specific machine, the process can be reproduced on another machine without any prior knowledge of performance events other than the list of supported events.

#### 1.3 Outline

The remainder of this thesis explores PMUs and presents a framework for automatically selecting and evaluating events. Chapter 2 contains a brief overview of PMUs and examines related work. Chapter 3 presents a survey of PMUs. Chapter 4 explores methods for grouping performance events. Chapter 5 applies a classification technique to detect interference with samples consisting of event counts. The results are used to evaluate the effectiveness of different event groupings. Chapter 6 discusses possible directions for future work. Chapter 7 concludes. Benchmark configurations are documented in Appendix A, and the list of events considered for selection can be found in Appendix B.

# 2 Background

This chapter is dedicated to the background information required to understand subsequent chapters. We begin by introducing Performance Monitoring Units. The purpose of this section is to provide insight to the centerpiece of this thesis. Next, a detailed study of related work is presented to understand the possible applications of Performance Monitoring Units.

## 2.1 Preliminaries

Here we give an overview of Performance Monitoring Units and introduce associated terminology. Although Performance Monitoring Units are processor-specific, we primarily focus on abstract concepts applicable to all processors in this section. Related tools are also mentioned as they will be relevant in later chapters.

## 2.1.1 Performance Monitoring Units

A **Performance Monitoring Unit (PMU)** is a component present in virtually all modern processors. As the name suggests, PMUs can be used to obtain performance measurements within computers. Each PMU contains two main components:

- Performance events

- Performance counters

#### **Performance Events**

A performance event is a hardware event within the processor which can be measured by the PMU. Examples of events include the number of clock cycles, instructions executed, and last-level cache misses. Some events have **subevents** which allow fine-grained control. For instance, cache misses may be classified as data reads, data writes, instruction fetches, and hardware prefetches. Depending on the PMU, it may or may not be possible to select multiple subevents when measuring an event. Moreover, there are three categories of events: **core events**, **off-core events**, and **uncore events**. Core events are measured within cores whereas uncore events are measured outside of cores. Offcore events are in the middle,

2.1 Preliminaries 2 Background

and they often measure requests sent to processor components outside of cores. In this thesis, we consider offcore events to be a special type of core events.

Since PMUs are processor-specific, the supported events vary from processor to processor. Different vendors provide completely distinct events. The difference between microarchitectures from the same vendor is not as pronounced, but there are still minor variations. Generally, each PMU supports several hundred events.

#### **Performance Counters**

A performance counter is a special-purpose register which is capable of measuring a single event.<sup>1</sup> For example, we could have two counters which measure the number of cache misses and references and then derive the cache miss rate. Counter values are always integers. Each core has its own set of counters. Moreover, there are two types of counters: fixed counters and general-purpose counters. Fixed counters can only measure specific events while general-purpose registers are capable of measuring any supported event (with a few exceptions).

It is important to note the number of counters is PMU-dependent, and not all PMUs have fixed counters. Generally, each core has less than a dozen counters. If simultaneous multithreading (SMT) is enabled, general-purpose counters in a core are normally evenly divided among SMT threads whereas each SMT thread has its own set of fixed counters.

#### Instrumentation

Despite the processor-dependent nature of PMUs, the instrumentation is more or less the same for all machines. The following information is therefore applicable to all CPUs. Every event is represented by an event code, and subevents are selected by applying unit masks (umasks). Counters are managed through a set of **model specific registers** (MSRs). Typically, each general-purpose counter is associated with two MSRs:

- Event select MSR: This register controls the counter.

- Event counter MSR: This register stores the count of the selected event.

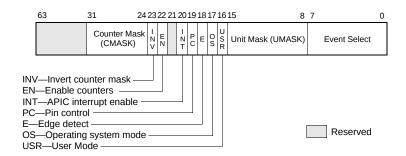

The bits of the event select MSR are used to configure the corresponding event counter MSR:<sup>2</sup>

- Counters are enabled or disabled by toggling a bit.

- Events are selected using event codes and umasks.

- Counters can be restricted to count only when the core is executing in kernel mode or user mode.

On x86 processors, the WRMSR instruction is used to write to event select MSRs while RDMSR is used to read event counter MSRs. Some vendors have special

<sup>&</sup>lt;sup>1</sup>Since the use of a performance counter implies the measurement of an event, we will use the terms PMU and performance counters interchangeably.

<sup>&</sup>lt;sup>2</sup>While event select MSRs provide additional functionality, the details have been omitted for brevity.

2.1 Preliminaries 2 Background

instructions for accessing PMU MSRs (e.g., counters can be read with RDPMC on Intel CPUs).

There may be additional restrictions on events and counters, e.g., some events can only be measured with specific counters. As the rules are PMU-specific, it is not possible to present a generalization here.

Instrumentation of fixed counters is essentially the same as general-purpose ones, except event select MSRs are replaced by fixed counter control MSRs, which lack the capability to select events.

#### **2.1.2** Tools

Given that instrumenting counters by reading and writing to MSRs is rather cumbersome, a number of tools have appeared which facilitate the use of PMUs by providing high-level abstractions. These include operating system support and user libraries with advanced features. In addition, vendors have also created tools for performance analysis which utilize PMUs.

#### **Operating System Support**

Linux has supported PMUs with perf\_event through the perf\_event\_open system call (syscall) since version 2.6.3.1 [41].<sup>3</sup> Each measured event is represented as a file descriptor, and it is possible to group events. There are various options such as only monitoring specific processes or cores. It is also possible to periodically sample counters and write the values into a ring buffer. Furthermore, the syscall provides "generic" events for portability across different machines although this requires events to be hardcoded for each supported microarchitecture. Other events are accessible by supplying event codes and umasks. Control of counters is performed through ioctl calls.

On FreeBSD, pmc provides an interface to performance counters through the hwpmc kernel module [25, 26]. FreeBSD has event name aliases which are similar to generic events on Linux. Both counting and sampling events are also possible.

#### **User Libraries**

Two common libraries with PMU are support are libpfm [20] and PAPI [7, 23]. The former mainly aids users in the selection of events while the latter is a more comprehensive suite with extra functionality.

The libpfm library is normally coupled with perf\_event. Instead of requiring users to pass in "raw" event codes and umasks to access events not in the limited set of predefined generic events, libpfm supplies a list of events compiled from vendor documentation. Hence most events have a self-evident name which simplifies event selection for users. Support for each new microarchitecture must still be added to libpfm, but end users need not be concerned with this process.

On the other hand, PAPI is more akin to an all-in-one package. The library was designed as a cross-platform interface, and users configure and access counters

<sup>&</sup>lt;sup>3</sup>It was originally named perf\_counter\_open

2.2 Related Work 2 Background

through its API. It provides generic events under the name "standard events" and supports microarchitecture-specific events as "native events." Unlike perf\_event and libpfm, it possesses the capacity to multiplex counters. Moreover, PAPI has low-level and high-level APIs. The latter only includes basic functionality.

#### **Vendor Tools**

CPU vendors have released PMU tools such as Intel PCM (Performance Counter Monitor) [12] and Intel VTune Amplifier [13]. Although Intel PCM's support is limited to Intel CPUs, it is capable of producing detailed performance metrics for various CPU components. Furthermore, Intel PCM has good support for multiple microarchitectures, and its source code is available online under the 3-clause BSD license.

#### 2.2 Related Work

Previous work has demonstrated that PMUs have numerous applications ranging from performance modeling to power efficiency. It is possible to divide the use cases into those which improve performance of programs online and other applications (here performance refers to either throughput or latency). Both categories are discussed in detail although we are mainly concerned with the former.

# 2.2.1 Performance Applications of PMUs

#### **Resource Contention**

One way of dealing with resource contention in multicore systems is contentionaware scheduling. Another method is to employ cache partitioning to avoid interference. In both cases, previous work has shown good heuristics can be obtained from performance counter measurements.

Azimi et al. reduced cache contention and cache thrashing with cache partitioning [2]. Both objectives were achieved by using the cache miss rate as a heuristic. For the former, it helped determine the cache partition sizes, and in the latter, it provided an estimate of the *reuse distance* so that cache lines which "polluted" the cache by evicting useful cache lines were restricted to a special partition.

Knauerhase et al. made scheduling improvements by employing the number of cache misses per cycle as a heuristic [24]. In a nutshell, the scheduler distributed tasks evenly among caches using the heuristic to reduce interference. Zhuravlev et al. evaluated a similar scheduling policy, but used the cache miss rate as the heuristic instead [45]. A scheme was also devised to quantify factors causing performance degradation, and they concluded that factors such as memory controller contention and hardware prefetching were more dominant than cache contention. However, they noted the cache miss rate is highly correlated with the number of memory controller and prefetch requests, which explains its effectiveness as a heuristic.

2.2 Related Work 2 Background

Saini et al. assessed the performance benefits of enabling SMT by quantifying processor resource utilization using PMU measurements [39]. They concluded SMT is generally beneficial, but contention in the memory hierarchy can reduce its advantages.

## **Application Latency**

Coscheduling batch jobs and latency-sensitive applications is desirable to maximize resource utilization, but this must not come at the cost of increased latency. While interference is a consequence of resource contention, we need not be concerned with the root cause in contrast to the previous use case. In other words, the contended resource is not important so long as the latency is kept under control.

Zhang et al. collected the cycles-per-instruction (CPI) metric from applications and used historical data to detect anomalies [44]. They identified "antagonists" which caused interference and throttled them. Lo et al. applied resource utilization to determine whether batch jobs and latency-sensitive applications can be scheduled together, for interference occurs when shared resources are saturated [28]. They relied on performance counters to calculate memory bandwidth usage for their resource utilization estimations.

## 2.2.2 Other Applications of PMUs

# **Compiler Optimizations**

Techniques such as profile-guided optimization (PGO) attempt to find an optimal combination of compiler flags, and they have been applied to real-world programs such as Mozilla Firefox [34]. Cavazos et al. proposed an alternative approach using performance counters [8].

## **Debugging and Troubleshooting**

Bare et al. made measurements of a small set of events and used support vector machines (SVMs), a machine learning technique, to detect anomalies in an e-commerce system [3]. In addition, Bhatia et al. developed a tool which collects system information including counter measurements [5]. The data can then be used for debugging by finding irregularities.

#### Performance Modeling

Ofenbeck et al. showed performance counter measurements can be used for the roofline model [43] when analyzing application performance by counting the number of FLOPS, memory operations, and clock cycles with performance events on Intel processors [38].

#### **Power Consumption**

Singh et al. estimated power consumption of a computer system with data gathered from performance counters [40]. Merkel et al. took the concept a step fur-

2.3 Discussion 2 Background

ther and developed a power-aware scheduler in addition to estimating power consumption [32].

#### 2.3 Discussion

We can formulate a number of conclusions from the examination of PMUs and related work. This includes not only benefits but also limitations of performance counters.

First, there is no question concerning the usefulness of PMUs. In particular, counter measurements are good indicators of performance [2, 24, 45, 46]. Determining the root cause of interference is relevant in cases where scheduling is employed to avoid resource contention. However, it is not necessary when providing latency guarantees for programs [28, 44]. Moreover, the storage of historical data aids the detection of performance degradation [44].

Second, applications in previous work target a specific processor, which demonstrates a drawback in terms of portability—moving to a new machine would require reselecting the performance events. In cases where the same events exist on the new platform, one must still verify the validity of the events. The presented PMU tools are aware of this limitation, and in response attempt to support a limited set of generic events across all platforms [7]. This is one step to solving the problem even though it is not a complete solution.

Third, most studies make the assumption contention occurs either in caches or the memory bus and measure corresponding performance events such as the number of cache misses or memory accesses. Yet there is no proof such events are the best indicators; it is plausible there are other more suitable candidates.

Fourth, the number of performance counters limits the data obtainable by users. Recent Intel and AMD processors have 11 and 4 counters per core, respectively. In contrast, there are hundreds of measurable events. PAPI supports multiplexing of events, and there are proposals exploring different approaches. Azimi et al. utilized statistical sampling to multiplex counters to get values within 15% of non-multiplexed counts [1]. A similar study was undertaken by May [31]. Consequently, multiplexing is a valid solution, but we will investigate other alternatives which do not rely on statistical sampling to reduce the probability of error.

# 3 Survey of PMUs

In this chapter, we present a survey of PMUs and discuss their limitations in detail. Topics include the portability of performance events and the scarcity of performance counters. In contrast to the previous chapter, we mention architecture-specific details of PMUs. Case studies of PMUs are also conducted to understand typical workflows of users.

#### 3.1 Vendor Documentation

Priority is given to the x86 architecture, so we only consider Intel and AMD processors in this thesis. Documentation of PMUs for Intel microarchitectures is located in the Intel 64 and IA-32 Architectures Software Developer's Manual (SDM) Volume 3 [11]. Each microarchitecture has its own section with a list of supported performance events. To illustrate, Figure 3.1 contains a truncated list of events for the Ivy Bridge microarchitecture obtained from the SDM. Each event has an event code, umasks for subevents, and a description. Certain events have additional restrictions or notes. Note that high-end CPU models often support extra events compared to basic models within the same microarchitecture.

| Event<br>Num. | Umask<br>Value | Event Mask Mnemonic     | Description                                                                                                                              | Comment |

|---------------|----------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 03H           | 02H            | LD_BLOCKS.STORE_FORWARD | Loads blocked by overlapping with store buffer that cannot be forwarded.                                                                 |         |

| 03H           | 08H            | LD_BLOCKS.NO_SR         | The number of times that split load operations are temporarily blocked because all resources for handling the split accesses are in use. |         |

| 05H           | 01H            | MISALIGN_MEM_REF.LOADS  | Speculative cache-line split load uops dispatched to L1D.                                                                                |         |

| 05H           | 02H            | MISALIGN_MEM_REF.STORES | Speculative cache-line split Store-address uops dispatched to L1D.                                                                       |         |

Figure 3.1: Snippet of event list for the Ivy Bridge microarchitecture.

Event select and fixed counter control MSRs are also documented although there is less variation between generations. A sample event select MSR from the SDM is shown in Figure 3.2. The various bits control the corresponding counter MSR. Bits 0–7 are for the event code, and bits 8–15 are for the subevent. Bits 16 and 17 specify whether execution in kernel mode and user mode should be measured, respectively. Bit 22 determines whether the counter is enabled or disabled.

3.2 Tools 3 Survey of PMUs

Figure 3.2: Layout of an Intel event select MSR.

In addition to the SDM, Intel also provides event data as JSON and TSV files for each microarchitecture [14].

Documentation for AMD is similar. Whereas Intel covers all microarchitectures in a single volume, AMD releases a separate BIOS and Kernel Developer's Guide (BKDG) for each processor family [18]. For instance, there is a dedicated document for family 10h processors [17]. The specification of events and PMUs MSRs is more or the less the same, so details have been omitted for brevity.

## 3.2 Tools

In this section, we study the actual use of some tools listed in Section 2.1.2, namely, perf\_event in the Linux kernel and the libpfm and PAPI libraries.

#### 3.2.1 perf\_event

The function prototype of perf\_event\_open is as follows:

The syscall sets up an event to be measured by a counter and returns a file descriptor which references the event. We will cover the parameters beginning with attr.

**Event selection:** The selection of events is completed through the type and config fields in attr. We are primarily concerned with 3 types:

- PERF\_TYPE\_HARDWARE

- PERF\_TYPE\_HW\_CACHE

- PERF TYPE RAW

The types PERF\_TYPE\_HARDWARE and PERF\_TYPE\_HW\_CACHE provide "generic" events across different platforms. The latter contains events concerning caches (e.g., cache accesses, DTLB misses, etc.) while the remaining events belong to the

<sup>&</sup>lt;sup>1</sup>Intel and AMD use different terminology. A microarchitecture is roughly equivalent to a family.

former (e.g., instructions executed, clock cycles, etc.). Other events not available as generalized events can be selected using PERF\_TYPE\_RAW. The event is set in config.

**Reading counter values:** There are two methods of reading event counts: *counting* and *sampling*.

- Counting reads event counts through the read syscall. The format is based on the read\_format field. Events in the same group can be read with a single invocation using PERF\_FORMAT\_GROUP.

- Sampling writes event counts to an mmap ring buffer, and either the sampling frequency or period must be specified. The sample\_type field defines the sample format. Values for events in the same group can also be read into a single sample using PERF\_SAMPLE\_READ.

Counter control and scope: Various other attributes are specified in attr. For instance, the disabled field determines if the counter is to be enabled immediately. Counters may be configured to exclude counting of events while executing in user mode and kernel mode using exclude\_user and exclude\_kernel, respectively. Monitored processes which are forked or spawn threads have the option of having children inherit their counters with the inherit field.

Monitored processes/threads and cores: The counter can be restricted to monitor a specific process/thread by passing in the PID/TID in pid. A value of 0 monitors the calling process/thread while a value of -1 monitors all processes/threads. Similarly, the counter only monitors a given CPU if its identifier is passed in as cpu.<sup>2</sup> A value of -1 monitors the specified process/thread on any core. If a PID/TID is passed in, the counter value follows the process/thread wherever it is scheduled to run (subject to CPU restrictions), i.e., the counter value is saved and restored if the process/thread migrates to a different core. Hence the returned file descriptor only references a *logical* counter as the underlying hardware counter may change. If a CPU ID is specified, a counter is allocated on the core to measure the event (subject to process/thread restrictions).

**Grouping counters:** Counters may be grouped together. Counters in the same group can be collectively enabled/disabled, and their values can also be read with a single function call. The only restriction is counters belonging to the same group must be on the same core, and they are to be scheduled together. Passing in group\_fd = -1 creates a new group with the returned file descriptor as the *group leader*. Specifying the group leader of an existing group adds the new counter to that group.

<sup>&</sup>lt;sup>2</sup>Here CPU is defined as a logical core. Each logical core has its own unique identifier.

3.2 Tools 3 Survey of PMUs

**Miscellaneous options:** The parameters attr and flags contain many other options. However, the remaining functionality is not relevant for this thesis, so they have been omitted. Refer to the man page for more details.

**Counter operations:** Operations are performed with the ioctl syscall on file descriptors. The following are used to enable, disable, and reset counter values to zero:

- PERF\_EVENT\_IOC\_ENABLE

- PERF\_EVENT\_IOC\_DISABLE

- PERF\_EVENT\_IOC\_RESET

If PERF\_IOC\_FLAG\_GROUP is set, then the operations above are applied to all counters in the same group.

**Limitations:** The perf\_event\_open syscall has a number of limitations.

- The configuration pid = -1 and cpu = -1 is an invalid combination. The syscall sets up exactly one *logical* counter to measure the specified event, and it maps to at most one hardware counter at any given time. Monitoring all processes on all cores would violate this.

- The inherit bit has no effect on existing children, for it would be impossible to apply this change retroactively.

- The options PERF\_FORMAT\_GROUP and PERF\_SAMPLE\_READ are incompatible with inherit since reading counter values of children could potentially require reading counters on different cores, causing synchronization problems

- Ring buffers for sampling must pinned to memory, so users may have to increase RLIMIT\_MEMLOCK.

- The syscall is an abstraction layer, so users cannot select the underlying hardware counter. This restricts the control users have over multiplexing counters.

#### 3.2.2 libpfm

The purpose of libpfm to is allow users to select events using self-evident names instead of event codes and subevent umasks, so it is not responsible for configuring PMU MSRs. In practice, libpfm is most commonly used to prepare the attrargument for perf\_event\_open by setting type to PERF\_TYPE\_RAW and filling in the appropriate value in config according to the given event name. The function prototype is shown below:

The first argument is reserved for the event name string. The function can limit the scope of counters in attr to specific protection rings with dfl\_plm. Although there are multiple levels, only PFM\_PLM0 and PFM\_PLM3 are used. The

3.3 Portability 3 Survey of PMUs

former corresponds to kernel mode while the latter is normally user mode. For use with perf\_event, os is set to PFM\_OS\_PERF\_EVENT. In this case, users may ignore dfl\_plm and set the appropriate flags in attr before passing it to the syscall.

The library provides a list of event names which it translates to event codes for each microarchitecture. While the lists are not complete, they are comprehensive enough to cover frequently used events.

#### 3.2.3 PAPI

PAPI is another library dedicated to cross-platform support of PMUs. Whereas perf\_event provides the functionality to access PMUs and libpfm allows users to select events, PAPI covers both domains.

PAPI groups events into event sets which are similar to groups in perf\_event. The following functions are responsible for event set management:

```

int PAPI_create_eventset(int *EventSet)

int PAPI_cleanup_eventset(int *EventSet)

int PAPI_destroy_eventset(int *EventSet)

int PAPI_add_named_event(int EventSet, char *EventName)

int PAPI_set_multiplex(int EventSet)

```

PAPI supports both generic and microarchitecture-specific events under the names standardized and native events, respectively, and it is possible to select events with names instead of event codes and umasks. Event sets may also be multiplexed.

Performance counters are managed with the following functions:

```

int PAPI_reset(int EventSet)

int PAPI_start(int EventSet)

int PAPI_stop(int EventSet)

int PAPI_read(int EventSet, long long *values)

```

# 3.3 Portability

The issue of portability is clearly visible since both perf\_event and PAPI attempt to address the problem by introducing generic events. However, we note this approach has three shortcomings:

- The set of generic events is very limited. For instance, perf\_event only defines 17 generic events as of Linux 4.7 while each PMU typically supports hundreds of events.

- 2. Not all generic events are available on all platforms, i.e., there are generic events which cannot be mapped to suitable events on some processors. If users are restricted to generic events which are always available, they are presented with an even smaller set, further limiting the usefulness of PMUs.

- Although PMUs may have events with identical or similar names, it does not mean they are equivalent. For example, Intel does not include prefetches in last-level cache misses or references, but other vendors may. Therefore,

generic events give users some degree of convenience, but do not completely solve the problem.

## 3.4 Performance Overhead

The low performance overhead has been mentioned as an incentive for using PMUs to obtain system diagnostics [1, 24, 44]. We perform microbenchmarks to verify such claims and to provide concrete numbers on the cost of reading counter values.

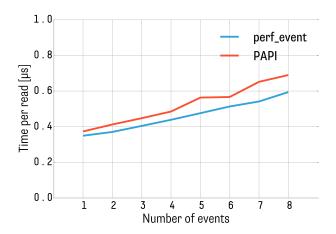

The benchmarks were performed on *Babybel*. For all benchmarks in this thesis, refer to Appendix A for details such as the hardware configuration, operating system, etc. Event values of event groups were read with bulk operations for perf\_event and PAPI 5.4.3, and the group size was varied. Each benchmark performed a total of 10,000,000 read operations, and we calculated the average time.

Figure 3.3: Cost of counter reads.

From Figure 3.3, we observe reads for larger group sizes take longer although the increase is not linear with respect to the number of events. Therefore, it is possible to reduce the overhead by leveraging event groups. Even if each event were read individually, the cost to read a single event is approximately 0.4  $\mu$ s, which is negligible. This corroborates earlier claims.

Finally, we also experimented with different events to determine the effect of selected events on read times. However, there was no observable variance, so the choice of events should be irrelevant.

# 3.5 Case Study: Scheduling

Now that we have examined various aspects of PMUs, we turn to case studies to understand how they are used in practice. The remainder of this chapter consists of two case studies. The objective of the first case study is to characterize system behaviour. The second case study looks at different types of interference on two separate machines.

Apart from the underlying hardware, thread placements are another major factor which influence application performance. Therefore, it is imperative for us to investigate how they are determined by schedulers and the ramifications of different thread placements.

#### 3.5.1 Preliminaries

We performed benchmarks using the applications PR, HD, and SSSP on *Gottardo* with the following partitioning schemes:

- shared cores

- whole sockets

- default

Every application was configured to spawn 32 threads (the machine has 64 logical cores). Refer to Appendix A for more details concerning benchmarks.

The logical cores of the 4 processors are numbered 1–16, 17–32, 33–48, and 49–64. Logical cores 1 and 9 are SMT threads on the same physical core. The same holds for 2 and 10, 3 and 11, etc. The numbering for remaining processors is analogous.

For *shared cores*, the first application was assigned cores 1–8, 17–24, 33–40, and 49–56 while the second application received the remaining cores. For *whole sockets*, the first application was allocated cores 1–32 while the second application received cores 33–64.

First, we ran each application alone, i.e., the cores reserved for the second application were idle. Next, they were run pairwise to observe the effects of interference, e.g., PR and PR, PR and HD, PR and SSSP, etc. This process was repeated for every partitioning scheme.

#### 3.5.2 Results

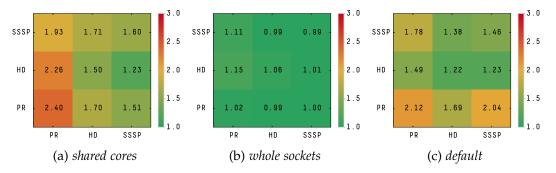

We define the **interference factor** of a given application and partitioning scheme to be the execution time of the interference case divided by the execution time of the base case. As mentioned in Appendix A.4, if an application was run for multiple iterations, we use the execution time of the first iteration only. E.g., if the execution times with and without interference are 60 s and 30 s, respectively, the interference factor is 60/30 = 2. Clearly, lower factors are desirable, and a factor of 1 is optimal as it signals the absence of performance degradation.

Observe that *whole sockets* exhibits the least interference while *shared cores* has the most in Figure 3.4. *Default* is somewhere in between. This reflects our choice of thread placements. The applications do not share any resources within individual CPUs with the *whole sockets* scheme. In contrast, *shared cores* results in applications sharing memory controllers, L1 to L3 caches, physical cores, etc. Since we selected two extremes, *default* naturally lies in the middle.

Determining the optimal thread placement for a given set of constraints is difficult. To illustrate, if we assume SSSP is a latency-sensitive task running alongside PR, then *whole sockets* is the best strategy as it causes the least interference for SSSP.

However, if we want to attain the highest throughput possible for PR, the other two schemes are preferable.<sup>3</sup>

Figure 3.4: Interference heatmaps for each partitioning scheme.

### **Scheduling History Reconstruction**

As part of this thesis, we developed a novel algorithm which reconstructs the thread placement history with performance counter samples. This is useful for understanding how the Linux scheduler allocates cores. In cases where there is perceived interference, we can see which resources are shared between applications. Obviously, this is only meaningful for *default* as other schemes pin threads to cores. The instrumentation of PMUs is described in Appendix A.4. Since we only make use of sample metadata and not event counts, we are not concerned with which events are actually measured.

Each sample contains the PID, TID, and CPU ID<sup>4</sup> in addition to the event and event count. Therefore, it is possible to track threads as they migrate between cores. The reconstruction algorithm is presented in Algorithm 1. The input is a list of samples sorted by timestamp in ascending order; the output is a list of periods. The general idea is to keep track of a set of *active periods* with an invariant: each thread or core has at most one active period at any point in time. We apply the following rules to generate the list of periods:

- 1. If the current core has an active period belonging to another thread, it is terminated, and a new one is created for the current thread.

- 2. If the current thread is continuing execution execution on the same core, the active period is extended.

- 3. If the current thread was migrated from another core, the previous active period is terminated, and a new one is created.

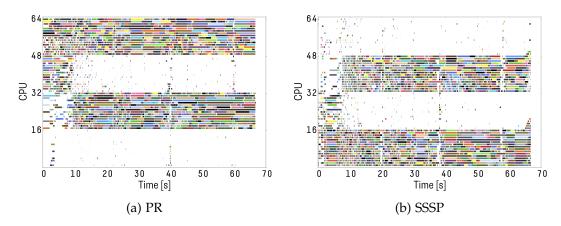

We display the scheduling histories of the benchmark involving PR and SSSP as an example in Figure 3.5. Each thread is shown in a distinct colour, and we use the numbering of CPU cores described above. Clearly, the Linux scheduler attempts to group threads belonging to the same process on the same processor. However,

<sup>&</sup>lt;sup>3</sup>A lower interference factor is not indicative of a shorter execution time. It is possible for a scheme to experience more interference, but still have a shorter execution time.

<sup>&</sup>lt;sup>4</sup>CPU IDs reference logical cores instead of whole processors.

## Algorithm 1 Scheduling history reconstruction

```

1: function Reconstruct-Scheduling-History(samples)

2:

periods = LIST()

3:

active_periods = DICT() // Key = TID, value = period

4:

last\_tids = DICT()

// Key = CPU, value = TID

5:

for all sample \in samples

6:

// If another thread was running on current CPU, end its active period.

7:

prev\_tid = GET(last\_tids, sample.cpu)

8:

if prev\_tid \neq NULL and prev\_tid \neq sample.tid

9:

ADD(periods, GET(active_periods, prev_tid))

{\tt REMOVE}(active\_periods, prev\_tid)

10:

11:

// Get active period of current thread if it exists.

12:

period = GET(active\_periods, sample.tid)

13:

if period \neq NULL and period.cpu == sample.cpu

14:

// Thread was running on same CPU, so extend period.

15:

period.end = sample.time

16:

else

17:

// If the active period is on another CPU, end it and clear CPU state.

18:

if period \neq NULL // Condition period.cpu == sample.cpu implied

19:

ADD(periods, period)

20:

REMOVE(last_tids, period.cpu)

// Create new active period.

21:

new_period = Create-Period(sample.cpu, sample.tid, sample.time)

22:

23:

SET(active_periods, (sample.tid, new_period))

set(last_tids, (sample.cpu, sample.tid))

24:

25:

return periods

```

there is some unnecessary overhead as threads from the same task are frequently migrated between cores. In this particular case, *default* behaves similarly to *whole sockets*. However, we have also seen scenarios where it is not as clear cut and threads belonging to different processes are scheduled on the same socket. The cost of thread migration is not merely limited to context switches. For example, machines having multiple NUMA nodes may initially allocate memory on the first NUMA node a thread is scheduled on. Then subsequent migrations run the risk of introducing additional memory latency.

Figure 3.5: Scheduling histories of PR and SSSP.

Basically, the Linux scheduler tries to strike a balance between latency and throughput, yet it is still difficult to impose specific constraints users may need. This is complicated by the fact that finding an optimal thread placement is non-trivial. As it has been shown scheduler bugs can lead to severe performance issues [29], the reconstruction of scheduling histories using performance counters has potential use cases since users can gain additional insight into the system.

#### Algorithm 2 Scheduling history reconstruction (auxiliary function)

```

1: function Create-Period(cpu, tid, time)

```

- 2: period.cpu = cpu

- 3: period.tid = tid

- 4: period.begin = time

- 5: period.end = time

- 6: return period

# 3.6 Case Study: Interference

Now that it has been shown applications can have complex interactions, we want to establish that PMUs are capable of diagnosing performance issues. In this section, we present case studies involving cache and memory interference.

#### 3.6.1 Cache Interference

In this case study we paired an application with good locality of reference and an application with poor locality to demonstrate contention on the last-level cache (LLC).

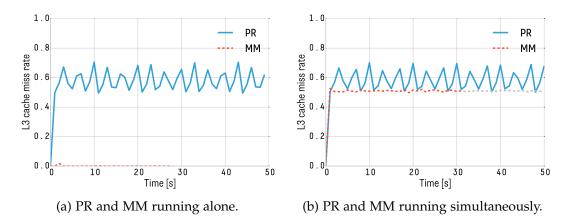

We ran MM with PR on *Babybel* (in this case study MM refers to MM1). PR was configured to use 8 threads. The PR threads and the MM process were pinned to separate cores on the same processor. *Babybel* has 2 processors with 10 cores each, so one processor had 9 cores in use while the remaining core and all cores on the other processor were idle. The following two events were used to calculate the L3 cache miss rate [11]:

- LONGEST\_LAT\_CACHE.REFERENCE

- LONGEST\_LAT\_CACHE.MISS

The L3 cache miss rates of the applications running alone are shown in Figure 3.6a. MM and PR have average cache miss rates of 0.0008 and 0.57, respectively. The low miss rate for the former can be explained by the fact the input and output matrices are both approximately 2 MB each and fit into the processor's L3 cache (25 MB). In contrast, PR has a much higher cache miss rate which explains consumption of memory bandwidth in the previous case study.

The results of the applications running side by side are presented in Figure 3.6b. The cache miss rate of MM dramatically increases to 0.57 whereas the rate for PR remains steady at 0.58. However, the elevated cache miss rate resulted only in an 8.9% increase in execution time for MM. Because the overall execution

Figure 3.6: L3 cache miss rates of PR and MM instances.

time of MM is shorter than PR, we restarted MM after the program finished in Figure 3.6b. The continued execution is indicated by the grey line.

At a glance, the increases in the cache miss rate and execution time appear to be disproportionate; however, examination of the L2 cache miss rate clarifies this—it is relatively low at 0.07. As only a small number of requests reach L3 cache, an increase in L3 cache misses has limited effect on the execution time.

Unlike the L3 cache, there is no event which counts all the different types of L2 references and misses collectively, so they had to be measured separately. The following events were required to calculate the L2 cache miss rate [11]:

- L2\_RQSTS.ALL\_DEMAND\_DATA\_RD

- L2\_RQSTS.DEMAND\_DATA\_RD\_HIT

- L2 RQSTS.ALL RFO

- L2\_RQSTS.RFO\_MISS

- L2\_RQSTS.ALL\_CODE\_RD

- L2 RQSTS.CODE RD MISS

As mentioned before, Intel processors only have 8 general-purpose performance counters per core. Consequently, the data for the L2 cache was collected in a separate run with identical configuration.

#### 3.6.2 Memory Interference

Memory interference is caused by applications with working sets unable to fit inside the CPU cache and/or poor locality of reference. Typically, such applications have higher L2 and L3 miss rates which result in an increased number of main memory accesses. This in turn can lead to contention on memory controllers and/or interconnect paths.

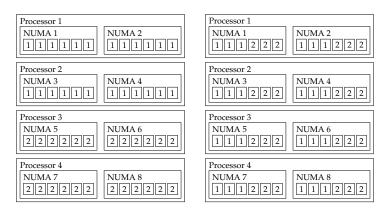

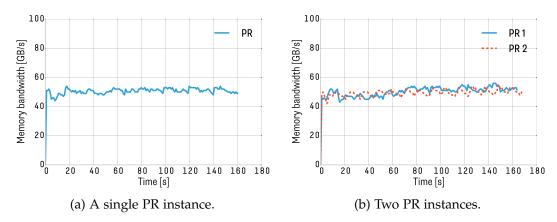

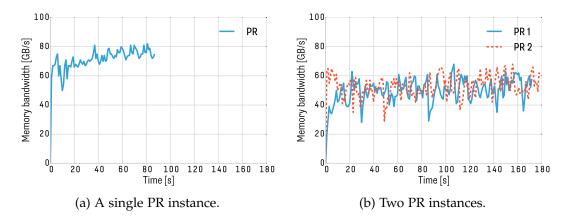

To show the effects of memory interference, we measured the memory bandwidth of PR on *Appenzeller*. Memory bandwidth was calculated using a formula obtained from an AMD white paper [19]. The event "DRAM Accesses" was used to count memory accesses [18].

Figure 3.7: Thread placement strategies 1 (left) and 2 (right).

We ran two benchmarks: (1) one instance of PR running alone and (2) two instances of PR running simultaneously. Each instance of PR was configured to use 24 threads (the machine has 48 cores). The threads were pinned to cores during execution to allocate memory controllers and avoid interference by the Linux scheduler. We ran each benchmark with two different thread placement strategies. The first strategy assigned 2 entire processors to each PR instance, which translates to 4 whole NUMA nodes. For the second strategy, each PR instance was allocated half of every NUMA node. A graphical depiction is given in Figure 3.7

Figure 3.8: Memory bandwidth of PR instances distributed on 4 NUMA nodes.

In the benchmarks for the first strategy, the execution time for a single PR instance running alone is around 162 seconds, and the measured memory bandwidth is approximately 51 GB/s (c.f. Figure 3.8a). If two PR instances are executed together, the execution time and memory bandwidth remain roughly constant. The two instances do not interfere with each other since the threads of instances are assigned to separate sockets.

For the second strategy, each PR instance received half of every NUMA node, i.e., each instance gets 3 out of 6 cores on all NUMA nodes. We observe the execution time of a single PR instance is nearly halved (c.f. Figure 3.9a). We attribute this to the fact that we now have the ability to make use of twice the number of

Figure 3.9: Memory bandwidth of PR instances distributed on 8 NUMA nodes.

memory controllers in the system. We see that the memory bandwidth is roughly 21 GB/s higher than in Figure 3.8a. However, once we execute two PR instances simultaneously on the machine, we see that the execution time goes up to approximately 176 seconds and the memory bandwidth decreases to around 52 GB/s. Assuming the two instances share memory controllers fairly, each instance receives the equivalent of  $0.5 \times 8 = 4$  memory controllers. The execution time and memory bandwidth attained by instances therefore appears to be dependent on the number of available memory controllers.

#### 3.7 Discussion

From the scheduling case study, we verify the claim that running tasks on modern systems result in complex interactions, and finding an optimal thread placement for a given set of constraints is a difficult problem. The case study on interference then goes on to show PMUs are able to make inroads to a solution by gathering data on hardware components.

It should be noted both case studies are representative of typical use cases of performance counters. One normally proceeds with the following steps:

- 1. Formulate an objective.

- 2. Observe the behaviour of the system.

- 3. Experiment with various events.

- 4. Adjust the system.

Using the memory interference case study as an example, the objective was to determine the reason why the two thread placement strategies resulted in different performance characteristics. Shared resources in the memory hierarchy are often contended, so we might hypothesize either CPU caches or memory controllers are the bottleneck. Then trial and error is required to find a suitable event capable of diagnosing the problem. The conclusion is to allocate the highest number of NUMA nodes possible without having to coschedule PR instances on the same NUMA nodes.

3.7 Discussion 3 Survey of PMUs

While this approach is valid and feasible, it suffers from two limitations: (1) the selected events are specific to this machine, and (2) the selection of events is a manual process which is labour-intensive and requires domain knowledge. The first limitation is evident in all applications of performance counters. Previous applications of performance counters also experienced this very same problem. Portability itself is not a showstopper, but the second limitation makes it impossible for this approach to scale. The requirement to understand both the hardware and implications of various events also raises the entry bar. Moreover, event selection is inherently time-consuming, so it causes users to automatically turn to a small set of candidate events such as cache misses or memory accesses. While these may be relevant events for performance issues, they are not necessarily the best events. The failure to consider a wider range of events opens up the possibility of passing over more suitable candidates.

We therefore propose a new framework which is required to be (1) portable across *all* architectures and (2) capable of *automatically* selecting relevant events for users. Although we have seen numerous applications of PMUs, we will restrict ourselves to detecting and classifying interference for now. The steps for our proposal are as follows:

- 1. Define list of performance events.

- 2. Run set of applications and collect measurements for each event.

- 3. Determine which events are indicative of interference.

- 4. Classify the types of interference indicated by the selected events.

Step 1 is straightforward as vendors provide a list of events for each CPU. We select as many events as possible, but uncore events are excluded since all processes on the same socket share the same count for an uncore event. Therefore, it is impossible to tie event counts to a specific process.

Step 2 requires an application set containing a mix of programs which covering common workloads of the majority of users. This is difficult as the applications must also exhibit contention of various shared resources when run together. We begin with a small set with the future plans to expand it.

Step 3 will involve a binary classifier which determines whether certain event sets serve as effective heuristics for detecting performance degradation.

Step 4 is reserved for future work.

However, since CPUs possess a limited number of performance counters with respect to the number of measurable events, we must first group similar events before proceeding to interference detection. Consequently, we will discuss our application set and possible approaches for event grouping in the next chapter.

# 4 Event Space Reduction

Recall the wide gap between the number of countable events and available counters in Figure 1.1. The ability to only measure a limited number events leads to two immediate questions:

- 1. How many events are needed to detect interference?

- 2. Which events are needed to measure to detect interference?

Ideally, we would like to see a change in event counts in the presence of interference, and previous studies which used performance counter measurements as heuristics prove this is possible. However, the minimum number of events necessary to detect interference is an open question. Our first step is then to find the intrinsic dimensionality of the event space. Next, we must reduce the event space to allow users to gather information without measuring every single event. This involves grouping correlated events together, and we evaluate several grouping schemes.

## 4.1 Preliminaries

As our solution is designed with a view to solve portability issues, we do not give answers specific to any platform. Instead, we present a framework which is capable of reducing the event space on any machine by running a predefined set of applications known as the *application set*. We will begin by describing it in detail.

#### 4.1.1 Applications

The selection of applications must be sufficiently diverse to cover most workloads end users run. Furthermore, it must be capable of causing various types of interference. In other words, it moves the burden of experimenting with various events under different workloads away from end users. Due to these reasons, it is a challenge to add new applications. We begin with a small set of applications with plans to expand it at a later date. Currently, the application set consists of the following applications:

• PR

- MM

- SORT

PR instances are configured to spawn 8 threads, and all three variations of MM are used, i.e., MM1, MM2, and MM3.

#### 4.1.2 Benchmarks

A variety of benchmarks were run with the selected applications on *Babybel*. The complete list is shown in Table 4.1. First, each application was run independently. Next, applications were paired together to generate interference. Benchmarks involving paired applications were run with three different partitioning schemes:

- shared cores

- shared sockets

- whole sockets

The table explicitly documents the cores assigned to each application as a set, e.g., for the benchmark MM + PR (*shared sockets*), MM and PR are assigned the core sets {1} and {2–9}, respectively. Hence MM runs on core 1 whereas PR is allocated cores 2–9. Recall *Babybel* has 2 processors with 10 cores each. We label the cores in the first processor 1–10 and the cores in the second 11–20.

Notice that PR is run independently twice. This is because the partitioning of cores for *shared sockets* is different from the other two schemes, so a different baseline is necessary. Normally, the scheme column is left empty if applications are running alone. In addition, MM should be expanded into MM1, MM2, and MM3, e.g., the row MM + SORT (*shared cores*) should be read as three rows:

- MM1 + SORT (shared cores)

- MM2 + SORT (shared cores)

- MM3 + SORT (shared cores)

| Application(s) | Scheme         | Core Set(s)                  |

|----------------|----------------|------------------------------|

| MM             |                | {1}                          |

| SORT           |                | {1}                          |

| PR             |                | {1-8}                        |

| PR             | shared cores   | {1–4, 11–14}                 |

| MM + SORT      | shared cores   | ({1}, {1})                   |

| MM + SORT      | shared sockets | ({1}, {2})                   |

| MM + SORT      | whole sockets  | ({1}, {11})                  |

| MM + PR        | shared cores   | ({1}, {1–8})                 |

| MM + PR        | shared sockets | ({1}, {2–9})                 |

| MM + PR        | whole sockets  | ({1}, {11–18})               |

| SORT + PR      | shared cores   | ({1}, {1–8})                 |

| SORT + PR      | shared sockets | ({1}, {2–9})                 |

| SORT + PR      | whole sockets  | ({1}, {11–18})               |

| PR + PR        | shared cores   | ({1-8}, {1-8})               |

| PR + PR        | shared sockets | ({1-4, 11-14}, {5-8, 15-18}) |

| PR + PR        | whole sockets  | ({1–8}, {11–18})             |

Table 4.1: List of benchmarks.

#### 4.1.3 Event Selection and Measurement

The libpfm library provides events for the Intel Xeon E5-2670 v2 processor through the PMU module *ivb\_ep*, and as many events as possible were selected. The list of 190 selected events can be found in Appendix B.

Uncore events were excluded since their counts cannot be traced back to a specific process/thread. In more concrete terms, suppose there is an uncore event measuring the number of memory bus transactions. The event count includes transactions for all processes running on the socket as we cannot restrict it to a specific process or core.

The processors in *Babybel* only have 8 general-purpose counters per core, so it is impossible to measure 190 events simultaneously. As a result, each benchmark was run multiple times to collect measurements for all events. Iterations for the same benchmark had identical configuration, with the exception of monitored events. The sample standard deviation of execution times was calculated for each execution. We define the *relative standard deviation* to be  $\sigma/\mu$ , where  $\sigma$  denotes the standard deviation and  $\mu$  is the mean. The maximum maximum standard deviation across all executions is 0.96%. Hence all the iterations of the same benchmark were similar in terms of execution time.

## 4.1.4 Data Representation

Data mining techniques frequently require input to be represented as matrices. This part describes how we represent sample counts for events as a matrix. Each application is understood to be a single process which may contain multiple threads, and we always use a time slice of 1 second in this thesis.

Suppose we measured n events  $e_1, \ldots, e_n$  for a process p on a machine with m cores (note that the threads of p may execute on multiple cores simultaneously), and the execution time was t seconds. The execution time can be divided into time slices of equal length. The delta of an event is defined to be the increase in the event count during a specific time slice (deltas are always nonnegative integers). Since we have separate counters for each core, they must be aggregated for every time slice. Let  $c_{ijk}$  denote the increase of  $e_i$ 's event count during the jth time slice on core k. Thus the delta of  $e_i$  for the jth time slice is

$$c_{ij} = \sum_{k=1}^{m} c_{ijk}.$$

Then the deltas of all events for the *j*th time slice can be represented as a column vector

$$x_j = \begin{bmatrix} c_{1,j} \\ \vdots \\ c_{n,j} \end{bmatrix}.$$

By defining column j of matrix X to be the vector of deltas for time slice j, we obtain

$$X = \begin{bmatrix} x_1 & \dots & x_t \end{bmatrix}.$$

In other words, row i of X is simply a vector containing  $e_i$ 's deltas in chronological order.

In addition, data from several processes may be concatenated together. Assume we have matrices  $X_p$  and  $X_q$  for processes p and q, respectively. Then define

$$X_{pq} = \begin{bmatrix} X_p & X_q \end{bmatrix}$$

to be the combined matrix. Clearly, this can be done for an arbitrary number of processes.

For the remainder of this chapter, matrix X is defined to contain data for all executions of applications, i.e.,

$$X = \begin{bmatrix} X_{p_1} & \dots & X_{p_N} \end{bmatrix}$$

,

where N is the number of executions. We also exclude rows which only contain 0, i.e., events whose deltas are all 0. There are a number of possible explanations for this phenomenon. There may be a software or hardware bug affecting specific events, or the events were simply not triggered.

There are 164 remaining events out of 190, and hence  $X \in \mathbb{Z}_{\geq 0}^{164 \times N}$ , where  $\mathbb{Z}_{\geq 0}$  denotes the set of nonnegative integers. The excluded events are listed in Appendix B. Note that any conclusions obtained from operations on X should be valid for all applications as X contains data from every execution in the application set.

We take the sum of counts of all threads for each application because we are primarily concerned with the overall performance and not the progress of individual threads. For example, in cases where only a few threads are affected by interference, we need not be overly concerned. However, carrying out aggregation of event counts implies we lose fine-grained control, so there are also disadvantages of this approach. An alternative is to analyze each thread on its own.

# 4.2 Dimensionality Analysis

In this section, we apply principal component analysis (PCA) to find the *intrinsic dimensionality*, i.e., the number of variables determining the data points. PCA projects each column  $x_i \in \mathbb{R}^D$  of  $X \in \mathbb{R}^{D \times N}$  onto a subspace to obtain  $\tilde{x}_i \in \mathbb{R}^K$ , and the objective is to select the smallest possible  $K \leq D$  such that each column retains its "features" [22]. Here D = 164 since there are 164 events in X.

Recall we have multiple runs of each application. Suppose p' and p are executions of an application with and without interference, respectively. Define

$$X_{pp'} = \begin{bmatrix} X_p & X_{p'} \end{bmatrix}.$$

After reducing the event space, we need to be able to differentiate whether vectors originate from p or p' to detect interference, and selecting a higher K obviously increases this probability. However, if K is small, then not all 164 events need to be measured to obtain sufficient data. Moreover, K may be used to determine the number of groups when performing event grouping.

4.2.1

Subspace Dimensionality and Approximation Error

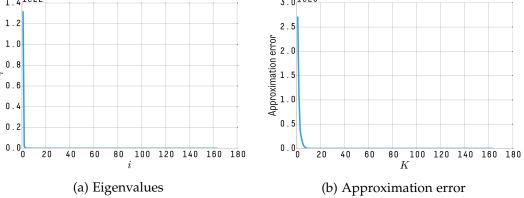

Figure 4.1: Eigenvalues and approximation error of PCA.

As usual, matrix X was mean-centered before applying PCA by obtaining the eigendecomposition of the covariance matrix with functions from NumPy [35, 36, 37]. The results are shown in Figure 4.1. We are primarily concerned with how the approximation error changes according to K. There is a visible "knee" between K = 1 and K = 10 since the error decreased dramatically in this range, which implies the data points (i.e., the columns of X) can be orthogonally projected onto a low-dimensionality subspace. Assuming we get the maximum error when K = 1, further inspection reveals selecting K = 4 returns an error of less than 10% (8.16%). Increasing *K* to 7 reduces the error to below 1% (0.95%).

#### **Projection of Data Points onto Subspaces** 4.2.2

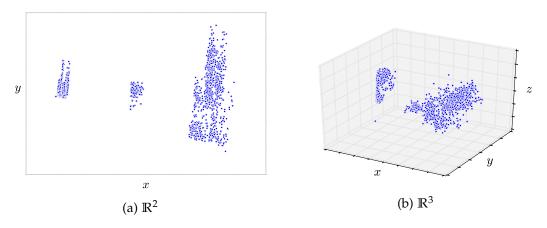

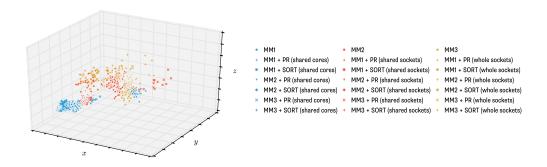

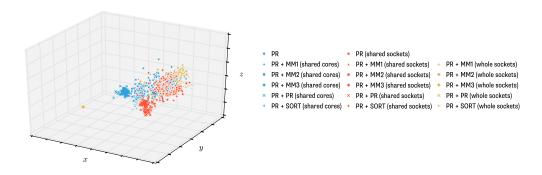

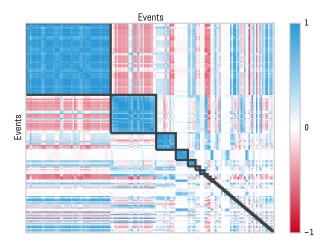

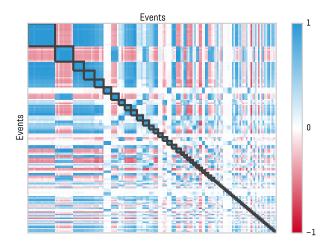

In order to visualize the data, the points are projected onto  $\mathbb{R}^2$  and  $\mathbb{R}^3$  in Figure 4.2. We see the points retain their "structure" when *K* is reduced from 3 to 2. This suggests K = 3 may be a valid choice for the intrinsic dimensionality of the event space.

Figure 4.2: Projection of data points onto subspaces.

However, we need to verify two additional conditions. First, points originating from the same execution should be clustered together. All of the applications in the application set only have one phase, so in theory the event deltas should be similar for all time slices. One minor exception is be SORT as it may behave differently as it makes progress. Second, different executions should be distinguishable. Executions exhibiting interference normally have irregular counter values. Next, we plot each application in a separate graph.

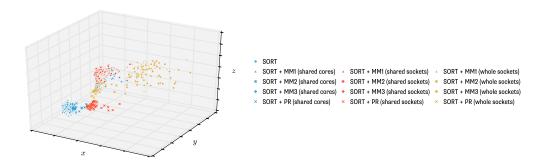

Figure 4.3: Data points of SORT.

Figure 4.3 exclusively contains data points belonging to executions of SORT. Each execution can be identified by a unique shape and colour. For instance, blue circles denote an execution of SORT without interference, and red squares denote an execution of with MM2 causing interference with the *shared sockets* partitioning scheme. Observe that data points from the same execution are frequently close to each other although there are some outliers, and certain executions exhibit more variance. In addition, executions experiencing more severe degradations are easily distinguishable—executions with the *shared cores* scheme form a cluster which is further removed from other executions.

Figure 4.4: Data points of MM.

The same process is done for MM and PR in Figures 4.4 and 4.5, respectively. The MM application is also a single-threaded process like SORT. However, we experimented with three input matrices of different sizes as they act on the LLC differently. Smaller matrices which fit inside the cache have very low miss rates while larger ones have higher miss rates. Regardless of MM's effect on the LLC,

we can draw similar conclusions to SORT since executions experiencing more interference form an distinct cluster.

In contrast, the reaction of PR to interference is a bit more varied since it is a multithreaded program. When PR experiences interference caused by a single-threaded program (e.g., SORT and MM), the performance degradation is not as pronounced. We also see a serious slowdown when two PR instances are coscheduled with the *shared cores* scheme. Therefore, it is possible to conclude there are varying *degrees* of interference—some severe and others less so—which can be detected and visualized through performance counter measurements.

Figure 4.5: Data points of PR.

Clearly, if these results can be obtained from a 3D subspace, then all of the above (and possibly more) should be achievable with subspaces containing more dimensions. It is important to note the chosen value for K, i.e., the intrinsic dimensionality or number of principal components, does not directly translate to the number of events which should be measured. However, it does suggest only a fraction of events are required to preserve information from the complete set of events. Finally, we wish to emphasize the generality of the dimensionality analysis again. PCA was performed on data points originating from all applications in the application set as well as executions with and without interference. Thus the selected K is not specific to any application, nor is it limited to a specific type of interference. This generality will continue to apply to all following results.

# 4.3 Event Similarity

By applying PCA, it is possible to show the intrinsic dimensionality of the event space is less than 10. However, PCA only tries to preserve information when mapping data points to a subspace and does not suggest the dimensions which are important, i.e., PCA does not determine the events which should be measured. In other words, *K* provides an estimate of *how much* the event space may be reduced, but we still need to explore *how* to perform the reduction.

Naturally, clustering is one way of proceeding, and there is certainly no shortage of clustering algorithms; one classic example is *k*-means clustering. The core of such algorithms involves defining *similarity* between objects, e.g., the Euclidean

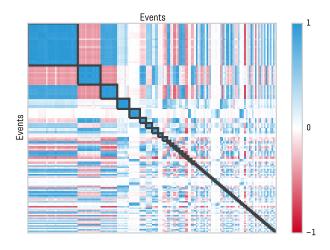

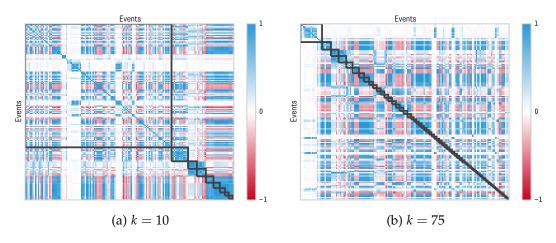

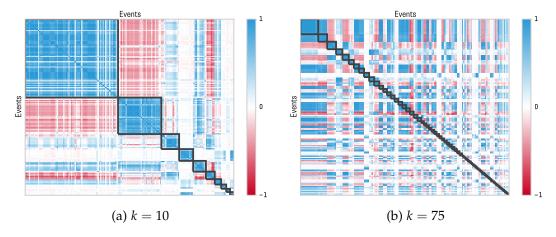

distance between points is often used with k-means. In this section, we will discuss (1) how similarity is formally applied to the matrix X, (2) different notions of similarity, and (3) evaluate their suitability for X.