# Efficient Design Space Exploration for Embedded Systems

# A dissertation submitted to the SWISS FEDERAL INSTITUTE OF TECHNOLOGY ZURICH

for the degree of Doctor of Sciences

presented by

SIMON KÜNZLI

Dipl. El.-Ing.,

Swiss Federal Institute of Technology Zürich, Switzerland

born August 4, 1975

citizen of Switzerland

accepted on the recommendation of Prof. Dr. Lothar Thiele, examiner Prof. Dr. Luca Benini, co-examiner

2006

Examination date: April 20, 2006

TIK-SCHRIFTENREIHE NR. 81

Simon Künzli

# Efficient Design Space Exploration for Embedded Systems

A dissertation submitted to the Swiss Federal Institute of Technology Zurich for the degree of Doctor of Sciences

Diss. ETH No. 16589

Prof. Dr. Lothar Thiele, examiner Prof. Dr. Luca Benini, co-examiner

Examination date: April 20, 2006

### **Abstract**

Design space exploration is an important factor in embedded systems design. During several steps in a state-of-the-art design flow, designers have to decide between many design alternatives. The decisions are located at various levels of abstraction. In addition, the choices affect several design goals, the alternatives therefore represent a multi-criteria decision problem.

Further, the space of possible solutions is normally very large, i.e., many design alternatives exist. As a consequence, exhaustive search of the design space is prohibitive, and more sophisticated techniques have to be used to find "good" solutions. To judge the quality of a new design, the performance of a system for a given application is one core criterion. Potential performance metrics are memory demand, response time, or data throughput of an application. As a consequence, one may ask the following questions:

- How can we assess the performance of a new design for a certain application?

- How do we find new design points in the design space?

- How can we automate the design space exploration process?

In this work, we investigate several aspects of design space exploration problems and try to answer these questions. In particular, we identify and discuss the building blocks for a design space exploration framework, namely design evaluation, search strategies, and design representation. Based on these building blocks, the main contributions of this work can be described as follows:

A new hybrid method for performance evaluation of embedded systems is presented. The new method allows the combination of existing methods for performance analysis. In particular, these methods can be analytic or simulation-based. We provide the required interfaces for this combination.

- We describe a new evolutionary multi-objective optimisation algorithm, that directly incorporates the user's preferences based on performance indicators. It is easy to use and shows superior performance on test benchmarks and on design space exploration problems.

- A novel software framework for design space exploration is presented. Using the framework we can re-use existing software blocks and need to implement only a few components that represent the specific problem.

### Kurzfassung

Die Erforschung des Entwurfsraums ist eine wichtige Tätigkeit im Rahmen des Entwurfs von Eingebetteten Systemen. Wenn Systeme nach aktuellen Entwurfsabläufen entwickelt werden, müssen die Entwickler immer wieder zwischen verschiedenen Entwurfsalternativen auswählen. Diese Entscheidungen werden auf verschiedenen Abstraktionsebenen getroffen. Zusätzlich haben diese Entscheide Auswirkungen auf verschiedene Entwurfsziele, die Auswahl der Entwurfsalternativen stellt deshalb ein Mehrziel-Optimierungsproblem dar.

Der Entwurfsraum der möglichen Lösungen ist normalerweise sehr gross, d.h. es existieren viele verschiedene Alternativen für den Entwurf. Als Konsequenz kann nicht jede Lösung im Suchraum untersucht werden, sondern es müssen geeignete Methoden angewendet werden, um in einem Teil des Suchraumes die "guten" Lösungen zu finden. Die Performanz einer solchen Lösung für eine gegebene Anwendung ist ein Kernkriterium, um die Qualität des Systems zu ermitteln. Mögliche Metriken zur Bestimmung der Performanz sind Speicherverbrauch, Antwortzeit oder Datendurchsatz einer Anwendung.

Als Folge dieser Uberlegungen kann man sich die folgenden Fragen stellen:

- Wie kann man die Performanz eines neuen Entwurf für eine gegebene Anwendung bestimmen?

- Wie finden wir überhaupt eine neue Lösung im Entwurfsraum?

- Wie kann die Suche nach neuen Entwürfen automatisiert werden?

In dieser Arbeit untersuchen wir verschiedene Aspekte der Entwurfsraumsexploration und versuchen auf die obigen Fragen Antworten zu finden. Die einzelnen Bausteine für eine automatisierte Exploration, nämlich die Evaluation einzelner Lösungen, unterschiedliche Suchstrategien und die Repräsentation der Lösungen werden vorgestellt. Basierend auf diesen Bausteinen können wir nun die Hauptbeiträge dieser Arbeit präsentieren:

- Wir präsentieren einen neuen hybriden Ansatz zur Performanz-Analyse von Eingebetteten Systemen. Die neue Methode kombiniert existierende Verfahren, insbesondere Simulation und analytische Verfahren, und beschreibt auch die notwendigen Schnittstellen zwischen diesen.

- Ein neuer evolutionärer Algorithmus für die Mehrzieloptimierung wird vorgestellt, welcher Benutzerwünsche an die Suche, ausgedrückt durch Performanz-Indikatoren, direkt berücksichtigt. Der Algorithmus ist einfach zu benutzen und liefert für Probleme, bei welchen es um die Erforschung des Entwurfsraums geht, gute Resultate.

- Wir beschreiben ein Programm-Framework, welches für die Entwurfsraumsexploration verwendet werden kann. Mit dem Framework kann man schon bestehende Software-Blöcke wiederverwenden und muss nur wenige Komponenten, die das aktuelle Problem beschreiben, neu implementieren.

#### I would like to thank

- Prof. Dr. Lothar Thiele for being my advisor, letting me doing my own work very independently, but also always finding the time to have fruitful discussions if needed.

- Prof. Dr. Luca Benini for his agreement to be my co-examiner, for the interesting discussions on performance evaluation, and for the possibility to visit his lab in Bologna.

- Andreas Meier for always being ready to help and his moral support during the last weeks before submitting this thesis.

- Dr. Lennart Meier for the discussions about proper German language, hyphens, and all the other things that are to be discussed in a shared office.

- Prof. Dr. Samarjit Chakraborty for the collaboration and being my office mate in the first two years of my PhD studies. Starting to work with him was a very smooth dive into research, and also a great pleasure.

- all my colleagues at TIK with whom I had lots of interesting discussions, sometimes ending rather late and off-topic.

The work presented in this thesis was partly supported by the Innovation Promotion Agency CTI/KTI through project number 5500.2. This support is being gratefully acknowledged.

## **Contents**

| 1 | Intr | oductio |                                                    | 1  |

|---|------|---------|----------------------------------------------------|----|

|   | 1.1  |         | dded System Design                                 | 1  |

|   | 1.2  |         | ibutions                                           | 4  |

|   | 1.3  | Overv   | view                                               | 5  |

| 2 | Des  | ign Sp  | ace Exploration of Embedded Systems                | 7  |

|   | 2.1  | A Sim   | ple Example: Design Space Exploration of Cache Ar- |    |

|   |      | chitec  | tures                                              | 8  |

|   | 2.2  |         | action Layers in Design Space Exploration          | 11 |

|   | 2.3  |         | n Evaluation                                       | 13 |

|   | 2.4  |         | ration Method                                      | 14 |

|   | 2.5  |         | nary                                               | 16 |

| 3 | Des  | ign Eva | aluation                                           | 17 |

|   | 3.1  | Exam    | ple Systems                                        | 18 |

|   |      | 3.1.1   | Network Processor                                  | 18 |

|   |      | 3.1.2   | Multiprocessor Platform MPARM                      | 18 |

|   | 3.2  | Perfo   | rmance Analysis                                    | 19 |

|   | 3.3  |         | al Performance Analysis                            | 25 |

|   |      | 3.3.1   | Event Models and Resource Capabilities             | 25 |

|   |      | 3.3.2   | Analysing a Single Task                            | 27 |

|   |      | 3.3.3   | Multiple Streams on a Resource                     | 30 |

|   |      | 3.3.4   | Complex Systems with Multiple Resources            | 32 |

|   |      | 3.3.5   | Adaptation for Design Space Exploration            | 36 |

|   |      | 3.3.6   | Example System 1: Network Processor                | 38 |

|   | 3.4  | Simul   | lation-based Performance Analysis                  | 39 |

|   |      | 3.4.1   | Example System 1: Network Processor                | 40 |

|   |      | 3.4.2   | Example System 2: Multiprocessor Platform          | 44 |

|   | 3.5  | Comp    | parison between Simulation and Formal Method       | 45 |

|   |      | 3.5.1   | Example System 1: Network Processor                | 45 |

|   |      | 3.5.2   | Example System 2: Multiprocessor Platform          | 59 |

|   |      | 3.5.3   | Concluding Remarks                                 | 61 |

|   | 3.6  | Comb    | vination of Simulation with Formal Method          | 63 |

|   |     | 3.6.1 Interfaces between Simulation and Formal Method 6   | 3              |

|---|-----|-----------------------------------------------------------|----------------|

|   |     | 3.6.2 Benefits of hybrid approach 6                       | 6              |

|   |     | 3.6.3 Example System 2: Multiprocessor Platform 6         | 66             |

|   | 3.7 | Event Trace Generation                                    | 70             |

|   |     | 3.7.1 Requirements and Quality Assessment                 | 71             |

|   |     | 3.7.2 General Event Trace Generation                      | 72             |

|   |     | 3.7.3 Implementation                                      | 76             |

|   |     | 3.7.4 Results                                             | 79             |

|   | 3.8 | Summary                                                   | 32             |

| 4 | Sea | ch Strategies 8                                           | 35             |

|   | 4.1 | Multi-Objective Evolutionary Algorithms                   | 36             |

|   |     | ·                                                         | 37             |

|   |     |                                                           | 39             |

|   |     | 4.1.3 Variation                                           | 92             |

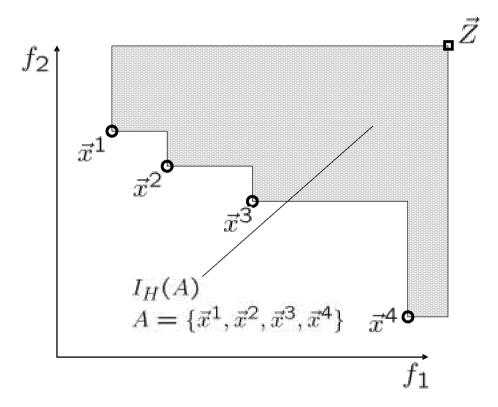

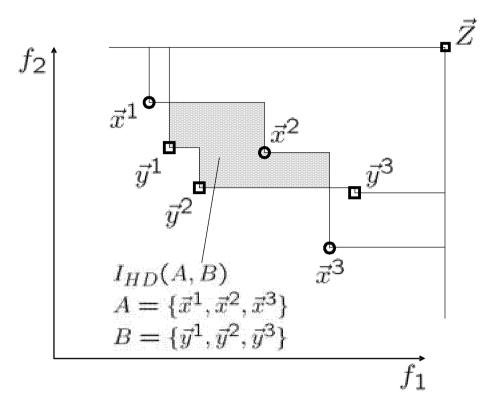

|   | 4.2 | Performance Indicators for Search Algorithms 9            | <del>)</del> 5 |

|   |     |                                                           | )5             |

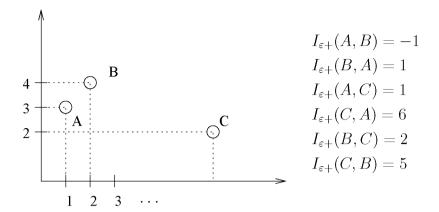

|   |     | 4.2.2 Multiplicative $\varepsilon$ -indicator             | 96             |

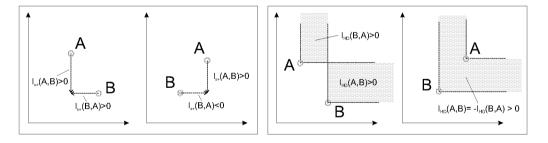

|   |     | 4.2.3 Coverage Indicator                                  | 96             |

|   |     | 4.2.4 Hypervolume Indicator                               | 97             |

|   |     | 4.2.5 Binary Hypervolume Indicator                        | 8              |

|   | 4.3 | Indicator-Based Evolutionary Algorithm                    | 9              |

|   |     |                                                           | 9              |

|   |     | 4.3.2 Preliminaries                                       | )1             |

|   |     | 4.3.3 Indicator-Based Selection                           | )1             |

|   |     | 4.3.4 Improving Robustness                                | )7             |

|   | 4.4 | Summary                                                   | )8             |

| 5 | Too | s and Applications                                        | 3              |

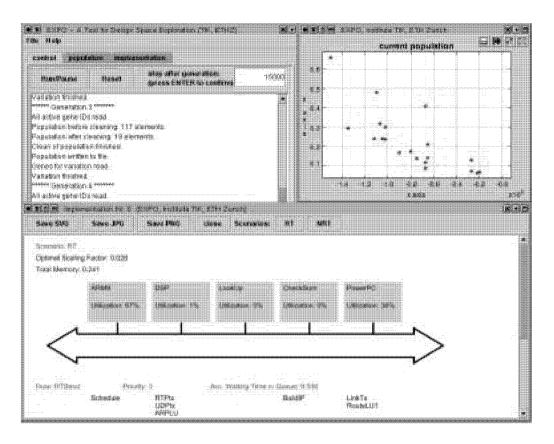

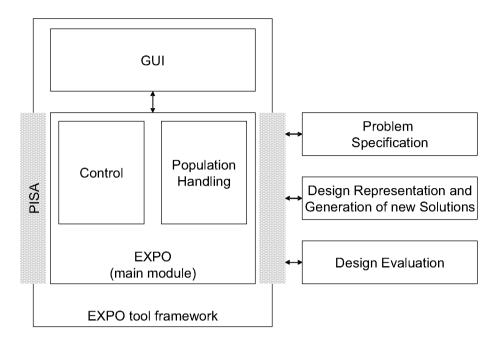

|   | 5.1 | EXPO: A General Framework for Design Space Exploration 11 | 3              |

|   |     | 5.1.1 Software Architecture                               | 4              |

|   |     | 5.1.2 PISA                                                | 5              |

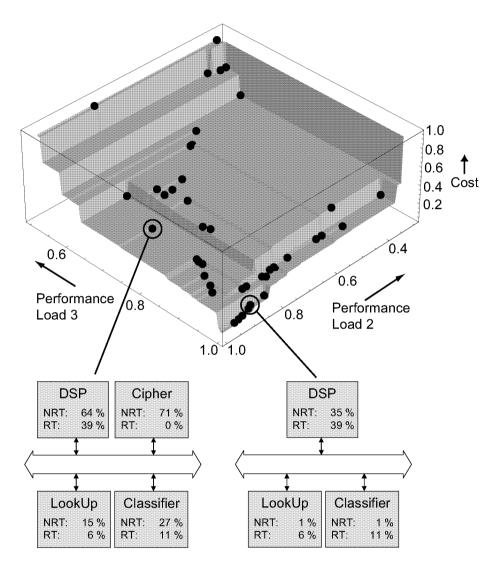

|   | 5.2 | Applications of Framework                                 | 9              |

|   |     | 5.2.1 Packet Processors                                   | 9              |

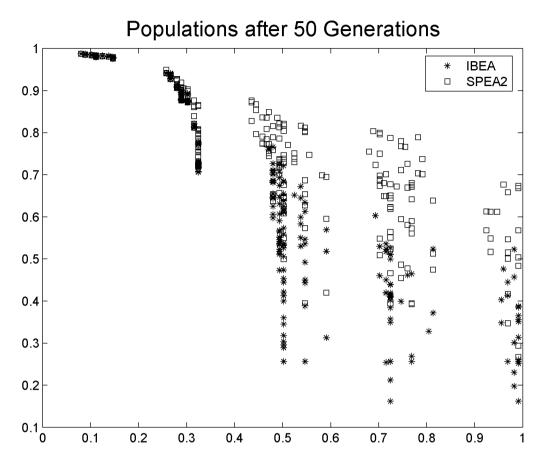

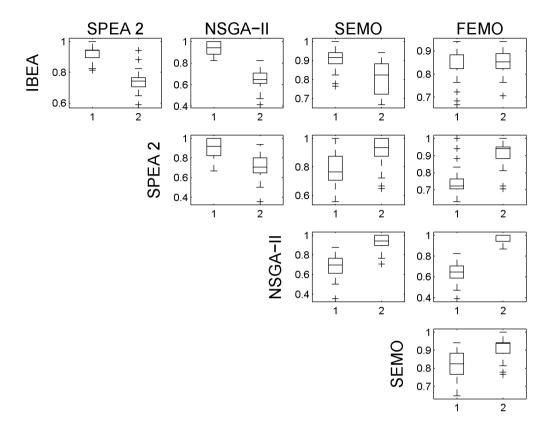

|   | 5.3 | Different Search Algorithms                               | 28             |

|   |     | 5.3.1 Benchmark Applications                              | 28             |

|   |     | 5.3.2 Test Cases                                          | 29             |

|   | 5.4 | Summary                                                   | 12             |

| 6 | Con | clusions 14                                               | 13             |

|   | 6.1 | Contributions                                             | 13             |

|   | 6.2 | Future Work 14                                            | 14             |

| Contents | ix |

|----------|----|

| Contents | 17 |

| A The EXPO Tool Framework  A.1 Interface Specification  A.2 Interface Gene | 14 | 6 |

|----------------------------------------------------------------------------|----|---|

| B Approximations for Real-Time Calcu                                       |    |   |

| Bibliography                                                               | 16 | 9 |

## Introduction

An embedded system can be defined as information-processing system that is embedded into its environment. Embedded systems are mostly dedicated to a certain application domain where they are customised to fulfil special-purpose tasks. Examples for embedded systems are processors in cars, mobile phones, or even coffee machines.

Embedded systems are ubiquitous, there are surveys that report of more than 50 embedded processors in an average household in the year 2002 (e.g. in [MSB+02]). Marwedel in [Mar03], and also Wolf in [Wol01] report that high-end cars even contain more than 100 processors at the beginning of the 21st century.

Designing an embedded system is a difficult task because the requirements change for every new system. The design flow has therefore to be flexible and generic enough to cope with the requirements and design constraints that a new design possibly imposes. The complexity of embedded system design is aggravated by the lack of generally accepted architectures, unlike in the domain of general purpose processors.

There are many different approaches to capture the embedded system design flow. In the next section, we will discuss a few examples and try to extract the principles common to all the methods.

### 1.1 Embedded System Design

Many design methods have been proposed and discussed over the last few decades. For software development, there is the waterfall design flow introduced by Royce [Boe88], in which the main design steps are performed one after the other from high abstraction levels to lower ones, starting from requirements, leading over architectural decisions and software integration, to testing and maintenance of the developed software. In this design model, there is only little feedback to the next-higher abstraction level. This top-down approach is ideal, but not realistic, because most design projects involve several revisions.

This behaviour is better captured with the spiral design flow [Boe88], where several versions of a system are built. Early versions are simple in nature, where later systems are more and more complex. On each design level, the design steps requirements, construction, and testing are performed. A possible drawback of the spiral model is that it may take too long, if too many spirals are performed (see [Wol01]). A design method that is based on a first prototype construction which is then improved in several iterations is called successive refinement design flow [Wol01]. The difference between these design flows lies in the point in time when design steps are taken at what level of accuracy, but not in the design steps itself.

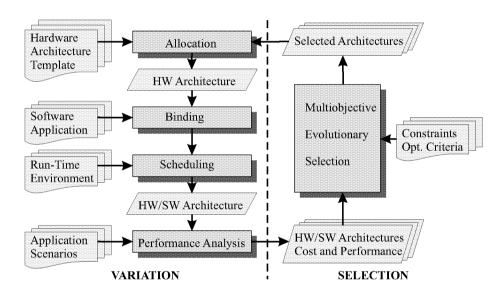

Wolf identified 5 major steps embedded system design [Wol01]. These are (1) the definition of requirements that can be functional as well as non-functional, and (2) the specification of the system behaviour. The specification serves as contract between the designers and the customers. In step (3) the architecture design, the overall structure of the system is designed, then it is partitioned into component blocks for hardware and software parts. In this step, system-level design decisions are made, such as allocation and binding of software blocks to hardware resources. The work presented in this thesis helps the designer to make these decisions. Step (4) deals with the design of the individual hardware and software components, and finally the whole system is integrated and tested in step (5).

Ernst proposes three main types of design tasks which can be identified in all design flows for embedded systems in [Ern03]:

- component/subsystem interfacing

- system verification

- system optimisation and design space exploration

These steps can be identified in many design flows implemented by commercial or academic methodologies. Examples are the SpecC design flow, COSYMA, the IMEC tool flow, Ptolemy II, and OCTOPUS (see [Mar03] and references therein).

As an example, we look at the SpecC design flow. Starting from an executable specification in SpecC, the next step performed in the SpecC

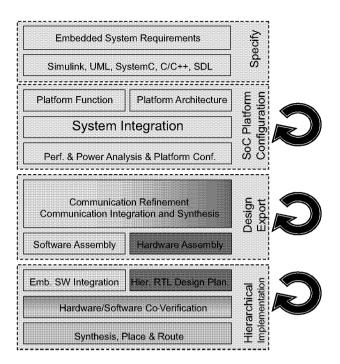

**Fig. 1:** Graphical representation of the design flow as developed within the SpeAC project.

design flow [GZD+00] for embedded systems is an architecture exploration. After this step, a chosen architecture with allocation, partitioning and scheduling is validated.

The design flow proposed in the European project SpeAC is shown in Figure 1. The design flow tackles different views of a design, namely a module and a system view across various levels of abstraction. At the design specification, for instance UML, Matlab/Simulink, SDL, C/C++ can be used separately or combined within one design. Afterwards SystemC can be used for integrating heterogeneously specified modules into a single simulation model. In Figure 1, also the steps at lower abstraction levels are shown. In the design flow, refinement steps occur at all levels of abstraction. Here, too, there are design space exploration tasks to be solved, e.g. at the platform configuration step, during the communication refinement, but also at low levels of system synthesis and placement/routing.

As a result of this short survey, we can identify the design task of *design space exploration* common to all proposed embedded system design flows. This thesis exactly deals with issues related to this task and proposes new models and methods for design space exploration. They should assist a designer in finding a good design. The next chapter discusses the various aspects of design space exploration and introduces a reader into the topic. This thesis is based on the following journal publications, conference

papers, and book chapters: [CKT+03b], [KTZ06], [KTZ05b], [KBTZ04], [CKT03a], [TCGK02a], [TCGK02b], [ZK04], [KPBT06], and [KT06].

#### 1.2 Contributions

In this thesis, we present results that ease the task of design space exploration for embedded systems. The main contributions are presented in the following.

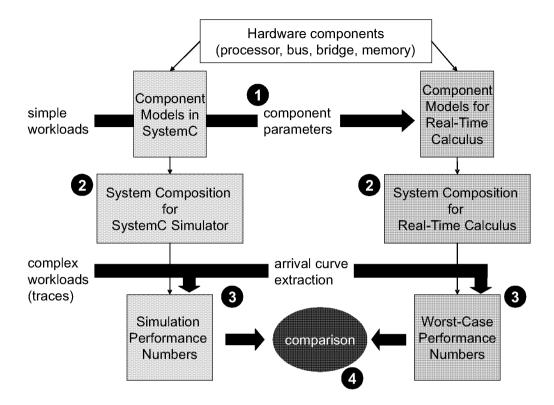

- 1. We describe a new, compositional performance evaluation method for embedded systems. The new method combines existing approaches for system-level performance analysis, namely a formal method and a simulation-based approach. To enable this combination, we define the interfaces needed between the different performance evaluation methods. As a core of the approach, we propose a method to generate simulation stimuli from analytical models. In addition, we introduce a measure to assess the quality of a generated simulation trace with respect to its analytical description. In order to show the applicability of this new approach for performance evaluation, we implemented an example system for such a combined performance evaluation consisting of a multiprocessor system-on-a-chip. It is based on existing models for simulation and analytical models extended by the needed interfaces for the combination, including an implementation of the simulation trace generation algorithm. This combined model was then used for a case study of an application running on a multiprocessor system.

- 2. A new evolutionary algorithm IBEA is presented that directly incorporates user preferences. Most popular evolutionary search algorithms incorporate methods to quickly find solutions close to the optimal solution (fast convergence), but also to keep diversity among the solutions. These methods are built-in and cannot be changed by the user. Our new algorithm is more generic in the sense that it allows the user to explicitly advise the algorithm what optimisation goal it should pursue. Furthermore, the new algorithm is easy to use, as it reduces the number of parameters that have to be set by a user compared to other existing black-box optimisation algorithms. This is achieved by an adaptive scaling such that the algorithm works independently of the objective values given to the algorithm. We discuss the performance of the new algorithm IBEA compared with many other state-of-the-art multi-objective optimisers on several test problems.

1.3. Overview 5

3. We present a generic software framework to perform design space exploration runs. Using the framework, only a few problem-specific parts have to be implemented to explore a certain design space, other parts can be reused. The tool implements the PISA interface such that many popular multi-objective optimisers can easily be reused without any implementation effort. Like this, the development time for a new design space exploration tool that matches a user's needs is shortened and the developers can concentrate on the problemspecific parts of the exploration tool. It offers the user a convenient graphical user interface and is completely written in Java. We used the framework for two example design space exploration problems, namely a cache optimisation example and for packet processor architectures. The former was used to introduce the framework and to discuss the main components of a design space exploration problem. The packet processor example is more involved and was used as benchmark application to evaluate the performance of different randomised search algorithms for a real-world application.

#### 1.3 Overview

In the following, we give an overview over the contents of this thesis:

- Chapter 2 gives an overview over the various topics that are involved in the process of design space exploration. We give a classification of existing approaches to design space exploration based on the abstraction level and the exploration method used.

- Chapter 3 covers performance evaluation methods for single design points in the space of possible designs. We investigate a formal method for system-level performance analysis, show how it can be adapted to be used for design space exploration. We then compare the formal method with a simulation-based approach and finally propose a new performance evaluation method that combines simulation with the formal method.

- Chapter 4 discusses the different search strategies that exist for multi-objective optimisation problems. Further we propose a new evolutionary algorithm that directly incorporates user preferences. The performance of the new search algorithm is compared to other established algorithms in a case study.

- Chapter 5 describes tools and applications of the work presented in the previous chapters. It gives an overview over the EXPO tool

framework, a generic framework for design space exploration that was used for several exploration problems presented in this thesis. Further, the tool was used as a benchmark problem for evolutionary algorithms and the results of a case study are also presented in this chapter.

• Chapter 6 concludes the thesis with an outlook for future research and a summary of the contributions.

# Design Space Exploration of Embedded Systems

Design space exploration is a central step in embedded system design [Ern98]. There may be many different design alternatives that implement a given system specification. These different implementations have to be explored and judged for their quality such that a designer can make a decision which system alternative to implement. Therefore, during the exploration phase, many design alternatives have to be evaluated. Design alternatives may consist of different hardware component allocations, different mappings of software tasks to resources, different scheduling policies implemented on shared resources as well as lower level design parameters such as clock frequency or bus widths.

In actual design flows presented by Marwedel in [Mar03], design space exploration can be found embedded into the design process. For example, in the SpecC design flow [GZD+00], design space exploration is performed after having an executable specification to find an appropriate allocation, partitioning and scheduling. After the exploration, in the SpecC design flow design validation is performed.

The IMEC tool flow also involves design space exploration at several stages as part of the design flow. During the exploration phase, the mapping of tasks to processors is optimised [WMY+01] as well as data transfer

and data storage [CdGS98].

Design space exploration is often a problem involving multiple criteria. The design alternatives normally represent a trade-off between different optimisation goals. For instance, if we consider cost and performance as optimisation goals, a processor that can run at higher clock speeds is usually more expensive.

In the following sections, we will introduce a simple example for design space exploration that will guide us through the remainder of this chapter, categorise existing approaches to design space exploration according to their abstraction layer, and cover the different aspects that play a role in the design space exploration process for embedded systems.

## 2.1 A Simple Example: Design Space Exploration of Cache Architectures

Before we describe the components needed for design space exploration in detail, let us consider a simple example application – the design of a cache subsystem – that will be used throughout the remainder of this chapter for illustration purposes. Note, that it is not the purpose of the example to present any new results in cache optimisation.

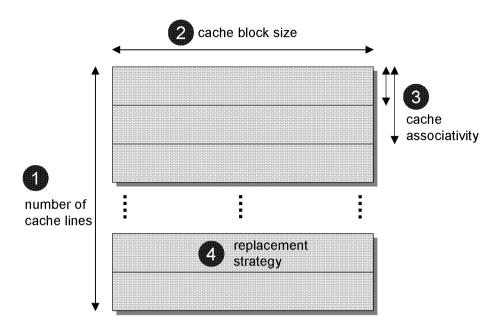

Suppose we want to optimise the architecture of a cache for a predefined benchmark application. Restricting ourselves to Level 1 data caches only, the design choices include the cache size, the associativity level, the block size, and the replacement strategy. The goal is to identify a cache architecture that (1) maximises the overall computing performance with respect to the benchmark under consideration and (2) minimises the chip area needed to implement the cache in silicon.

| Nr. | Parameter            | Range                             |

|-----|----------------------|-----------------------------------|

| 1   | # of cache lines     | $2^k$ , with $k = 6 \dots 14$     |

| 2   | Block size           | $2^k$ Bytes, with $k = 3 \dots 7$ |

| 3   | Associativity        | $2^{k}$ , with $k = 05$           |

| 4   | Replacement strategy | LRU or FIFO                       |

**Tab. 1:** Parameters determining a cache architecture.

In Table 1, all parameters and possible values for the cache architecture are given. A design point is therefore determined by three integer values and a Boolean value. The integers denote the number of cache lines, the cache block size and the cache associativity; the Boolean value encodes the replacement strategy: *false* denotes FIFO (first-in-first-out),

Fig. 2: Illustration of the considered design choices for an L1 data cache architecture.

true denotes LRU (least recently used). Figure 2 graphically depicts the design parameters. The values for the number of cache lines, block size and associativity have to be powers of 2, due to restrictions in the tools used for evaluation of the caches.

The first objective according to which the cache parameters are to be optimised is the CPI (cycles per instruction) achieved for a sample benchmark application, and the second objective is the chip area needed to implement the cache on silicon. To estimate the corresponding objective values, we used two tools, namely sim-outorder of SimpleScalar [BA97] and CACTI [SJ01] provided by Compaq. The first tool served to estimate the CPI for the benchmark compress95 running on the plain text version of the GNU public license as application workload. The smaller the CPI for compress95 for a particular solution, the better is this solution for this objective. The second tool calculated an estimate for the silicon area needed to implement the cache. The smaller the area, the better is the cache for the area objective.

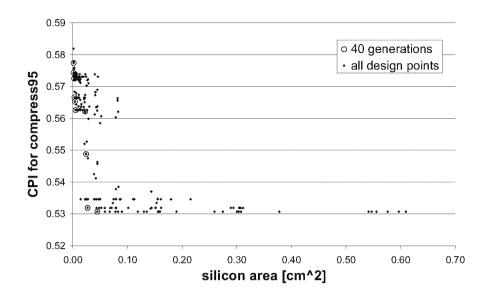

The cache subsystem design space exploration example was performed using the EXPO tool framework described in Chapter 5 of this thesis. We used the randomised search algorithm SPEA2 [ZLT02] to perform the optimisation.

The design space with all solutions is shown in Figure 3. These design points have been generated using exhaustive search in order to compare the heuristic search with the Pareto front of optimal solutions. The Pareto

**Fig. 3:** All 540 possible design points determined using exhaustive search and the design points found by the multi-objective search algorithm SPEA2 after 40 generations.

front denotes the set of solutions that are Pareto-optimal, i.e. the solutions that are not dominated by any other solution in the solution set. A solution A dominates another solution B, if A is at least as good as B in all criteria and strictly better in at least one criterion.

The front of non-dominated solutions found for the cache example with SPEA2 after a typical optimisation run with 40 generation for a population size of 6 solutions is marked with circles. The details of the solutions in the population after 40 generations are given in Table 2.

Although the cache design space exploration problem is simple in nature, one can make some observations which also hold for more involved exploration problems. The two objectives, namely the minimisation of the silicon area and the minimisation of the CPI, are conflicting, resulting in an area vs. performance trade-off. This results in the fact that there is not a single optimal solution, but a front of Pareto-optimal solutions. All points on this front represent different promising designs, leaving the final choice for the design of the cache up to the designer's preference.

The reduction of the problem to a single-objective optimisation problem, e.g., using a weighted-sum approach is difficult already for this simple example, because it represents a true multi-objective problem. It is not at all clear how to relate area to performance, which would be needed for the weighted-sum approach.

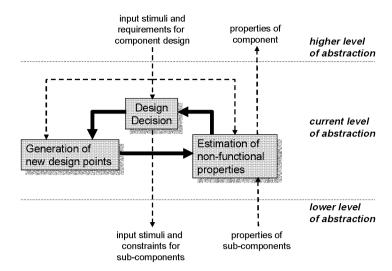

Figure 4 shows how the design space exploration is embedded into a

| No. | CPI    | Area     | Design Parameters |                             |               |         |

|-----|--------|----------|-------------------|-----------------------------|---------------|---------|

| 1   | 0.5774 | 0.001311 | LRU               | 2 <sup>7</sup> cache lines  | block size 8  | d. m.   |

| 2   | 0.5743 | 0.001362 | LRU               | 2 <sup>7</sup> cache lines  | block size 8  | 2 sets  |

| 3   | 0.5622 | 0.022509 | FIFO              | 2 <sup>8</sup> cache lines  | block size 64 | 8 sets  |

| 4   | 0.5725 | 0.002344 | LRU               | 2 <sup>7</sup> cache lines  | block size 16 | 2 sets  |

| 5   | 0.5488 | 0.024018 | LRU               | 2 <sup>10</sup> cache lines | block size 32 | 8 sets  |

| 6   | 0.5319 | 0.027122 | LRU               | 2 <sup>10</sup> cache lines | block size 32 | 16 sets |

| 7   | 0.5666 | 0.002898 | LRU               | 2 <sup>6</sup> cache lines  | block size 32 | 2 sets  |

| 8   | 0.5653 | 0.003629 | FIFO              | 2 <sup>6</sup> cache lines  | block size 64 | d. m.   |

| 9   | 0.5307 | 0.044902 | FIFO              | 2 <sup>10</sup> cache lines | block size 64 | 8 sets  |

| 10  | 0.5626 | 0.004907 | LRU               | 2 <sup>6</sup> cache lines  | block size 64 | 2 sets  |

**Tab. 2:** Details of 10 non-dominated solutions for the simple example of a cache exploration found after a typical design space exploration run. These solutions are marked with circles in Figure 3.

hierarchical design trajectory for embedded systems. If we consider our example to be on the current abstraction level, the evaluation of a solution leads to requirements for sub-components on the lower level, e.g. the area on silicon that is available for the implementation in our example. In addition, the evaluation provides properties of the component to the higher level of abstraction. The various abstraction layers for design space exploration are discussed in the next section. In the later sections, we use the cache example to introduce the building blocks for design space exploration.

## 2.2 Abstraction Layers in Design Space Exploration

There are many existing approaches that make use of an automated or semi-automated design space exploration in embedded systems design. Exploration of implementation alternatives happens at various levels of abstraction in the design. These various layers are described next and existing design space exploration approaches are classified accordingly:

Logic Design and High Level Synthesis: Here, one is concerned with

the synthesis of digital logic starting from either a register-transfer

specification or a more general imperative program. The manual design of dedicated computing units is also included. Typical design

choices concern speed vs. implementation area vs. energy consumption, see e.g. [BBB01, CSH00].

**Fig. 4:** Embedding of exploration in a hierarchical design trajectory for embedded systems.

- Programmable Architecture: The programmable architecture layer contains all aspects below the instruction set. For example, it contains the instruction set definition, the microprocessor architecture in terms of instruction level parallelism, the cache and memory structures. There are numerous examples of exploration on this level of abstraction; they concern different aspects such as caches and memories [GG03, SC99, SCK04], or the whole processor architecture, especially the functional unit selection [HHBS99, PSZ03, RCR04].

- Software Compilation: This layer comprises all ingredients of the software development process for a single task, such as code synthesis from a model-based design or a high-level program specification. Within the corresponding compiler, possible exploration tasks are code size vs. execution speed vs. energy consumption. There are attempts to perform a cross-layer exploration with the underlying processor architecture, see e.g. [ZTB00b, APS04].

- Task Level: On the task level, the whole application is partitioned into tasks and threads. Therefore, the task level refers to operating system issues like scheduling, memory management and arbitration of shared resources. Typical trade-offs in choosing the scheduling and arbitration methods are energy consumption vs. average case vs. worst case timing behaviour, see e.g. [BBTZ01].

- *Distributed Operation*: Finally, there exist applications that run on distributed resources. The corresponding layer contains the hard-

ware aspects of distributed operation (such as the design of communication networks) as well as methods of distributed scheduling and arbitration. On this level of abstraction, which is sometimes called system level, one is interested in the composition of the whole system that consists of various computing and communication resources. System-level design not only refers to the structure of the system, but also involves the mapping of application to the architecture and the necessary (distributed) scheduling and arbitration methods. This highest level of abstraction seems to be especially suited for exploration methods, see e.g. results on the communication infrastructure [LRD04, ETZ00], on distributed systems [ABD+04] or multiprocessor systems and systems-on-chip, e.g. [ARS98, GVNG98, GVH02, BTT98, TCGK02a].

The above approaches combine several important aspects such as the integration of the exploration into the whole design process, the specific estimation method used to evaluate the properties of design points and finally the method that is used to perform the actual exploration.

### 2.3 Design Evaluation

There are a lot of different criteria for which one could try to optimise an embedded system. Besides the "classic" non-functional properties, such as power consumption, silicon area or resource utilisation, the implementation cost or manufacturability are also examples for design criteria.

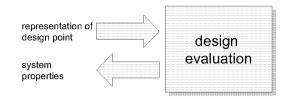

Common to all the criteria is the need for a tool to evaluate a design point in the design space. Based on the representation of the solution such a tool captures the quality of a design (cf. Figure 5). The quality of a property can normally be expressed using a number. In that case, two design points can be compared for this property and a designer can immediately see, which one of the two design points is better with respect to the design criterion in question, based on this number.

Dependent on the level of abstraction, the evaluation tools are based on formal methods, simulation or even measurements. One requirement for the design evaluation of a single design point in design space exploration is evaluation time. If the evaluation for a single design point takes too much time, the method is prohibitive for exploring a huge design space. Nevertheless, it may be possible to use the evaluation method in a later phase for a pruned design space.

Performance evaluation of embedded systems is covered in more detail in Chapter 3. A formal performance evaluation method is introduced and compared with an existing established performance evaluation

**Fig. 5:** A design evaluation method takes the representation of a design point as input and provides the system properties as output.

method, namely simulation. We show that in order to speed up the evaluation time, we can use approximations for the formal method. Further, we propose a new evaluation method that combines simulation-based approaches with analytical methods.

For the cache example introduced in Section 2.1 we use two different tools to assess the performance number for a given solution. On one hand side, we use SimpleScalar [BA97], an instruction set simulator to retrieve the cycles per instruction (CPI) for a benchmark application. The evaluation of the cache architecture for CPI is therefore based on simulation. On the other hand, to obtain the area in silicon needed to implement the cache we use CACTI [SJ01], a tool that is based on formal analysis.

### 2.4 Exploration Method

The existing approaches for design space exploration can also be classified in a way that is orthogonal to the abstraction layers, namely the methods that are applied to perform the exploration itself. This way it becomes apparent that the exploration process is largely independent of the abstraction level.

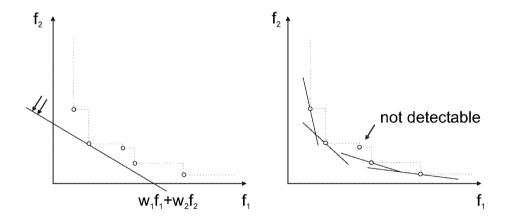

If only a single objective needs to be taken into account in optimisation, the design points are totally ordered by their objective value. Therefore, there is a single optimal design (if all have different objective values). The situation is different if multiple objectives are involved. In this case, design points are only partially ordered, i.e. there is a set of incomparable, optimal solutions. They reflect the trade-offs in the design. Optimality in this case is usually defined using the concept of Pareto-dominance: A design point dominates another one if it is equal or better in all criteria and strictly better in at least one. In a set of design points, those are called Pareto-optimal which are not dominated by any other. Using this notion, available approaches to the exploration of design spaces can be characterised as follows:

- 1. *Exploration by hand*: The selection of design points is done by the designer himself. The major focus is on efficient estimation of the selected designs, e.g. [GVNG98].

- 2. Exhaustive Search: All design points in a specified region of the design parameters are evaluated. Very often, this approach is combined with local optimisation in one or several design parameters in order to reduce the size of the design space, see e.g. [SC99, ZSXS03].

- 3. Reduction to a Single Objective: For design space exploration with multiple conflicting criteria, there are several approaches available that reduce the problem to a set of single criterion problems. To this end, manual or exhaustive sampling is done in one (or several) directions of the search space and a constraint optimisation, e.g. iterative improvement or analytic methods is done in the other, see e.g. [CSH00, GG03, LRD04, RCR04].

- 4. *Black-box Randomised Search*: The design space is sampled and searched via a black-box optimisation approach, i.e. new design points are generated based on the information gathered so far and by defining an appropriate neighbourhood function (variation operator). The properties of these new design points are estimated which increases the available information about the design space. Examples of sampling and search strategies used are Pareto Simulated Annealing [CJ98] and Pareto Tabu Search, e.g. [APS04, PSZ03], evolutionary multi-objective optimisation [ABD+04, BTT98, ETZ00, TCGK02b], or Monte Carlo methods improved by statistical estimation of bounds, e.g. [BBB01]. These black box optimisations are often combined with local search methods that optimise certain design parameters or structures, e.g. [BBTZ01].

- 5. *Problem-dependent Approaches*: In addition to the above classification, one can find also a close integration of the exploration with a problem-dependent characterisation of the design space. Several possibilities have been investigated so far:

- Use the parameter independence in order to prune the design space, e.g. [GVH02, PG02].

- Restrict the search to promising regions of design space, e.g. [HHBS99].

- Investigate the structure of the Pareto-optimal set of design points, for example using hierarchical composition of subcomponent exploration and filtering [ARS98, SCK04].

Explicitly model the design space, use an appropriate abstraction, derive a formal characterisation by symbolic techniques and use pruning techniques, e.g. [NSK02].

Finally, usually an exhaustive search or a black-box randomised search is carried out for those parts of the optimisation that are inaccessible for tailored techniques.

From the above classification, one can state that most of the above approaches use randomised search techniques one way or the other, at least for the solution of subproblems. This observation does not hold for the exploration by hand or the exhaustive search, but these methods are only feasible for small design spaces with a few choices of the design parameters. Even in case of a reduction to a single objective or in the case of problem-dependent approaches, sub-optimisation tasks need to be solved, either single objective or multi-objective and randomised (blackbox) search techniques are applied.

### 2.5 Summary

In this chapter, we introduced design space exploration as a central step in embedded system design. The main building blocks for a design space exploration are the problem specification, the design representation, the evaluation of a single design point and the exploration method. We revised existing approaches and classified them according to the abstraction layer and to the exploration method used.

Based on the concepts introduced in this chapter, the remainder of this thesis further investigates issues related to design space exploration. In the following, Chapter 3 is dedicated to performance evaluation of single design points. In Chapter 4, we will introduce evolutionary algorithms as exploration method. The performance of different algorithms is investigated and a new evolutionary algorithm is proposed. In Chapter 5, we present a tool framework for design space exploration and applications thereof.

# Design Evaluation

The evaluation of design points is one of the building blocks for design space exploration of embedded systems. There are many different properties of an embedded system a designer can be interested in. In [VG01], the authors present a long list of such potential design metrics, including power consumption, size, unit cost and performance for given applications.

In this chapter, we look at performance analysis techniques for embedded systems. First, we discuss existing approaches in Section 3.2. We then introduce Real-Time Calculus as formal method to assess performance numbers of a system in Section 3.3. Next, we briefly introduce simulation-based approaches for performance evaluation. These simulation-based approaches are then used for a comparative study with Real-Time Calculus.

After revising these existing approaches and discussing their use for design space exploration, we present the main results achieved in this work that are related to performance evaluation. Namely, we introduce a new approach to performance analysis, which combines Real-Time Calculus with a simulation-based approach in Section 3.6. Further, the necessary interfaces for this combination are described and we present a case study based on a multiprocessor platform. In the last section of this chapter, we look more carefully at the interface needed to couple Real-Time Calculus with simulation, and propose a generator for simulation traces that comply with a formal load specification.

Throughout this chapter, we use two example embedded systems. The

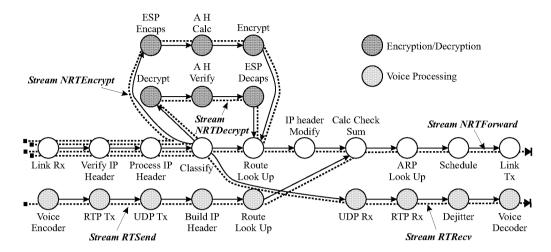

example system 1 is a hypothetical network processor architecture which is built around a PowerPC processor. The example system 2 consists of an architecture with multiple ARM cores connected through a parameterisable interconnection network. Both example systems were modelled with analytical techniques as well as for simulation and are introduced in the next section.

### 3.1 Example Systems

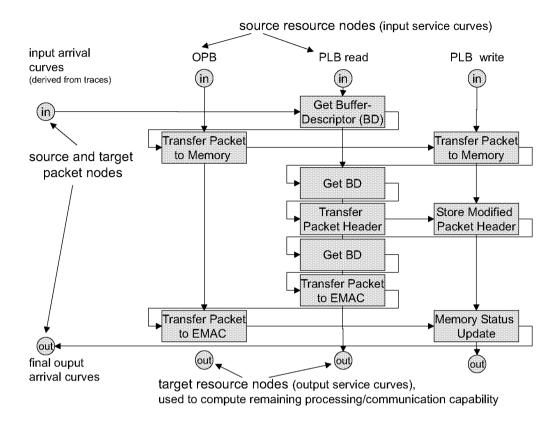

#### 3.1.1 Network Processor

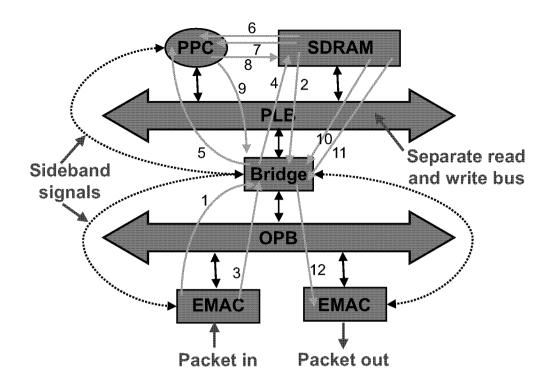

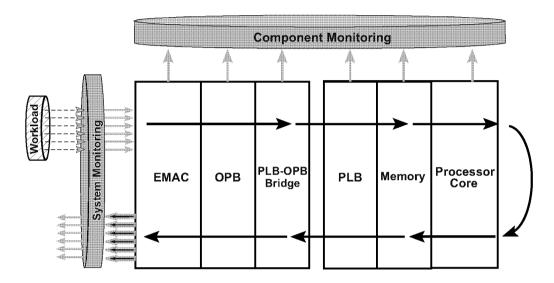

Figure 6 shows a hypothetical network processor architecture built out of blocks from an existing core library [IBMa, IBMb]. In the figure, PPC refers to the PowerPC 440 core, and PLB and OPB refer to two buses called the Processor Local Bus and the On-chip Peripheral Bus provided by the CoreConnect [IBMb] architecture for interconnecting cores and custom logic. For our example, we assume a simple network packet forwarding application running on this architecture. The numbers on the arrows in this figure either indicate actions that are to be performed by the different blocks as a packet flows through the architecture, and they are ordered according to the numbering. The system is described in more detail in [Wor01].

From Figure 6 it is possible to construct a task graph considering the appropriate packet transfers from one resource to another. This task graph together with a model for the hardware resources can then be used for formal analysis as we will see later in this chapter. With this analysis we can compute the load on the different buses (such as the OPB and the PLB), the on-chip memory requirement of this architecture to store the buffered packets in front of each resource, and the end-to-end packet delays.

#### 3.1.2 Multiprocessor Platform MPARM

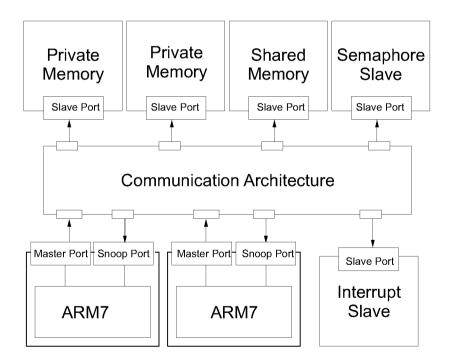

MPARM is a multi-processor virtual platform [LAB+04]. Its purpose is the system-level analysis of design tradeoffs in the usage of different processors, interconnects, memory hierarchies and other devices.

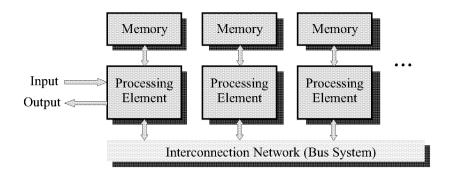

It consists of a parameterisable number of ARM7 processor cores and an AMBA interconnection network [AMB]. The platform includes several memory devices, which can be used as private or shared memories (cf. Figure 7).

For the examples presented in this chapter, we investigated 2 different applications running on this system architecture. First, we looked at a pipelined matrix multiplication application with 8 pipeline stages

**Fig. 6:** A system-level model of a network processor. The figure shows the path that a packet follows through the architecture. The numbers on the arrows indicate the different actions involved (which are explained in Table 3) while the packet travels through the architecture, and specify the order in which these actions are executed.

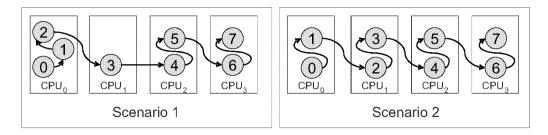

mapped on 4 processor cores. We investigated 2 different scenarios with a different mapping of the tasks to the computing resources as shown in Figure 8. In one mapping, we tried to balance the load among the processors, for the other mapping, the goal was to minimise the communication needed between the processors.

Second, we analysed a GSM encoder application mapped to 2 processors. The application was partitioned into 2 tasks and the tasks communicate through a FIFO queue located in the shared memory. This second example will be used for the case study of the new hybrid approach for performance analysis in Section 3.6.

### 3.2 Performance Analysis

Recently, many processing devices for embedded systems are designed as systems-on-chip (SoC) [Wol01]. Using this design paradigm, a complete

| Step | Action                                                         |

|------|----------------------------------------------------------------|

| 1    | Sideband signal from EMAC to bridge (indicating that a new     |

|      | packet has arrived)                                            |

| 2    | Bridge gets a "buffer descriptor" (BD) from the SDRAM          |

| 3    | Packet is sent from EMAC to bridge over the OPB                |

| 4    | Packet is sent from bridge to SDRAM over the PLB write bus     |

| 5    | Sideband signal from Bridge to PPC (indicating that the new    |

|      | packet has been stored)                                        |

| 6    | CPU get buffer descriptor over the PLB read bus                |

| 7    | CPU gets packet header over the PLB read bus                   |

| 8    | CPU processes header, and stores it back to SDRAM over the PLB |

|      | write bus                                                      |

| 9    | Sideband signal from bridge to CPU (indicating that the packet |

|      | can be sent out)                                               |

| 10   | Bridge gets buffer descriptor over the PLB read bus            |

| 11   | Bridge gets packet over the PLB read bus                       |

| 12   | Packet sent out to specified a EMAC over the OPB               |

**Tab. 3:** Sequence of actions for every processed packet in the architecture model shown in Figure 6.

Fig. 7: MPARM platform architecture.

**Fig. 8:** Mapping of the matrix multiplication tasks T0–T7 to the 4 processors for the two scenarios discussed in the example.

system consisting of computing, storage and communication resources is integrated on the same chip. Such a system may consist of several IP cores and dedicated hardware, as the Cell processor announced recently by Sony, IBM and Toshiba [PAB+05].

The complexity of these SoC designs, coupled with issues like short time-to-market and low cost, have led to new design paradigms such as platform-based design [KMN+00]. These are based on the concept of *reuse* at several levels of abstraction, where designers rely on the use of intellectual property blocks or cores from some library (such as the IBM Blue Logic Core Library [IBMa]), or on cores provided by a third-party vendor. Since such cores are already pre-designed and verified, a designer can now concentrate on the overall system rather than the individual components, and also reduce the number of steps required to translate a system-level design into a final product.

Analysing such system platforms to verify timing and other system properties pose a major challenge because they depend on the interfaces and properties (such as arbitration schemes on buses) of the different cores, and also on the RTOS and other components of the software platform. The problem gets aggravated in the context of embedded systems because of their generally heterogeneous architecture, where different scheduling and resource sharing strategies are used on the different buses and processors.

Performance evaluation of embedded systems can be broadly divided in two main areas: simulation-based approaches and formal methods. Most of the existing approaches rely on simulation (for example VCC [VCC] and Seamless [Sea]), and hence suffer from the problems of high running time, incomplete coverage and failure to identify corner cases. The last two problems are aggravated by the fact that in many cases system integrators do not have a full understanding of the functionality and the interfaces of the different cores, but only understand their high-level input/output behaviour. Therefore, if guarantees on system properties are

required then some form of static formal analysis is inevitable.

The trend for simulation-based performance analysis goes to full system simulation. Tools as Mentor Graphics' Seamless [Sea] support the co-simulation of complete hardware-software systems. In order to cope with the high simulation times caused by the increased complexity of the designed systems, simulation is used also on higher levels of abstraction in early design phases.

In [CB02] a modelling framework is presented which is composed of independent application, system and traffic models. The application is modelled using the Click modular router from MIT [KMC+00]. Click consists of a collection of software modules for describing various router functionality. Such modules in Click are called *elements*, and by putting together different elements in the form of a graph (which is called a *configuration*) it is possible to construct IP routers, firewalls, QoS routers, etc.

The framework in [CB02] is based on compiling Click modules for the Alpha ISA [Alp92]. The architecture to be evaluated is simulated using SimpleScalar [BA97] and it implements the Alpha instruction set. The compiled Click modules are then executed on this architecture. By simulating this execution using different traffic traces, the profiled code yields various information such as instruction count, details regarding cache behaviour, etc. These are then used to compute various performance metrics for the architecture being evaluated, related to packet latency, bandwidth and resource utilisation. For elements which do not have any software implementation (such as dedicated hardware units for header parsing) and can not be simulated, the profile and external dependencies need to be provided manually by the user.

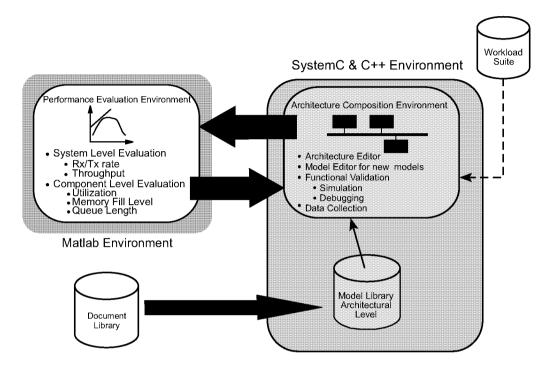

In contrast to this approach, the work done in [Wor01] models an architecture in SystemC [GLMS02]. This work mostly focuses on the communication subsystem and the memory organisation of an architecture. The models are then simulated on packet traces and performance metrics such as bus utilisation, memory fill levels, and packet delays are evaluated. This work forms the basis of the simulation results that we use in this chapter and further details on it are given in Section 3.4.

The MPSoC simulation platform described in [MAS+05] combines a cycle-accurate simulation of a parameterisable communication infrastructure with instruction set simulators for the processing elements and therefore represents a framework that allows us to simulate complete embedded systems consisting of software and hardware. In contrast to the approaches presented in [Wor01] and [CB02] this framework can be used to evaluate both communication and computation parts of an embedded system.

Besides the simulation-based performance evaluation methods, for-

mal methods are emerging that enable the analysis of whole systems using holistic [PEP05] and compositional approaches. In particular, the system can be analysed using models of the individual components that can be later composed to system models that capture the complete system [RJE03, HHJ+05].

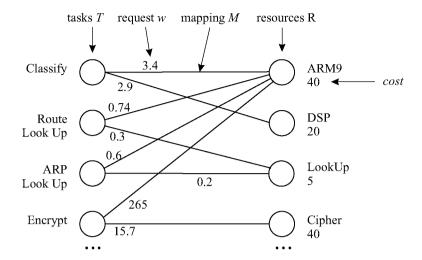

Especially for the domain of network processors, which is the application domain for the first example used in this chapter, an analytical performance model is considered in [FW02]. Here the different components that make up the architecture, and the interconnection among these components (the so called architecture template) is fixed. The design decisions that are to be made in deriving a concrete architecture from such a template, consist of choosing the values of the various parameters such as the bus width, cache sizes, etc. The architecture considered consist of a number of multi-threaded processors organised in clusters. Each cluster consists of a number of processors, each having its own cache, and the cluster communicates with an off-chip memory using its own memory interface. The parameters that can be changed are the number of threads running in each processor, the cache sizes, the number of processors in each cluster, the number of clusters in the network processor, the width of the memory channels, etc. For evaluating a set of parameters, an analytical model for multi-threaded processors proposed by Agarwal [Aga92] is used. Most of this work can be viewed as a model for the cache/memory subsystem of a network processor architecture. The analytical model is then evaluated on a benchmark workload [WF00] consisting of a mix of header-processing and payload-processing applications. For each application, properties such as load and store instruction frequencies and instruction and data cache miss rates are measured using processor and cache simulators. These values are then used to evaluate an architecture in terms of its processing power per unit chip area.

A general approach to timing analysis for heterogeneous systems was presented in [RE02] and [RZJE02]. It is based on identifying architectural components for which analysis methods are already known in the literature, and then combining these to obtain a compositional description of the complex system-level timing behaviour. The main contribution of this work is a method to adapt outgoing event streams from one component to match the input event model of another component which is required to process this outgoing stream. This gives a means for formally composing different architectural components and reasoning about the behaviour of the entire system.

The main drawback of this approach is that it can only accommodate standard event models like purely periodic, periodic with jitter, periodic with bursts, and sporadic. In practice, the event streams involved in a system usually do not conform to any of these standard models. But while

analysing such systems, these streams are approximated by some standard model which minimises the error. This introduces several modelling complexities, and when worst case bounds for a system are required, such approximations using standard event models give overly conservative bounds. These analytical methods are embedded into the SymTA/S tool, described in [HHJ+05].

The analytical model [TCGK02a, TCGK02b] that is discussed in more detail in Section 3.3 and used for the comparative study in Section 3.5 uses a model for both the architecture and the traffic traces on which the architecture is evaluated. In contrast to the work in [FW02] the architecture layout or the topology in this case is not fixed. Therefore, different combinations of processors, buses and their interconnection can be modelled and evaluated.

Actually, there is no sharp division into simulation-based approaches and formal methods for system-level analysis. There exist approaches that abstract communication internals in system simulation and use transaction-level modelling in SystemC [CG03]. Lahiri *et al.* present a combined approach to communication analysis which uses simulation for parameter extraction and then a formal method for fast performance analysis [LRD04]. Bobrek *et al.* also combine simulation with an analytical method in [BPN+04], with focus on the analysis of shared resource contention. They simulate parallel execution of threads and record accesses to shared resources, while a formal analysis model is then used to determine the adjustment of the timing caused by the shared resource contention.

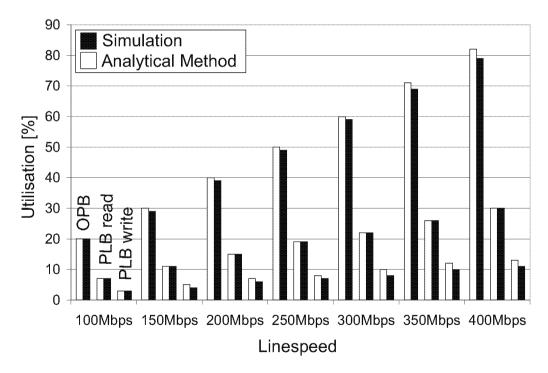

The formal methods used for design space exploration throughout this thesis is introduced in Section 3.3. In Section 3.4, we will revise existing simulation-based approaches that were used for the case studies presented in this thesis. Results obtained by these simulation-based approaches are compared with the results obtained by the system-level formal performance analysis model in Section 3.5. For a realistic network processor architecture, we consider performance metrics as the line speed or the end-to-end throughput that can be supported by the architecture, or the on-chip cache/memory requirement of the architecture. Finally, we present a new approach to performance analysis in Section 3.6 that is inspired by the idea of core-based design and represents a hybrid approach consisting of simulation-based and formal analysis components. The hybrid approach is applied in a case study for multiprocessor SoC performance evaluation. The automated way the interfaces between the different domains are provided makes this new approach also suitable for design space exploration.

# 3.3 Formal Performance Analysis

In this section, we introduce Real-Time Calculus as a framework for formal performance analysis of embedded systems.

# 3.3.1 Event Models and Resource Capabilities

We describe the event model which forms the basis of the formal performance analysis framework presented in this section and also a means of modelling the processing capability of resources which process event streams. It may be noted that in contrast to previous work on the performance evaluation of distributed embedded systems which relies on statistical bounds (see for example [KM98]) we are interested in analysing architectures and deriving worst-case bounds on system properties like response times, on-chip memory requirements and loads on various components. We also show how standard event models such as periodic or periodic with jitter can be represented by our event model.

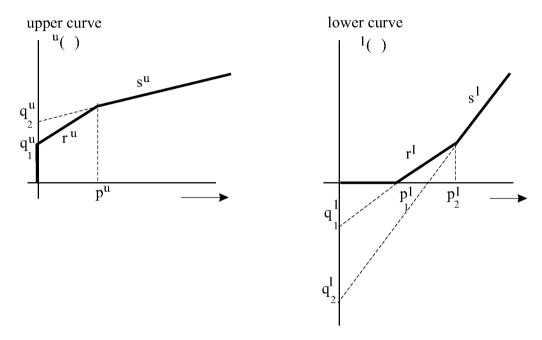

**Event models.** For a given event stream, let R(t) denote the number of events that arrive in the time interval [0, t]. Further, assume that the number of events arriving within any interval of time is bounded above by a right-continuous sub-additive function called the *upper arrival curve*, denoted by  $\alpha^u$ . Similarly, a lower bound on the number of events arriving is given by a *lower arrival curve*  $\alpha^l$ . R,  $\alpha^u$  and  $\alpha^l$  are related by the following inequality:

$$\alpha^{1}(t-s) \le R(t) - R(s) \le \alpha^{u}(t-s), \ \forall 0 \le s \le t$$

(3.1)

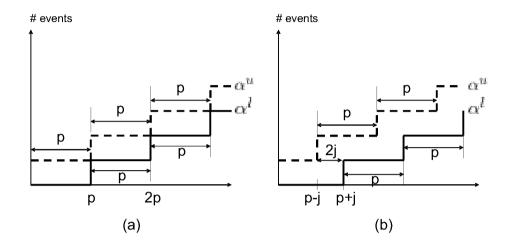

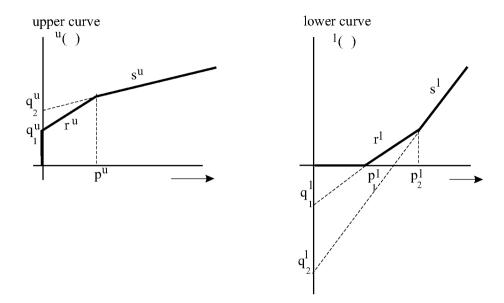

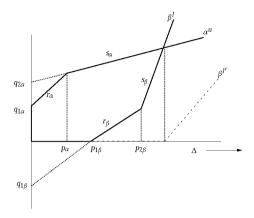

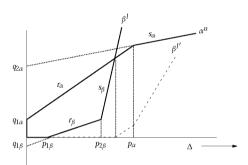

Therefore,  $\alpha^I(\Delta)$  and  $\alpha^u(\Delta)$  can be interpreted as the minimum and maximum number of events arriving within *any* time interval of length  $\Delta$ . Any standard event model can be represented in our model by an appropriate choice of  $\alpha^I$  and  $\alpha^u$ . For example, a periodic event stream with period p can be represented by an  $\alpha^I$  and  $\alpha^u$ , both of which are staircase functions of step width p and height 1, with  $\alpha^I(t) = 0$  for all t < p and  $\alpha^u(t) = 1$  for all t < p. This is because within any time interval of length less than p, the minimum number of events that can be seen is zero, and within any time interval of length  $p^+$ , the minimum number of events that can be seen is equal to one. Similarly, the maximum number of events that can be seen within any time interval of length p and  $p^+$  is one and two respectively. See Figure 9(a) for a graphical representation of the arrival curves for a periodic event stream.

Following the same reasoning, the class of event streams with period p and jitter j can be represented by an upper and a lower arrival curve of the form shown in Figure 9(b). Given any particular instance of such a periodic with jitter event stream, the corresponding upper and lower

arrival curves would lie within the arrival curves shown in Figure 9(b), and therefore these curves represent the upper and lower bounds on the maximum and minimum number of events that can arrive within any time interval for any event stream with period p and jitter j.

**Fig. 9:** (a) Upper and lower arrival curves describing a purely periodic event stream with period p. (b) Upper and lower arrival curves of the class of event streams with period p and jitter j.

At the same time, given any finite length arbitrary event trace and a real number  $\Delta$ , it is possible to determine the values of  $\alpha^l(\Delta)$  and  $\alpha^u(\Delta)$  corresponding to the event trace, by sliding a window of length  $\Delta$  over the trace and recording the minimum and maximum number of events lying within the window respectively. The upper and the lower arrival curves corresponding to the trace can be determined by following this procedure for different values of  $\Delta$ . The sliding window procedure is described in more detail in Section 3.6 and is used for the combination of the different approaches.

**Processing capability.** Similar to the upper and lower arrival curves, we use  $\beta^u$  and  $\beta^l$  to denote upper and lower *service curves* of a resource with the following interpretation. If C(t) denotes the number of processing units (might be in terms of processor cycles, time units, etc.) available from the resource over the time interval [0, t], then the following inequality holds.

$$\beta^{l}(t-s) \le C(t) - C(s) \le \beta^{u}(t-s), \ \forall 0 \le s \le t.$$

(3.2)

Hence,  $\beta^u(\Delta)$  and  $\beta^l(\Delta)$  give an upper and lower bound on the resource capability over any time interval of length  $\Delta$ .

There exist several possibilities to obtain the service curves describing a resource:

- They can be extracted from benchmark simulation runs, where simple workloads are processed by the resource.

- They can be obtained from data sheets describing the resource.

- They can be obtained from measurements of a real system.

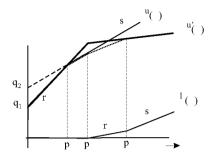

# 3.3.2 Analysing a Single Task

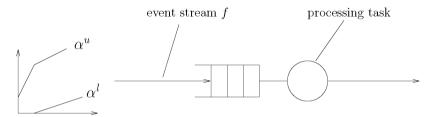

Assume the scenario from Figure 10. In this figure, a processing element is shown (circle on the right). It is associated with a buffer to store incoming events waiting to be processed. On the processing element a task that that has to be executed for each of the events is implemented. By this, the computing capabilities of the resource are being modified. Further, an event stream is given with the corresponding arrival curves denoting the worst-case bounds for event arrivals. These events are stored in the buffer if needed and processed by the processing element.

**Fig. 10:** Processing element executing a single task to process event stream f.

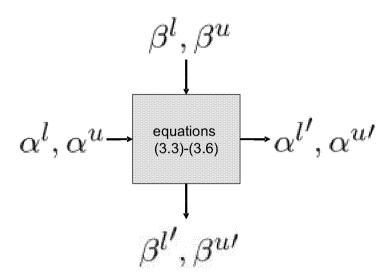

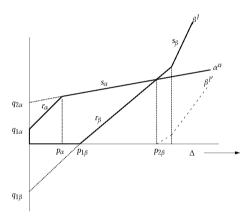

If we know the system from Figure 10, i.e. the upper and lower arrival curves  $\alpha^u$  and  $\alpha^l$ , and in addition know the processing element's computing capabilities described with service curves  $\beta^u$  and  $\beta^l$ , we can compute the description of the event stream after being processed. We can also compute the remaining service that can be offered by the resource after the event stream has been processed. We denote the event stream leaving the resource after being processed with arrival curves  $\alpha^{u'}$  and  $\alpha^{l'}$ . We also call these arrival curves "outgoing". Similarly, we denote the computing capabilities remaining in the resource with service curves  $\beta^{u'}$  and  $\beta^{l'}$ . Figure 11 gives a graphical representation for the curve processing. The curves can be related by the following expressions.

$$\alpha^{l'}(\Delta) = \min \{ \inf_{0 \le \mu \le \Delta} \{ \sup_{\lambda > 0} \{ \alpha^{l}(\mu + \lambda) - \beta^{u}(\lambda) \}$$

$$+ \beta^{l}(\Delta - \mu) \}, \beta^{l}(\Delta) \}$$

$$\alpha^{u'}(\Delta) = \min \{ \sup_{\lambda > 0} \{ \inf_{0 \le \mu < \lambda + \Delta} \{ \alpha^{u}(\mu) + \beta^{u}(\lambda + \Delta - \mu) \}$$

(3.3)

$$-\beta^{l}(\lambda)\}, \beta^{u}(\Delta)\} \tag{3.4}$$

$$\beta^{l'}(\Delta) = \sup_{0 \le \lambda \le \Delta} \{ \beta^{l}(\lambda) - \alpha^{u}(\lambda) \}$$

$$\beta^{u'}(\Delta) = \max\{ \inf_{\lambda > \Delta} \{ \beta^{u}(\lambda) - \alpha^{l}(\lambda) \}, 0 \}$$

(3.5)

$$\beta^{u'}(\Delta) = \max\{\inf_{\lambda > \Delta} \{\beta^{u}(\lambda) - \alpha^{l}(\lambda)\}, 0\}$$

(3.6)

Fig. 11: Simple processing node for arrival curves.

These results are based on generalising ideas from network calculus as applied to the domain of communication networks (see [BT01] for details), and hold specifically for infinite event streams that span over time  $t = -\infty$  to  $t = +\infty$ . Therefore, these are suited for modelling event streams such as periodic, sporadic, etc., which do not have any specific starting time (see also [CKT03a]). For modelling finite length event traces, the relations used in [TCGK02a, TCGK02b] may be used.

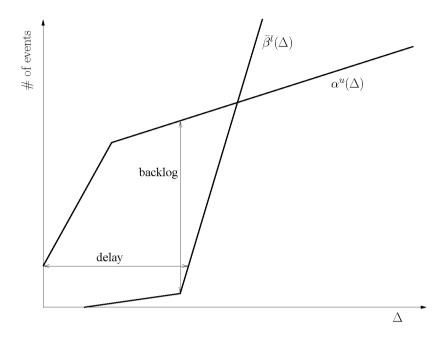

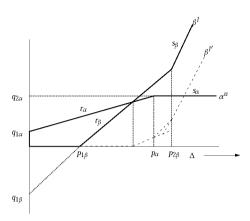

Moreover, it is not only possible to compute the outgoing event stream and the remaining resources for a given task, but also bounds on the delay experienced and backlog of unprocessed events. Assume  $\alpha^l$  and  $\alpha^u$  be the lower and upper arrival curves of an event stream entering a node whose input service curves are given by  $\beta^{l}$  and  $\beta^{u}$ . Then the maximum delay experienced by an event and the maximum number of backlogged events from the stream waiting to be processed can be given by the following inequalities.

$$delay \leq \sup_{t\geq 0} \left\{ \inf\{\tau \geq 0 : \alpha^{u}(t) \leq \beta^{l}(t+\tau)\} \right\}$$

$$backlog \leq \sup_{t\geq 0} \{\alpha^{u}(t) - \beta^{l}(t)\}$$

$$(3.7)$$

$$backlog \leq \sup_{t>0} \{\alpha^{u}(t) - \beta^{l}(t)\}$$

(3.8)

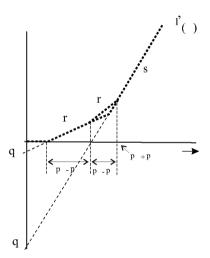

Fig. 12: Graphical representation of equations (3.7) and (3.8)

In Figure 12, a graphical interpretation of the Equations (3.7) and (3.8) is given. The maximum delay corresponds to the maximum horizontal distance between the upper arrival curve ( $\alpha^u$ ) and the lower service curve ( $\beta^l$ ), whereas the maximum backlog corresponds to the maximum vertical distance between the two curves. For a physical interpretation of these inequalities, we refer the reader to [BT01]. Lastly, if  $\beta^u$  and  $\beta^{l'}$  are the initial upper service curve and the lower remaining service curves of a resource, then its long-term utilisation in the worst case can be given by:

$$utilisation = \lim_{\Delta \to \infty} \frac{\beta^{u}(\Delta) - \beta^{l'}(\Delta)}{\beta^{u}(\Delta)}$$

(3.9)

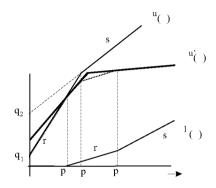

In order to apply the equations (3.3)–(3.6) we have to make sure that both, the arrival curves and the service curves use the same units. Often the arrival curves describe the minimum and maximum number of events in an interval  $\Delta$ , but the service curve give bounds on the number of processor cycles per time interval  $\Delta$ . In order to be able to correctly use the equations for remaining service and outgoing event stream, we have to scale the input curves accordingly.

For event event stream or packet flow f, let  $w_f$  be its worst-case per event processing requirement on the resource,  $b_f$  the best-case processing requirement. From now on, we will assume  $w_f$  and  $b_f$  to be defined in time units, i.e. the resource takes between  $b_f$  and  $w_f$  time units to process each

event of the stream f. To take these different processing requirements into account, we scale  $\bar{\alpha}^l_i$  and  $\bar{\alpha}^u_i$  appropriately before using Equations (3.3)–(3.6).  $\bar{\alpha}^l(\Delta)$  and  $\bar{\alpha}^u(\Delta)$  denote lower and upper event arrival curves, in other words, they give bounds on the number of events that can arrive in any interval  $\Delta$ . Hence we have,

$$\alpha^{u} = w_{f}\bar{\alpha}^{u}, \qquad \alpha^{l} = b_{f}\bar{\alpha}^{l} \tag{3.10}$$

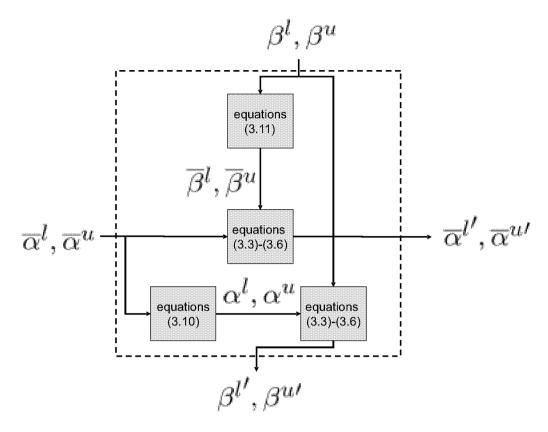

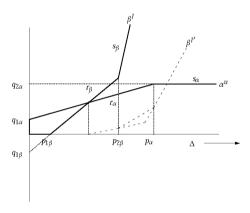

We scale the lower arrival curve with  $b_f$  — and not  $w_f$  or the average execution requirement — to ensure that the resulting, scaled arrival curve still represents a correct lower bound. Similarly, we scale the upper arrival curve with  $w_f$ . This procedure may introduce an error due to uncertainties caused by the variable execution requirement, but it is conservative and the resulting bounds are valid and safe. Using these scaled arrival curves, we can now compute the remaining service curves as shown in Figure 13.

The outgoing arrival curves representing the processed event stream can be computed using scaled service curves (as depicted in Figure 13):

$$\overline{\beta}^u = \lceil \beta^{u'}/b_f \rceil, \qquad \overline{\beta}^l = \lfloor \beta^{l'}/w_f \rfloor$$

(3.11)

In [MKT04] and [Max05], Maxiaguine *et al.* present workload curves, a further refinement of the scaling to reduce the error introduced and provide more accurate results. Workload curves capture variable execution times of tasks more accurately than just using best-case and worst-case execution times.

Now, we know how to calculate the outgoing event stream in form of arrival curves and the remaining resources in form of service curves, if we look at a single event stream for which a task has to be processed on a single resource. Next, we will look at the case, where multiple event streams have to be processed on the resource.

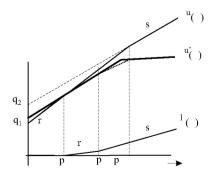

### 3.3.3 Multiple Streams on a Resource

If multiple event streams have to be processed by a resource, some sort of scheduling is necessarily involved. Scheduling means that some mechanism has to decide which event stream should be served at a certain point in time. In the next paragraphs we will have a closer look at a priority-based scheduling scheme.

Let us assume that there are n event streams entering a resource whose processing capability is bounded by the service curves  $\beta^l$  and  $\beta^u$ . Each event stream i is constrained by the arrival curves  $\bar{\alpha}_i^l$  and  $\bar{\alpha}_i^u$  and let the streams be ordered according to their priorities, i.e. stream 1 has the highest priority and stream n the lowest.

In the case of static priority scheduling, the resource processes the event streams in the order of decreasing priority, and the resulting arrival

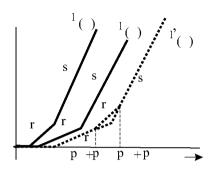

Fig. 13: Curve processing including scaling of arrival and service curves.

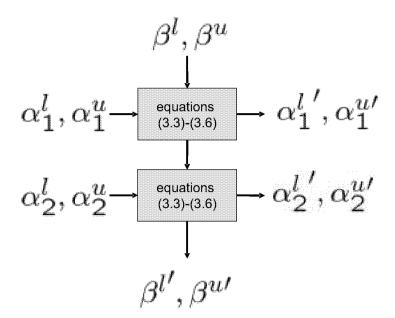

and service curves are computed using Equations (3.3)–(3.6). For the event stream 1, the service curves of the unloaded resource serve as an input. For the *i*th event stream, the input service curve is equal to the remaining service curve after processing the (i-1)th stream, for  $i \geq 2$ . This can be formally stated as follows:  $\beta_1^u = \beta^u$ ,  $\beta_1^l = \beta^l$ ,  $\beta_i^u = \beta_{i-1}^{u'}$ ,  $\beta_i^l = \beta_{i-1}^{l'}$ ,  $i = 2, \ldots, n$ , where  $\beta_{i-1}^{u'}$  and  $\beta_{i-1}^{l}$  for  $i = 2, \ldots, n$  are determined from  $\beta_{i-1}^{u}$ ,  $\beta_{i-1}^{l}$ ,  $\alpha_{i-1}^{u}$  and  $\alpha_{i-1}^{l}$  by applying Equations (3.5) and (3.6). Lastly, the remaining service curve after processing all the event streams is given as follows:  $\beta^{u'} = \beta_n^{u'}$ ,  $\beta^{l'} = \beta_n^{l'}$ . This can be used to process other event streams, possibly using a different scheduling discipline, in a hierarchical manner.

If other scheduling policies (such as EDF, GPS) or arbitration schemes in case of communication resources (such as TDMA) should be used, this results in a changed arrangement of the single processing nodes compared to the one shown for priority-based scheduling in Figure 14. Note that also the available service curves for the individual tasks may be changed. For further information about other scheduling policies to be used with Real-Time Calculus the reader is referred to e.g. [TW05],[TCGK02a].

Fig. 14: Curve processing for 2 event streams using a priority-based scheduling.

# 3.3.4 Complex Systems with Multiple Resources

In this section, we extend the analysis method to platform architectures containing more than one resource. An example for such an architecture is given in Figure 6. It describes an hypothetical example network processor architecture. The numbered arrows denote the sequence of steps that is performed by the architecture to forward a packet from one network interface to the other. The architecture is introduced in more detail in Section 3.3.6.

Event streams flow through a network of resources based on the order in which they need to be processed. From the arrival curves describing the input load to a resource, we can compute the outgoing arrival curves with Equations (3.3) and (3.4). The arrival curves of an outgoing event stream from a resource serve as input arrival curves to another resource. Similarly, the processing capability of a resource is reduced by the processing of the incoming event stream. The remaining processing capability, as captured in the outgoing upper and lower service curves is used to process other event streams.

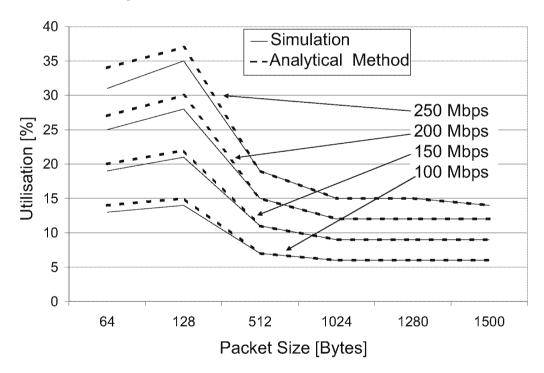

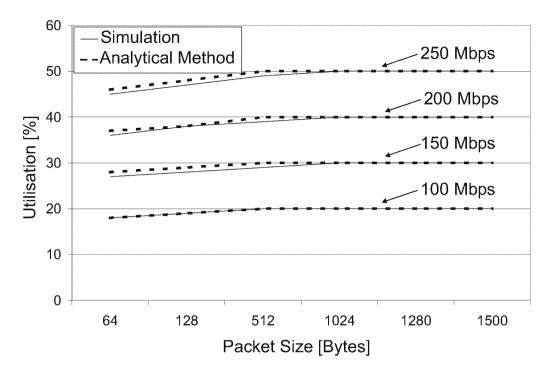

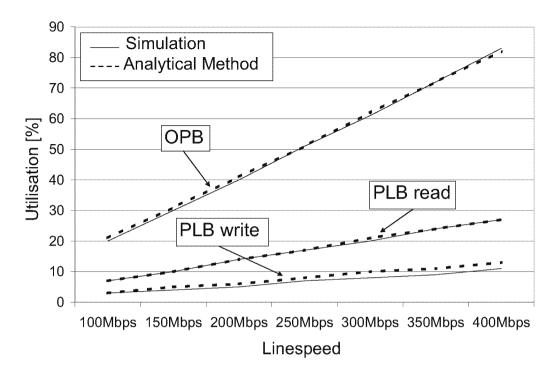

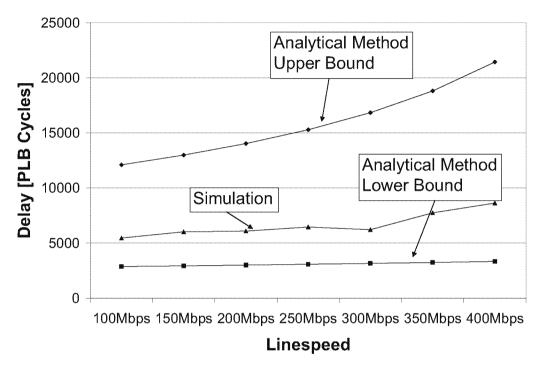

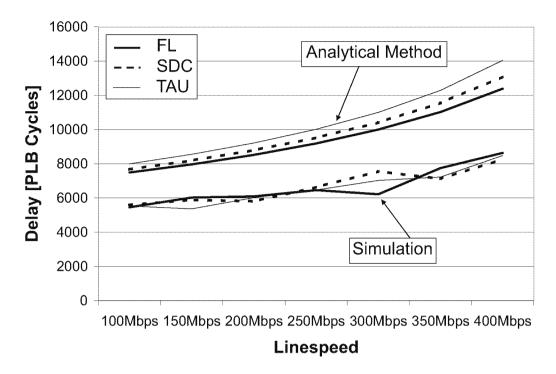

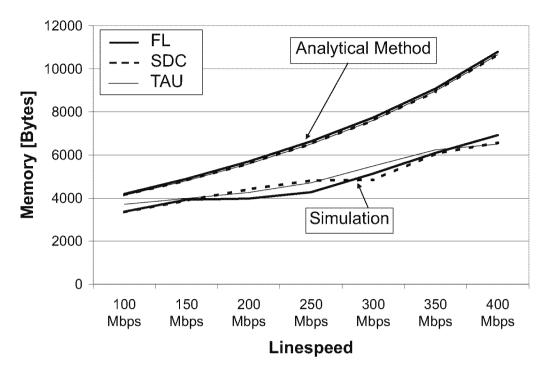

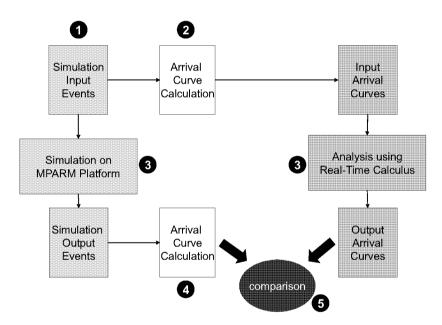

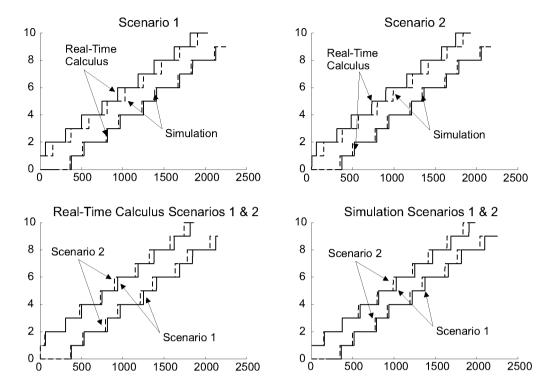

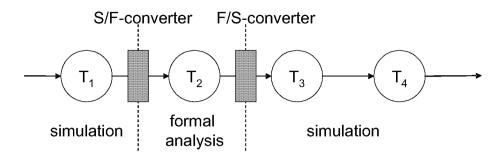

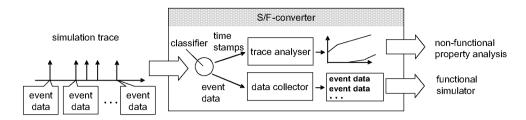

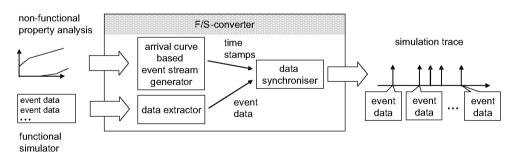

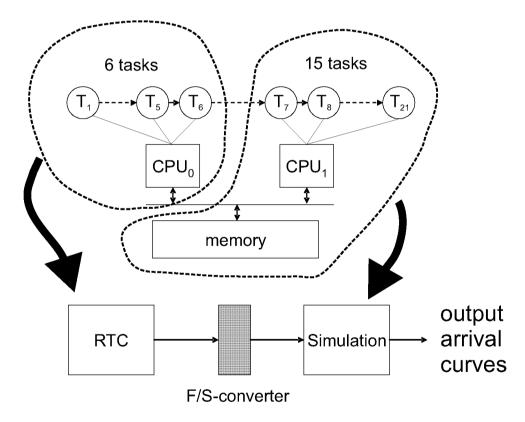

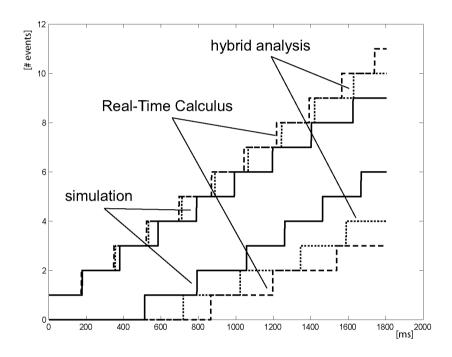

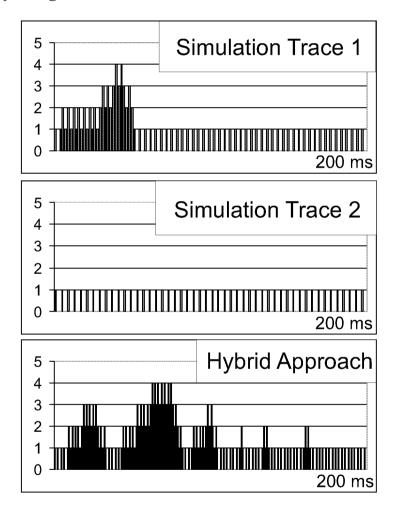

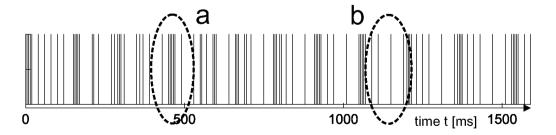

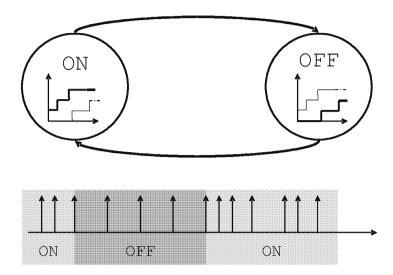

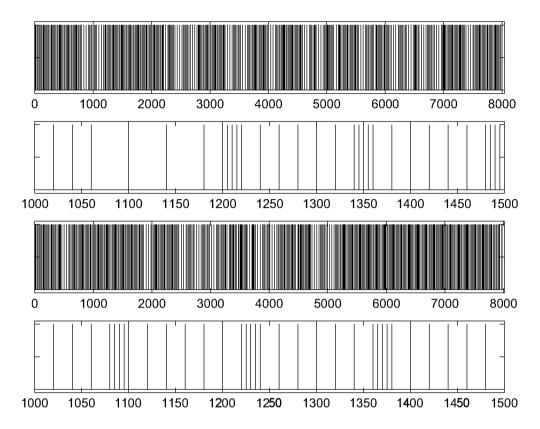

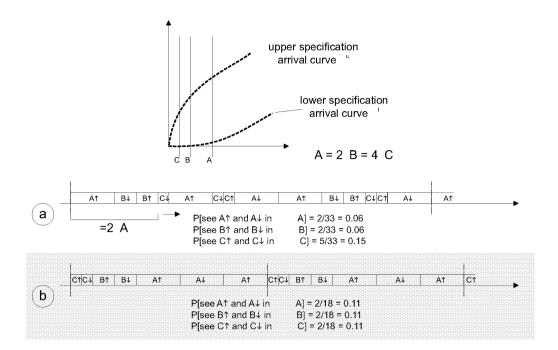

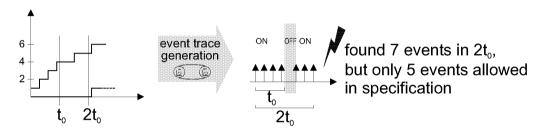

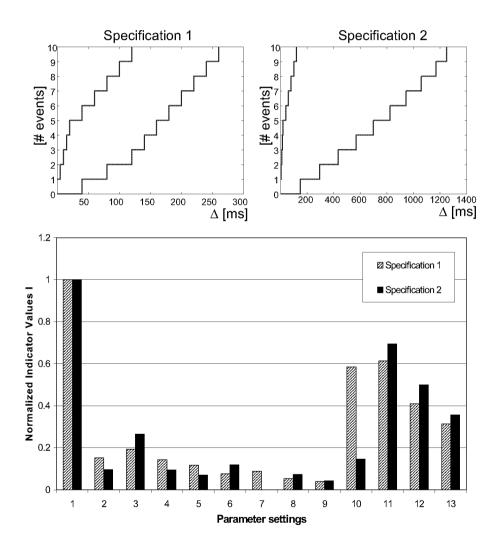

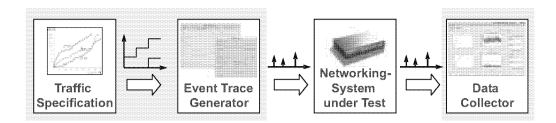

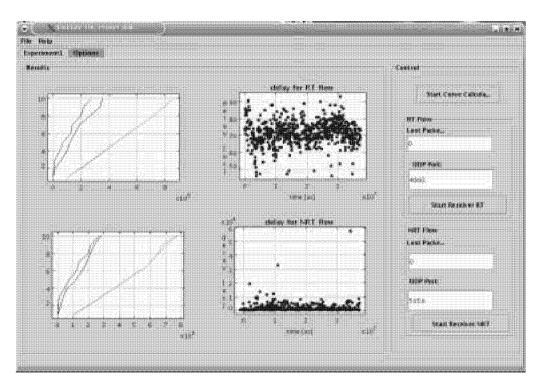

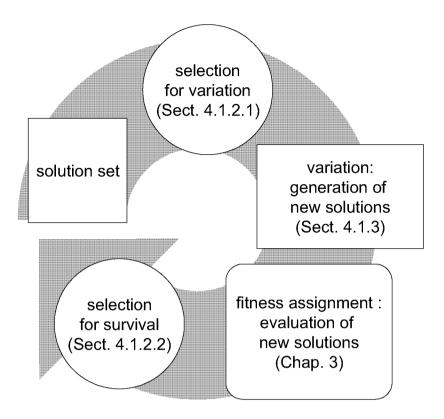

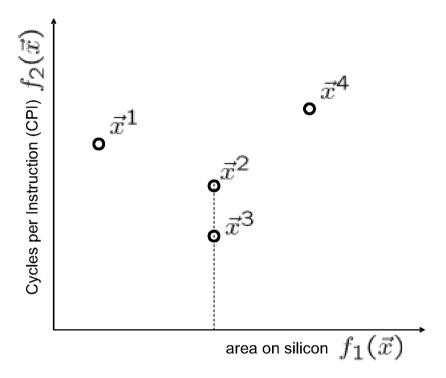

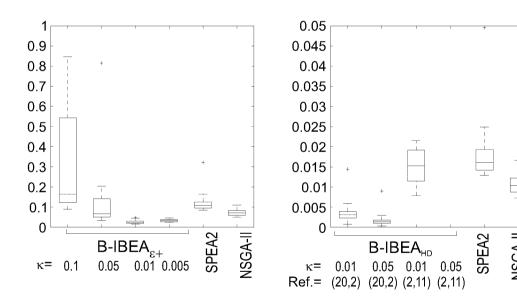

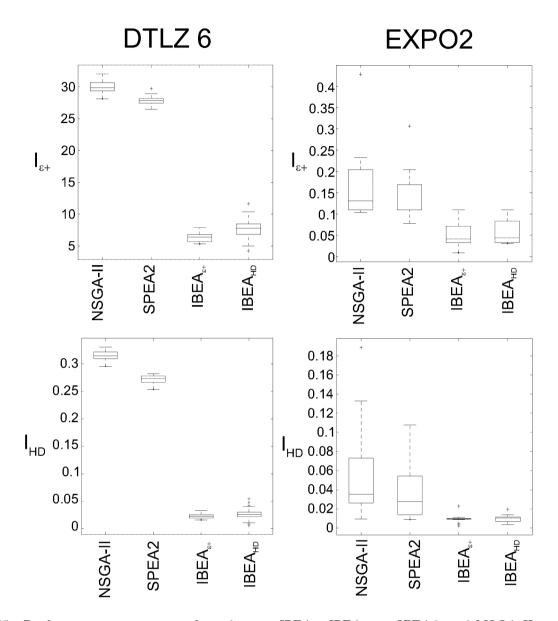

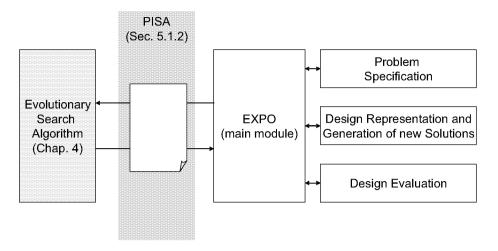

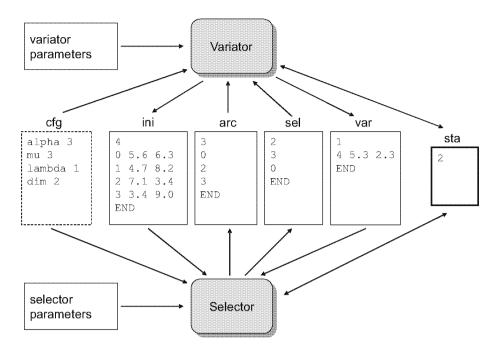

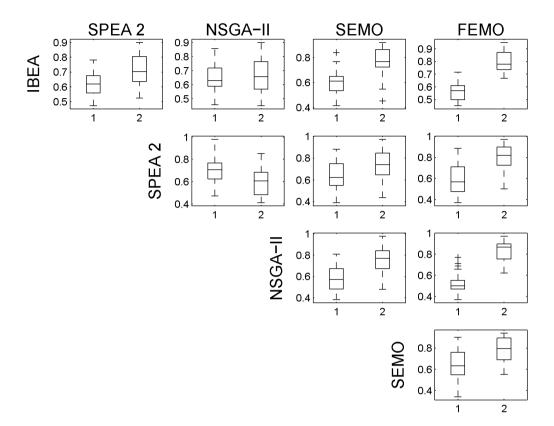

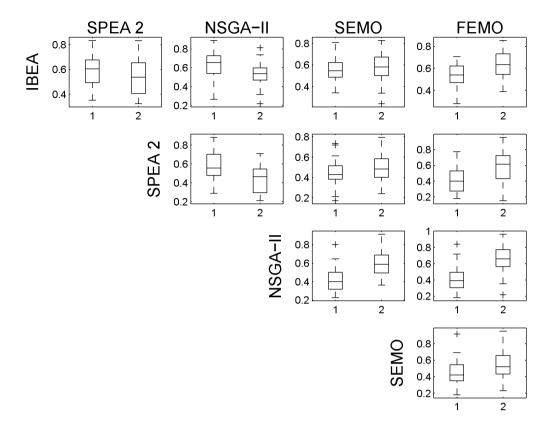

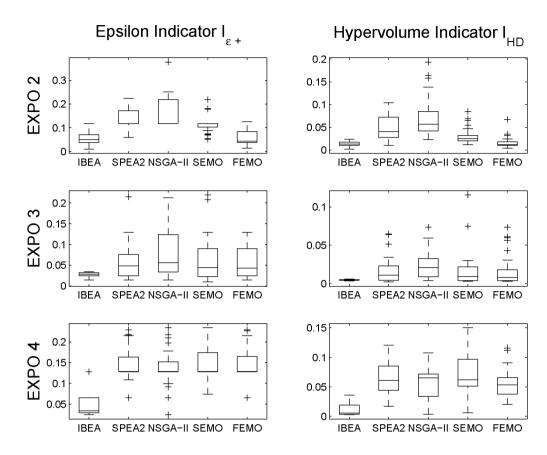

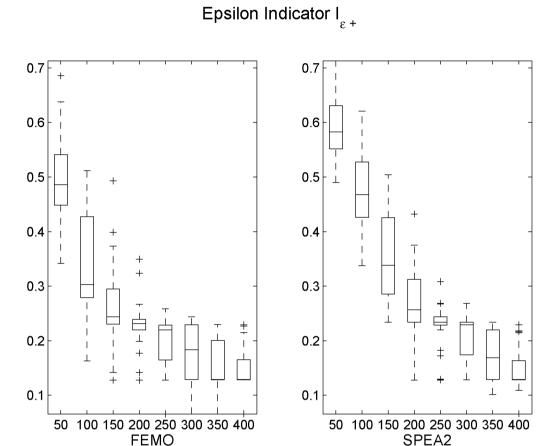

This model of an architecture can be represented as a *scheduling net-work*. The nodes of this network represent event processing functions that are implemented on the various resources. The inputs to each such node are the arrival curves of an event stream that is to be processed, and the service curve of the resource, representing the processing capability available to the function that is being implemented on the resource.