# DOL-BIP-Critical: a tool chain for rigorous design and implementation of mixed-criticality multi-core systems

# **Journal Article**

# Author(s):

Giannopoulou, Georgia; Poplavko, Peter; Socci, Dario; Huang, Pengcheng; Stoimenov, Nikolay; Bourgos, Paraskevas; Thiele, Lothar; Bozga, Marius; Bensalem, Saddek; Girbal, Sylvain; Faugere, Madeleine; Soulat, Romain; Dupont de Dinechin, Benoît

Publication date: 2018-06

Permanent link: https://doi.org/10.3929/ethz-b-000268885

Rights / license: In Copyright - Non-Commercial Use Permitted

Originally published in: Design Automation for Embedded Systems 22(1), <u>https://doi.org/10.1007/s10617-018-9206-3</u>

# **DOL-BIP-Critical:** a tool chain for rigorous design and implementation of mixed-criticality multi-core systems

Georgia Giannopoulou<sup>1</sup> · Peter Poplavko<sup>5</sup> · Dario Socci<sup>5</sup> · Pengcheng Huang<sup>1</sup> · Nikolay Stoimenov<sup>1</sup> · Paraskevas Bourgos<sup>6</sup> · Lothar Thiele<sup>1</sup> · Marius Bozga<sup>2</sup> · Saddek Bensalem<sup>2</sup> · Sylvain Girbal<sup>3</sup> · Madeleine Faugere<sup>3</sup> · Romain Soulat<sup>3</sup> · Benoît Dupont de Dinechin<sup>4</sup>

Received: 27 November 2015 / Accepted: 5 April 2018 / Published online: 2 June 2018 © Springer Science+Business Media, LLC, part of Springer Nature 2018

**Abstract** Mixed-criticality systems are promoted in industry due to their potential to reduce size, weight, power, and cost. Nonetheless, deploying mixed-criticality applications on commercial multi-core platforms remains a highly challenging problem. To name a few reasons:

Peter Poplavko, Dario Socci and Paraskevas Bourgos—Ex-employees of VERIMAG ("The presented research was performed while working at VERIMAG").

🖂 Georgia Giannopoulou georgia.gn@gmail.com Peter Poplavko petro.poplavko@siemens.com Dario Socci Dario Socci@mentor.com Pengcheng Huang pengcheng.huang@tik.ee.ethz.ch Nikolay Stoimenov nikolay.stoimenov@tik.ee.ethz.ch Paraskevas Bourgos bourgos@wings-ict-solutions.eu Lothar Thiele thiele@ethz.ch Marius Bozga marius.bozga@univ-grenoble-alpes.fr Saddek Bensalem saddek.bensalem@univ-grenoble-alpes.fr Sylvain Girbal sylvain.girbal@thalesgroup.com Madeleine Faugere madeleine.faugere@thalesgroup.com Romain Soulat romain.soulat@thalesgroup.com

Benoît Dupont de Dinechin benoit.dinechin@kalray.eu

(i) Industrial mixed-criticality applications are usually complex reactive applications, which cannot be specified by traditional, e.g., dataflow-based, models of computation. Appropriate mixed-criticality models of computation built upon Vestal's assumptions are missing; (ii) Scheduling such applications on multicores with shared resources, such as memory buses, requires that any timing interference among applications of different criticality is bounded in order to guarantee—the necessary for certification—temporal isolation and to enable incremental design; (iii) The implementation of isolation-preserving mixed-criticality schedulers is itself subject to certification. Hence, it needs to be not only efficient, but also provably correct. This paper proposes, for the first time, a complete design flow covering all aspects from specification, using a novel mixed-criticality aware model of computation (DOL-Critical), to correct-by-construction implementation, using the principle 'what you verify is what you generate' which is based on a novel variant of task automata. We demonstrate the applicability of our design flow with an industrial avionic test case on the state-of-the-art Kalray MPPA<sup>®</sup>-256.

**Keywords** Real-time systems · Mixed-criticality systems · Multi-core scheduling · Rigorous design · Software synthesis · Avionics

# **1** Introduction

With the proliferation of multi- and many-core platforms in the electronics market, the embedded system industry is experiencing an unprecedented trend towards integrating multiple applications into a common platform. The migration from single-core to multi-core designs affects even safety-critical domains, such as avionics and automotive. In such domains, applications are characterized by discrete safety criticality levels, as defined e.g., by the DO-178C avionics standard [16]. Integration of applications with different safety criticality has led to the design of so-called *mixed-criticality systems*, which has been a prominent research topic in recent years [11]. Nonetheless, a complete and sound methodology for successfully integrating mixed-criticality applications on (shared-memory) *multicores* remains by and large an open problem. Some of the challenges are listed below.

# 1.1 Motivation

# 1.1.1 Specification

Firstly, the specification of mixed-criticality (MC) applications does not usually fit into traditional streaming models of computation, such as Kahn process networks [35], for which established multi-core scheduling methods exist [57]. MC applications are often reactive control applications, where task activation depends on a combination of data availability (similar to streaming applications), complex (non-periodic) arrival patterns, and dynamic

<sup>&</sup>lt;sup>1</sup> Computer Engineering and Communication Networks Laboratory, ETH Zurich, 8092 Zurich, Switzerland

<sup>&</sup>lt;sup>2</sup> CNRS, VERIMAG, Univ. Grenoble-Alpes, 38000 Grenoble, France

<sup>&</sup>lt;sup>3</sup> THALES Research and Technology, 91767 Palaiseau Cedex, France

<sup>&</sup>lt;sup>4</sup> Kalray S.A., 38330 Montbonnot Saint Martin, France

<sup>&</sup>lt;sup>5</sup> Mentor, A Siemens Business, F-38334 Inovallee, Montbonnot, France

<sup>&</sup>lt;sup>6</sup> WINGS ICT Solutions PC, 189 Syggrou Avenue, 17121 Athens, Greece

decisions by schedulers which can skip tasks or activate them in degraded mode. As a result, the MC scheduling models widely used in the literature, like Vestal's [64], miss any link to application-level specifications, which calls for new models of computation for the precise representation of real-world MC applications.

#### 1.1.2 Temporal isolation

Secondly, mixed-criticality design needs to ensure temporal isolation for certification purposes. Namely, applications of different safety criticality levels should not interfere (delay each other), or their interference must be bounded according to safety standards. To achieve isolation on a single core, system designers usually rely on time partitioning mechanisms at platform level, such as the ones specified by the ARINC-653 standard [6]. In contrast to partitioning, in research literature it is commonly assumed that the isolation property is ensured in a non-symmetric way, for efficiency. That is, the interference from lower to higher criticality tasks is eliminated or bounded, but the interference from higher to lower tasks is tolerated. The established MC scheduling model of Vestal [64] represents tasks with multiple worstcase execution time (WCET) bounds at different safety criticality levels. The bounds become more conservative and more probable as the criticality level increases. Most scheduling policies based on this model execute all tasks initially according to their least conservative WCET bounds, and can change the schedule dynamically at runtime if high criticality tasks require more resources (execution time). After the schedule switch, lower criticality tasks may receive less or no service. Inhibiting those tasks prevents unwanted interference to high criticality tasks and improves resource efficiency. This way, non-symmetric isolation is ensured on single cores. However, on multicores one has to consider possible interferences among tasks with different criticality on additional (non-computational) shared platform resources, e.g., shared caches or memory buses. Preserving isolation in the presence of shared resources is not trivial [39]. It requires new industrial specifications, like [6], and an extension of Vestal's original MC model to account for the accessing behavior to shared resources. Existing multicore scheduling solutions often neglect this source of interference or assume that it has a bounded effect on the individual tasks' execution times [8,15,37,40,44,46,53]. On the contrary, we identify a state-of-the-art approach that preserves temporal isolation [24], and we offer a new rigorous and flexible implementation methodology for it.

#### 1.1.3 Incremental design

Thirdly, due to the high cost of certification, industry poses the requirement for incremental design of MC systems [7]. A MC scheduling policy should support adding new applications to a system without any impact on the schedule or the real-time properties of higher criticality applications that already existed in the system design. This removes the need for re-certification every time a new application is integrated, thus reducing the overall cost. Industrial standards, such as [6], specify mechanisms for incremental design that are restricted to single cores and symmetric isolation. New incremental design methodologies have to take into consideration non-symmetric isolation and interference of shared resources on multicores. This requirement has received, nonetheless, minimal attention in literature. The implementation methodology proposed in this paper targets at incremental design.

#### 1.1.4 Implementation

Fourthly, the implementation of both MC applications and their supporting mechanisms, such as schedulers and mechanisms for temporal isolation, is itself subject to certification.

Given that such mechanisms can include inter-core synchronisation, distributed monitoring of task execution times, dynamic schedule reconfigurations, resource servers, a manual implementation can be challenging and error-prone. Additionally, the runtime overhead of the supporting mechanisms is non-negligible and must be considered at design time for a safe deployment [54]. These challenges call for rigorous approaches for the implementation and validation of MC schedulers and the correct-by-construction MC software synthesis. Implementation paradigms for timing-critical multi-core applications, such as [27], show promising results. However, even though they are rigorous, they are not flexible, i.e., they are restricted to a particular model of computation and hardware architecture.

# **1.2 Contributions**

In this paper we present a complete design flow for mixed-criticality multi-core systems, which addresses all aforementioned challenges. The main contributions can be summarized as follows:

- We apply Vestal's model for MC task sets [64] so as to account, besides WCET, also for shared-resource accesses at different criticality levels, for degraded mode of lowcriticality tasks, and for incremental design.

- We extend Vestal's model further to a complete model of computation, with inter-task dependencies and communication requirements. This model is expressed in an architecture description language (ADL), DOL-Critical, which enables the specification of MC applications and schedules complying with the above extensions. This way we demonstrate the new elements that can be potentially included in popular ADLs, such as AADL, to account for mixed-criticality and multi-core designs.

- We present an optimization tool for isolation-preserving multi-core scheduling of MC applications which are specified in DOL-Critical. The optimization tool is integrated with response time analysis that considers task interference on shared resources, and it aims at incremental design. Thus, we propose a method that can handle our Vestal's model extensions in practice.

- For rigorous system design, we extend the timed-automata language BIP [1] to support asynchronous transitions, thus obtaining an enhanced variant of task automata [4,21]. As a result, we extend the scope of automata as design languages from synchronous to general real-time systems. Traditionally used only for verifying these systems, the automata can now be used to directly express multi-core applications and custom scheduling policies, which leads to the concept '*what you verify is what you generate*' (WYVIWYG). We demonstrate this concept by compiling the DOL-Critical applications and schedules into BIP automata and then performing functional validation and code generation.

- We implement a generator from BIP to hardware-dependent software (HdS). The synthesized code preserves the automata semantics up to a bounded clock drift caused by runtime overhead, e.g., thread synchronization. Although in a custom implementation the overhead may potentially be smaller, an automata-based implementation makes the overhead amenable for systematic formal analysis due to the formal automata semantics.

- We integrate all tools, from application specification in DOL-Critical to system modeling in BIP to code generation, into a single tool-chain.

- We show how to integrate runtime overheads characterized after the deployment of the MC application on the target platform back into the optimization tool, reusing its facility to model the shared resources. For this, we introduce a feedback loop in our flow.

- We demonstrate the applicability and utility of our design flow with an avionic test case targeting the Kalray MPPA<sup>®</sup>-256 platform.

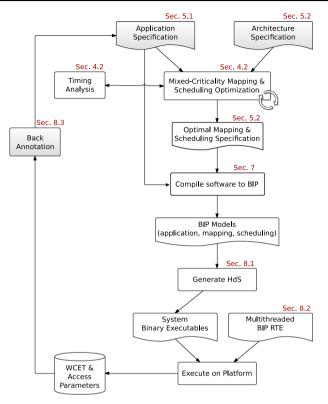

Fig. 1 DOL-BIP-Critical design flow

To the best of our knowledge, this is the first seamlessly integrated tool-chain for the specification, scheduling optimization, timing analysis, and correct-by-construction implementation of MC applications on commercial-off-the-shelf multi-core platforms. Note that the model of computation and the respective ADL, the enhanced task automata, the compilation of MC system specifications from ADL into automata for subsequent code generation, and the formal runtime overhead model that is integrated into schedule optimization are presented for the first time in this paper.

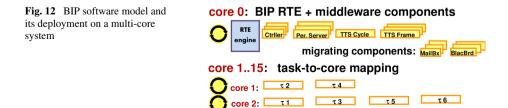

#### 1.3 Flow overview

The combined DOL-BIP-Critical design flow, which follows the established Y-chart approach [36], is illustrated in Fig. 1. The document shapes represent data (specifications of application, architecture, mapping in DOL-Critical, BIP models, executable code) and the rectangular shapes represent tools, respectively. The highlighted parts of the flow are user-defined. Namely, the MC application and the target architecture are specified by the system designer. All other steps of the design flow are executed automatically, except for the back annotation of the application specification, which is performed by the system designer after the execution of the MC application on the architecture. The front- and the back-end of the tool-chain are publicly available under [17,49], respectively.

# 1.4 Outline

In the remainder of the paper, Sect. 2 discusses related work. Section 3 presents the extensions to Vestal's MC model for resource-sharing multicores and defines the requirements for MC schedulability. Section 4 describes a scheduling policy that explicitly considers the effects of resource sharing and ensures temporal isolation, along with an approach for optimizing MC scheduling w.r.t. incremental design. Section 5 starts the description of the tool-chain of Fig. 1 by presenting the DOL-Critical language for specifying applications, architectures and schedules. Section 6 presents the enhanced task automata language BIP. Sections 7 and 8 discuss the compilation of an MC application and its optimized schedule into BIP and the deployment of the BIP system representation on the target platform, along with the feedback loop from execution to timing analysis (scheduling optimization). Section 9 demonstrates the developed design flow with an avionic test case and Sect. 10 concludes the article.

# 2 Related work

# 2.1 Mixed-criticality scheduling models

Scheduling of mixed-criticality (MC) systems has received increasing attention since the original work [64], which introduced the currently dominating model. This model represents MC tasks as periodic (sporadic) real-time tasks with multiple worst-case execution times (WCET), defined at different safety criticality levels. Vestal's model has been applied and extended in several works, [8,19,20,33,41,46] to name a few. For an up-to-date compilation and review of the model extensions and relevant scheduling policies, the interested readers are referred to [11]. In this work, we apply Vestal's model extensions to (i) capture shared-resource accesses, besides WCET, at different criticality levels, (ii) define the degraded mode of lower criticality tasks, and (iii) ensure incremental design.

# 2.2 Temporal isolation

Although several policies have been suggested for single-core MC systems, fewer solutions exist currently for multicores. One of the main challenges in multicores is satisfying the requirement for *temporal isolation* (or *freedom from interference*), which is dictated by industrial certification standards [16,34]. Since multicores typically feature different types of shared hardware resources, MC scheduling has to explicitly eliminate or bound potential timing interferences on all shared resources. For this purpose, several works advocate the static scheduling or per-core budget assignment on memory buses [22,59,70], the implementation of novel criticality-aware memory controllers [26,28,45], the privatization of memory banks by cores running single-criticality applications [51,67,69], or the use of virtualization and monitoring mechanisms for isolation among flows of different criticality on a network-on-chip [62]. Such methods allow bounding the effect of resource sharing on the response time of high-criticality applications. However, most of them lack flexibility (e.g., static time-triggered bus scheduling) and/or need special hardware support which limits their applicability to commercial-off-the-shelf platforms.

System-level solutions that target at global temporal isolation via scheduling have been also proposed recently. Anderson et al. proposed scheduling MC systems by employing different strategies (partitioned EDF, global EDF, cyclic executive) for different criticality levels and utilizing a bandwidth reservation server for isolation [5,44]. This work considers

mainly the CPU cores as shared resources, but no other platform resources where mixedcriticality applications can interfere. To overcome this limitation, the authors of [12,24] propose scheduling MC applications such that only tasks of the same criticality can be executed, and hence interfere on shared platform resources, at any time. Huang et al. formalise this notion under the term Isolation Scheduling and provide optimality results in [32]. In this paper, we employ policies for Isolation Scheduling of MC systems in order to facilitate their deployment on commercial-off-the-shelf platforms without dedicated hardware support. Particularly, we adopt the flexible time-triggered scheduling policy of [24] because (i) it complies with the MC model of Sect. 3, (ii) its dynamic runtime behavior allows efficient resource utilization (Sect. 4), (iii) it enables incremental design, and (iv) timing analysis methods which explicitly consider the effects of timing interference on shared resources are available [25].

#### 2.3 Implementation of mixed-criticality systems

The current industrial practice for implementing MC systems on single-core platforms enforces temporal isolation by means of operating system and hardware-level *partition-ing* mechanisms, e.g., as specified in the ARINC-653 standard [6]. No existing standards, however, define how isolation is preserved on resource-sharing multicores. Hence to the best of our knowledge, commercial multicores are not used currently for MC deployments in large-scale industrial applications. This highlights the vast need for tools and methodologies for the implementation of multi-core MC systems.

In research, implementation aspects of MC scheduling have started being addressed recently. Herman et al. [29] consider the implementation and runtime overhead of multicore MC scheduling, where the scheduling method of [5,44] is implemented in the real-time operating system LITMUS [13]. This policy does not preserve isolation in the presence of shared platform resources. Huang et al. [30] develop a framework, where several singlecore MC policies are implemented on top of a standard Linux kernel, and their runtime overheads are evaluated on an Intel Core i7 platform. Sigrist et al. [54] compare alternative implementations of common multi-core MC mechanisms on top of Linux, and evaluate their overheads on an 4-core Intel Core i5 and a 60-core Xeon Phi. Among others, they consider the overheads of the flexible time-triggered scheduling policy of [24], which is considered in our paper, and show that the implementation overheads can have a tremendous effect on schedulability, hence cannot be neglected. This shows clearly the challenge of implementing multi-core MC systems; rigorous methods are necessary for their scheduling, software synthesis, and timing analysis. This paper achieves a major step in this direction by presenting the first complete design flow for the implementation of isolation-preserving MC systems on commercial multi-core platforms, with explicit consideration of runtime overheads.

#### 2.4 Rigorous design methods

Rigorous design of timing-critical systems should employ models which possess formal operational semantics and capture the notion of physical time [65]. A relevant class of such models are timed automata, i.e., finite automata with continuous-time clock variables [3]. A literature overview [65] on applying timed automata in real-time systems reveals a large number of tools and a solid mathematical basis. An important extension of the timed automata are *timed automata with tasks*, also known as *task automata* [21]. These models can express and measure the time segments of their execution during which tasks are running. Timed and particularly task automata have many applications in timing analysis and code synthesis, an important example being the task-automata analysis and implementation tool TIMES [4].

Still, timed/task automata alone cannot satisfy all modeling needs, for two reasons. Firstly, they are often not convenient for programmers. Therefore, compilation from high-level languages, such as UML, to timed automata becomes a common practice, see e.g., [68]. Secondly, large timed automata suffer from analysis scalability issues. Therefore, for timing-critical system design it may be favorable to employ less expressive, yet better scalable models. Examples are (i) the AADL-based design flow TASTE [48], which employs tools for classical schedulability analysis, and (ii) the design flow CompSoC [27], which employs formal throughput analysis of dataflow graphs.

In this work, we introduce DOL-Critical as a high-level description language and a model of computation for specifying MC applications and multi-core scheduling solutions. The DOL-Critical specifications are fully automatically compiled to an enhanced variant of the BIP language for timed automata [1]. Our rationale for compilation to automata is to reuse their known ability to formally express runtime resource management mechanisms, especially in mixed-criticality settings [55], and to obtain a rigorous methodology for analyzing the runtime overheads. We perform code synthesis for both the application and runtime scheduling directly from the BIP task automata model. To enhance the scalability of timing analysis, we currently rely on a customized high-level analyzer which verifies the system both prior to and after (via a feedback loop) the compilation into BIP automata. We expect that the formal DOL-BIP relation established at compilation can be used to construct, in future work, a formal proof that the analysis can safely bound the runtime overheads.

DOL-Critical is based upon the distributed operation layer (DOL) [31,60]. A compilation framework from the original DOL to untimed automata in BIP was introduced in [9]. Unlike [9], in our tool-chain, the compilation target automata are timed. Moreover, we enhance the automata to represent real-time tasks and scheduling policies (including MC) explicitly, in a way that they form a homogeneous monolithic system with formal timingaware semantics that can be validated and synthesized as HdS code for a target platform. We refer to this facility as *what you verify is what you generate* (WYVIWYG). This has led to an essential redefinition of the synergy between DOL and BIP in particular and between ADL and formal-semantics models in general.

# 3 System model

This section defines the abstract application and architecture models<sup>1</sup> that are considered in our work as well as the necessary conditions for mixed-criticality schedulability. The application model is based on established assumptions from literature, which are extended to support resource sharing, degraded mode, dependencies, and non-blocking communication, while the architecture model is inspired by commercial many-core architectures. The schedulability conditions represent state-of-the-art methods of capturing temporal isolation and incremental design.

#### 3.1 Mixed-criticality application model

We consider mixed-criticality task sets  $\tau = {\tau_1, ..., \tau_n}$  with criticality levels between 1 (the lowest) and *L* (the highest). The tasks can be periodic or sporadic. A *periodic* task is characterized by a 4-tuple  $\tau_i = {W_i, \chi_i, C_i, C_{i,deg}}$ , where:

<sup>&</sup>lt;sup>1</sup> These models are used in our tool-chain for timing analysis (Sect. 4.2). The concrete class of applications and targets architectures that can be specified in DOL-Critical is described in Sect. 5.

- $-W_i \in \mathbb{N}^+$  is the task's period.

- $-\chi_i \in \{1, \ldots, L\}$  is the task's criticality level.

- $\mathbf{C}_i$  is a size-*L* vector of execution profiles, where  $C_i(\ell) = (e_i^{min}(\ell), e_i^{max}(\ell), \mu_i^{min}(\ell), \mu_i^{max}(\ell))$  represents a lower and an upper bound on the execution time  $(e_i)$  and the number of shared resource accesses  $(\mu_i)$  of  $\tau_i$  at level  $\ell \leq \chi_i$ . Note that execution time  $e_i$  denotes the computation or CPU time of  $\tau_i$ , without considering the time spent on accessing shared resources. Such decoupling of the execution and communication time is feasible on fully timing compositional platforms [66].

- $C_{i,deg}$  is a special execution profile that can be employed at runtime if a task  $\tau_j$  ( $\chi_j > 1$ ) consumes more resources than  $C_j(\ell')$  for some  $\ell'$  in  $\{1, \ldots, \chi_j 1\}$ . In Vestal's model, in this case it is legal to drop all subsequent jobs of tasks  $\tau_i$  with  $\chi_i \leq \ell'$  in order to free resources for the more critical task  $\tau_j$ . In this work, for compliance with industrial standards, we do not drop tasks, but instead execute them in *degraded mode*, which is characterized by profile  $C_{i,deg}$ . This corresponds to the minimum required functionality of  $\tau_i$  so that no catastrophic effect occurs in the system. If execution of  $\tau_i$  can be aborted without catastrophic effects, then  $C_{i,deg} = (0, 0, 0, 0)$ .

A *sporadic* task is characterized by a 5-tuple  $\tau_i = \{a_i, I_i, \chi_i, C_i, C_{i,deg}\}$ , with the new parameters  $(a_i \in \mathbb{N}^+, I_i \in \mathbb{N}^+)$  denoting the maximum allowed number of task activations,  $a_i$ , within any time interval  $I_i$ .<sup>2</sup> For scheduling purposes, a sporadic task is over-approximated by a periodic "server" task that has a sufficiently high execution frequency and tighter deadline to meet the deadlines of the sporadic task that it represents, see e.g., [50].

Periodic and sporadic tasks generate an infinite amount of jobs respecting the corresponding period or task activation per interval parameters. For simplicity, we assume that the first job of all periodic tasks is activated at time 0 and that the relative deadline  $D_i$  of  $\tau_i$  is equal to its period, i.e.,  $D_i = W_i$ . Furthermore, the worst-case parameters of  $C_i(\ell)$  are monotonically increasing for increasing  $\ell$  and the best-case parameters are monotonically decreasing, respectively. Namely, the min/max range of execution times and shared resource accesses in  $C_i(\ell)$  is included in the corresponding range of  $C_i(\ell + 1)$ , for  $\ell \in \{1, ..., \chi_i - 1\}$ . Note that the best-case parameters are only required for a tighter response time analysis. If not available, they are assumed equal to 0.

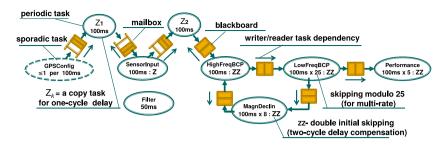

*Example 1* For illustration purposes, Table 1 presents the system model for our case study, a flight management system (FMS), which is discussed in more detail in Sect. 9.1 and is used as a running example throughout the paper. The FMS is a dual-criticality system, i.e., L = 2. The second column contains the criticality level  $\chi_i \in \{1, 2\}$  of each FMS task  $\tau_i$ . The period  $W_i$  of the sporadic task 'GPSConfig' is in fact its interval  $I_i$ , and  $a_i = 1$ . As the table shows, for high-criticality tasks ( $\chi_i = 2$ ), the level-1 worst-case execution time (WCET),  $e_i^{max}(1)$ , is lower than the respective level-2 WCET,  $e_i^{max}(1)$ . Therefore, in the 'emergency' situation where the level-1 WCETs turn out to be insufficient, the high-criticality tasks are eligible to continue their execution up to their level-2 WCET. For low-criticality tasks ( $\chi_i = 1$ ), e.g., 'Filter', the situation is reverse. In the case of 'emergency' (after high-criticality tasks overrun their level-1 WCET), the low-criticality tasks may receive a smaller execution budget than their 'normal' level-1 WCET, in order to free up resources for high-criticality tasks. In Table 1, for convenience, we specify this budget as 'level-2 WCET',  $e_i^{max}(2)$ . In fact, this budget corresponds to the degraded execution profile  $C_{i,deg}$  of low-criticality tasks, i.e.,  $e_i^{max}(2) = e_{i,deg}^{max}$ , if  $\chi_i = 1$ . The resource access counts,  $\mu_i^{max}$ , which are the same at all levels, in this example, are shown in the last column. The term 'RTE' describes a shared

<sup>&</sup>lt;sup>2</sup> Conventional sporadic tasks assume  $a_i = 1$ .

| Task $\tau_i$ | Criticality level<br><i>Xi</i> | Туре     | Period $W_i$ (ms) |    |    | RTE access count $\mu_i^{max}(1), \mu_i^{max}(2)$ |

|---------------|--------------------------------|----------|-------------------|----|----|---------------------------------------------------|

| Filter        | 1                              | Periodic | 50                | 32 | 2  | 3                                                 |

| SensorInput   | 2                              | Periodic | 100               | 1  | 26 | 3                                                 |

| GPSConfig     | 2                              | Sporadic | 100               | 1  | 21 | 4                                                 |

| HighFreqBCP   | 2                              | Periodic | 100               | 1  | 11 | 3                                                 |

| LowFreqBCP    | 2                              | Periodic | 100               | 1  | 11 | 3                                                 |

| MagnDeclin    | 2                              | Periodic | 100               | 1  | 11 | 3                                                 |

| Performance   | 2                              | Periodic | 100               | 1  | 11 | 3                                                 |

| Z1            | 2                              | Periodic | 100               | 1  | 26 | 3                                                 |

| Z2            | 2                              | Periodic | 100               | 1  | 26 | 3                                                 |

| Cycle_Begin   | 2                              | Periodic | 100               | 0  | 0  | 10                                                |

| Frame_Begin   | 2                              | Periodic | 50                | 0  | 0  | 4                                                 |

| Subframe_Bar  | 1                              | Periodic | 50                | 0  | 0  | 2                                                 |

Table 1 System model example: FMS application

resource and will be clarified later, in Sect. 8.3. All best-case parameters,  $e_i^{min}$  and  $\mu_i^{min}$ ,  $\forall \tau_i \in \tau$ , are considered zero and hence, omitted in the table.

The bounds for the execution times and accesses can be obtained by different tools. For instance, at the lowest level of assurance ( $\ell = 1$ ), the system designer may extract them by profiling and measurement, as in [47]. At higher levels, certification authorities may use static analysis tools, such as the abstract interpretation suite aIT [2], with more and more conservative assumptions as the required confidence increases. The execution profile  $C_i(\ell)$  for each task  $\tau_i$  is derived only for  $\ell \leq \chi_i$ . For  $\ell > \chi_i$ , there is no valid execution profile since certification at level  $\ell$  ignores all tasks with a lower criticality level. At runtime, if a task with criticality level greater than  $\chi_i$  requires more resources than initially expected, then  $\tau_i$  may run in degraded mode with execution profile  $C_{i,deg}$ . Note that we forbid the case where a task  $\tau_i$  consumes more resources than its own criticality level profile  $C_i(\chi_i)$ .

*Dependencies* can be defined between tasks with equal periods. We represent these by a directed acyclic graph  $Dep(\mathcal{V}, \mathcal{E})$ , where each node  $\tau_i \in \mathcal{V}$  represents a task, and an edge  $e \in \mathcal{E}$  from  $\tau_i$  to  $\tau_k$  implies that within a period the job of  $\tau_i$  must precede that of  $\tau_k$ . The dependencies between the FMS tasks of Example 1 will be defined later on.

Our *DOL-Critical model of computation* (MoC) extends the above system model by defining an inter-task communication method realized by means of shared objects, which are called *data channels*. The channels are written and read by tasks in a *non-blocking* fashion. The nonblocking communication is selected to avoid (potentially unbounded) blocking delays, and hence to facilitate scheduling, timing analysis and certification of mixed-criticality systems. Instead of blocking, we use dependencies to ensure functionally deterministic communication. Two tasks (of equal or different criticality levels) that communicate should have a dependency between them, going in the same or in the opposite direction as the flow of data. Recall that, in our model, a dependency implies equal periods. Therefore, to let two differentperiod tasks communicate, we transform them into equal-period tasks with a common-divisor period and internal skipping of excess activations. The DOL-Critical MoC is further discussed in Sect. 5.1. The MC model described above extends Vestal's model [64] by: (i) Introducing the shared resource access bounds, which are required for timing analysis on shared-resource multicores; (ii) Defining the degraded mode for lower criticality tasks. Guaranteeing a minimal functionality for such tasks (instead of dropping them as in the original model) has been also advocated in [10,52,58]; (iii) Introducing a consistent MoC where applications, such as the flight management system of Example 1, can be programmed.

#### 3.2 Shared-resource multi-core architecture model

We consider a set  $\mathcal{P}$  of *m* processing cores,  $\mathcal{P} = \{p_1, \dots, p_m\}$ . Here, the cores are identical but our approach can be generalized to heterogeneous platforms. The mapping of a task set  $\tau$  to the cores in  $\mathcal{P}$  is defined by function  $\mathcal{M}_{\tau} : \tau \to \mathcal{P}$ . In our work,  $\mathcal{M}_{\tau}$  is *not* given, but it is calculated by our optimization approach in Sect. 4.2.

Each core in  $\mathcal{P}$  has access to a private cache memory and to a shared general-purpose memory. The code and data of the tasks in  $\tau$  as well as the data channels used for the inter-task communications are assumed to fit in the shared memory. This abstract model gives a partial view of commercial many-core platforms, for instance the Kalray MPPA<sup>®</sup>-256 [14] and the STHorm/P2012 [42]. These platforms are on-chip networks of shared-memory clusters, with 16 cores per cluster. Currently, our model is restricted to a single cluster, since exploiting more on-chip clusters would require network-on-chip management, which is outside the scope of this paper.

For timing analysis, we need to consider shared resources which are accessed synchronously, namely which cause execution on the cores to stall until any pending access requests are served. We assume that such resources, for instance a memory bus, can be accessed by only one core at a time, and that once granted, a resource access is completed within a fixed time interval,  $T_{acc}$ . Access to the shared resources can be arbitrated according to any event- or time-triggered scheme, e.g., round-robin or time-division-multiple-access. To enable safe timing analysis under resource contention, we consider hardware platforms without timing anomalies, such as the fully timing compositional architecture defined in [66], where execution and communication times can be decoupled. Note that the MPPA<sup>®</sup>-256 cores have been shown to be fully timing compositional [14].

# 3.3 Mixed-criticality schedulability conditions

Under the above system assumptions, we seek a *feasible* schedule for the MC task set  $\tau$  on the cores  $\mathcal{P}$ , which enables *temporal isolation* among criticality levels and *incremental design*. Below we define the properties of feasibility, isolation and incremental design. The feasibility conditions follow from Vestal's schedulability conditions, by considering shared resource accesses and degraded mode. The isolation and incremental design conditions are introduced to capture the certification-induced requirements in safety-critical domains.

**Definition 1** (*Execution Scenario*) At runtime, the tasks follow a *level-l scenario* in a given time interval if, within this interval, the resource demand for all executing jobs of tasks  $\tau_i$  with criticality  $\chi_i \ge \ell$  complies with the execution and access bounds of profiles  $C_i(\ell)$ . If  $\ell > 1$ , there must be at least one job of a task  $\tau_j$ , for which the resource demand violates the bounds of  $C_j(\ell - 1)$ .

The term *resource*, in this context, refers to both processing time and shared-resource access. Initially, during a sufficiently small time interval, the tasks follow a level-1 scenario. When we extend this interval, the first job of a task  $\tau_j$ , whose resource demand exceeds  $C_j(1)$ , switches the current scenario to level 2. Later, a job of the same or another task  $\tau_{j'}$ , whose resource demand exceeds  $C_{j'}(2)$ , switches to level 3, and so on. The currently assumed scenario level (as well as the reference interval) is regularly reset back to level 1 at specific – for the given policy – time instances, when all cores and shared resources should be idle.

**Definition 2** (*Feasibility*) A schedule is *feasible* if for any level- $\ell$  scenario ( $\ell \in \{1, ..., L\}$ ), it guarantees the conditions:

- the jobs of each task  $\tau_i$ , satisfying  $\chi_i \ge \ell$ , receive enough resources between their activation time and deadline to meet their real-time requirements according to execution profile  $C_i(\ell)$ ,

- the jobs of each task  $\tau_i$ , satisfying  $\chi_i < \ell$ , receive enough resources between their activation time and deadline to meet their real-time requirements according to execution profile  $C_{i,deg}$ .

*Example 2* For the FMS application of Example 1, if a high-criticality task from the upper part of Table 1 exceeds its  $e_i^{max}(1) = 1$  ms, then the tasks switch from a level-1 to a level-2 scenario. If only the level-1 scenario was possible ( $e_i^{max}(1)$  was never exceeded), all tasks could easily meet their deadlines while executing on a single core, even if we assume that RTE accesses add a reasonably small overhead.<sup>3</sup> However, due to the large level-2 WCETs,  $e_i^{max}(2)$ , of high-criticality tasks, multiple cores are required for a feasible schedule even when the low-criticality tasks run in degraded mode. Note that when running on multiple cores, the tasks will experience *interference* upon simultaneous RTE accesses.

**Definition 3** (*Temporal Isolation*) A schedule satisfies non-symmetric *temporal isolation* if all tasks of criticality level  $\ell$  suffer no interference from tasks with lower criticality level, for all  $\ell \in \{1, ..., L\}$ . Namely, the execution and access activities of a task  $\tau_i$  do not delay in any way any task with criticality level higher than  $\chi_i$ .

**Definition 4** (*Incremental Design*) A scheduling algorithm enables *incremental design* if adding new tasks of lower criticality into the system can be done without altering the schedule for the existing tasks.

Note that the property of incremental design is based upon non-symmetric temporal isolation. The two properties imply that if the schedule of a task set  $\tau$  is certified as feasible, the certification procedure will not need to be repeated if new, lower-criticality tasks are added later to the system. This is highly desirable, since repeating the certification process of already certified tasks if the system is gradually incremented results in excessive costs [7].

# 4 Mixed-criticality scheduling on resource-sharing multicores

The previous section presented the abstract models of mixed-criticality applications and multi-core architectures that can be specified in DOL-Critical. Here, we focus on determining the *mapping*, i.e., the binding of the application tasks to processing cores, and *scheduling*, i.e., the execution order of the tasks on the cores. For the problem of mixed-criticality multi-core scheduling, policies that explicitly address the effects of interference on shared resources need to be considered. For this, we select the Time-Triggered scheduling policy with Synchronization points (TTS) [24], which is designed for temporal isolation and incremental

<sup>&</sup>lt;sup>3</sup> RTE specifies a shared resource, as described in Sect. 8.3.

design. Temporal isolation is achieved by allowing only a statically known subset of tasks

in  $\tau$  with the *same* criticality level to be executed across the cores  $\mathcal{P}$  at any time. This is necessary for deployments on commercial-off-shelf-platforms which do not provide special support for criticality isolation on their shared resources. Allowing a static subset of tasks to be executed in parallel enables, additionally, tight worst-case timing analysis, which is also crucial for certification.

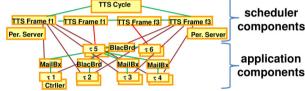

Section 4.1 presents the main principles of the TTS scheduling policy from [24], assuming that a TTS schedule for a particular task set and platform is *given*. We show how to determine a TTS schedule in Sect. 4.2. The design space exploration method of Sect. 4.2 is implemented in the tool suite for DOL-Critical language [17]. This tool suite is used both to provide the input and to analyze the output (via a feedback loop) of the automata-based compilation framework DOL-BIP-Critical.

# 4.1 TTS scheduling

The non-preemptive TTS scheduling policy combines time- and event-triggered task execution. The tasks are mapped statically to cores and no migrations are allowed. A TTS schedule repeats itself over a *scheduling cycle* equal to the hyper-period H of the tasks in  $\tau$  (least common multiple of periods). The scheduling cycle consists of fixed-size *frames* (set  $\mathcal{F}$ ), and each frame is divided further into L flexible-length *sub-frames*. A sub-frame contains only jobs of the same criticality level, and the sub-frames are ordered within a frame in decreasing order of criticality. Within a sub-frame, tasks are scheduled sequentially on each core following a predefined order, namely every task is triggered upon completion of the previous one. The jobs executed in a sub-frame have been generated at or before the respective frame start and have deadline at or after the frame end. The beginning of frames and sub-frames is synchronized among all cores in  $\mathcal{P}$ . The (fixed) frame lengths can differ, but they are upper bounded by the minimum period in  $\tau$ . Each sub-frame (except the first of a frame) starts once all jobs of the previous sub-frame complete execution across all cores. Synchronisation is achieved dynamically at runtime via a barrier mechanism, for the sake of efficient resource utilization.

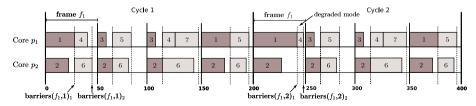

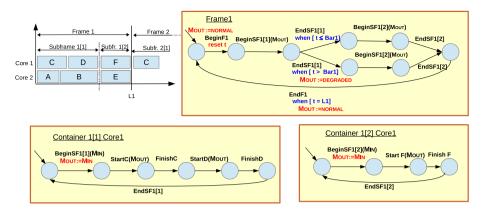

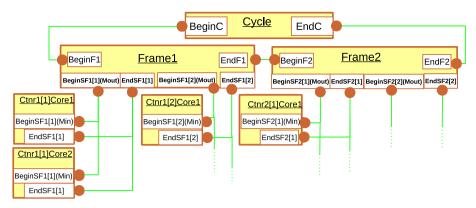

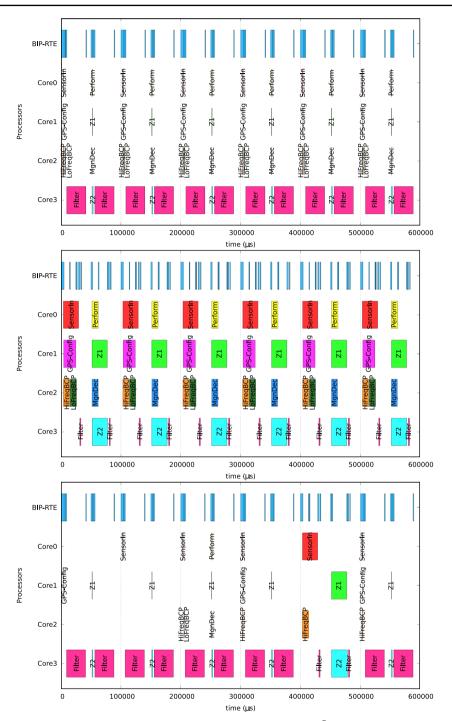

*Example 3* An illustration of a TTS schedule is given in Fig. 2 for a dual-criticality set of seven tasks, with hyper-period H = 200 ms. Figure 2 depicts two consecutive scheduling cycles. The solid lines define the frames and the dashed lines the sub-frames, i.e., potential points, where barrier synchronisation is performed at runtime. The TTS scheduling cycle (H = 200 ms) is divided into four frames of equal lengths (50 ms). Each frame has L = 2 sub-frames: the first for criticality 2 (high) and the second for criticality 1 (low), respectively. At runtime, the length of each sub-frame varies based on the different execution times and memory accessing patterns that the concurrently executed tasks exhibit. For example, the first sub-frame of  $f_1$  finishes earlier when  $\tau_1$ ,  $\tau_2$  run according to their level-1, i.e., low-criticality

Fig. 2 TTS schedule example: 2 cycles (dark annotation: crit. level 2, light annotation: crit. level 1)

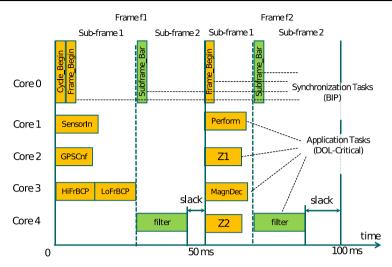

Fig. 3 TTS schedule generated for the FMS application in DOL-BIP-Critical flow

execution profiles (cycle 1) than when at least one task runs according to its level-2, i.e., high-criticality profile (cycle 2).

Despite the dynamic runtime behavior, the sub-frame worst-case lengths can be computed offline for a given TTS schedule by applying timing analysis under shared-resource interference. Function *barriers* :  $\mathcal{F} \times \{1, \ldots, L\} \rightarrow \mathbb{R}^L$  defines a vector with the worst-case length of all sub-frames of a frame when a particular scenario  $\ell$  is followed. We denote the worst-case length of the *k*th sub-frame of frame *f* for the level- $\ell$  scenario as *barriers*(*f*,  $\ell$ )<sub>*k*</sub>. Note that the *k*th sub-frame of *f* contains tasks of criticality level  $\ell' = (L - k + 1)$ . Also,  $\ell'$  corresponds to the highest level execution profile that the tasks in subframe *k* exhibit at runtime:  $\ell \leq \ell'$ . For  $\ell' > 1$ , execution in later sub-frames of *f* may be degraded.

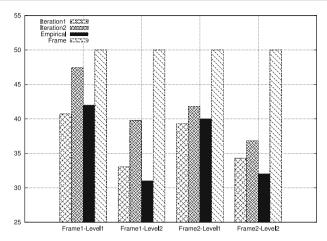

*Example 4* Figure 3 shows the TTS schedule that is generated in our DOL-BIP-Critical flow for the FMS application from Example 1, when we assume five available cores. In our flow, we add to the scheduler a model of runtime overhead of the TTS scheduling policy. The model consists of so-called *synchronization tasks*, which are exclusively executed on Core 0. The execution profiles of those tasks are extracted from the implemenentation of the TTS schedule in BIP automata language. As their names suggest, they represent synchronization of a TTS cycle, frame and sub-frame barrier. High-criticality tasks are depicted in orange and are executed in the first sub-frame, k = 1 ( $\ell' = 2$ ), of each frame  $f \in \{1, 2\}$ . The actual length of this sub-frame depends on execution scenario  $\ell \in \{1, 2\}$  and is bounded by *barriers*( $f, \ell$ )<sub>1</sub>, respectively. The second sub-frame, k = 2 ( $\ell' = 1$ ), contains the lowercriticality tasks, depicted in green. Its length is bounded by *barriers*( $f, \ell$ )<sub>2</sub>, where  $\ell = 1$ , since there is no level-2 execution profile defined for low-criticality tasks. Note that tasks 'HiFrBCP' and 'LoFrBCP' are not executed in parallel due to FMS-specific dependencies discussed later in Sect. 9.1.

#### 4.1.1 Runtime behavior

Given a feasible TTS schedule and the *barriers* function, the scheduler manages task execution on each core within a frame  $f \in \mathcal{F}$  as follows:

- For the kth sub-frame, the scheduler triggers sequentially the corresponding jobs following the predefined order. Upon completion of all jobs on the core, it signals an event and waits until the remaining cores reach the barrier (all jobs of the sub-frame are completed).

- Let the elapsed time from the beginning of the frame until the barrier synchronisation of the *k*th sub-frame be *t*. Below,  $\ell_{max}$  defines the maximum-level execution profile in the frame:

$$\ell_{max} = \underset{\ell \in \{1, \dots, L\}}{\operatorname{argmin}} \left\{ t \le \sum_{j=1}^{k} barriers(f, \ell)_j \right\}, \tag{1}$$

The scheduler will trigger jobs in the next sub-frame such that tasks with criticality level lower than  $\ell_{max}$  run in degraded mode.

- The two previous steps are repeated for each sub-frame, until the last sub-frame is reached.

Note that the decision on whether a task will run in degraded mode affects only the current frame. The interval for observing the execution scenario is reset at frame boundaries.

#### 4.1.2 Feasibility

A given TTS schedule is feasible if and only if the following condition holds for all scenarios  $\ell \in \{1, ..., L\}$ :

$$\sum_{k=1}^{L} barriers(f,\ell)_k \le \mathcal{L}_f, \quad \forall \ f \in \mathcal{F},$$

(2)

where  $\mathcal{L}_f$  denotes the length of frame f. If the condition holds for all frames  $f \in \mathcal{F}$ , it follows that all scheduled jobs can meet their deadlines when running according to their level- $\ell$  profiles.

#### 4.1.3 Temporal isolation and incremental design

The TTS scheduling policy preserves temporal isolation, since only tasks of the same criticality level can run simultaneously on the platform. The isolation is non-symmetric because of the criticality-monotonic dynamic scheduling of the sub-frames within each frame: The jobs of a sub-frame cannot be delayed in any way by lower-criticality jobs, however highercriticality jobs can implicitly delay the execution of lower-criticality by shifting the barrier synchronisation point. The TTS policy enables incremental design, since adding new tasks in sub-frames has no impact on previous sub-frames. In addition, the cross-core utilisation of frames is bounded at design time and the remaining *slack intervals*, where all cores are idle, can be even filled by new frames of other applications. Note that for incremental design, an attractive optimisation goal for a scheduler is to 'pack' the sub-frames as evenly across the core as possible, in order to minimize function *barriers* and maximize the slack intervals.

*Example 5* In the schedule of Fig. 3, the feasibility requirement translates into non-negative slack intervals at the end of each frame. Temporal isolation is apparent from the fact that only tasks of the same criticality level are executed in parallel. Finally, the incremental design could be illustrated if we e.g., replicated task 'Filter' on other cores, which would have no impact on the already scheduled high-criticality tasks.

#### 4.2 Mapping and scheduling optimization

In DOL-Critical, for a given application and target architecture, we seek an optimal TTS schedule. We define a schedule as *optimal* if (i) it is *feasible*, and (ii) the worst-case total sub-frame lengths are *minimal*. The latter condition implies maximal aggregate slack intervals, which can be used for incremental design.

The problem of optimal task mapping on multiple cores is known to be NP-hard in most cases, resembling the combinatorial bin-packing problem [43]. To tackle this challenge, we propose and implement in our tool-chain the *Mixed-Criticality Mapping and Scheduling Optimization* (MCMSO) tool. MCMSO takes as input a mixed-criticality task set  $\tau$  and a set of cores  $\mathcal{P}$ , and returns the mapping function  $\mathcal{M}_{\tau}$  of tasks to cores and a feasible TTS schedule if at least one such schedule exists.

MCMSO performs design space exploration with two main objectives. The primary objective is to find feasible solutions. The second objective is to improve the quality of a feasible solution by maximizing the total size of slack intervals available for incremental design. To perform the exploration, MCMSO implements a heuristic approach based on simulated annealing [38]. In summary, the MCMSO approach is described by the following steps:

- 1. Dimension the TTS scheduling cycle and frame lengths based on the periods of tasks in  $\tau$ .

- 2. Generate a random schedule of the jobs of  $\tau$  within hyper-period *H* on the cores of  $\mathcal{P}$  and the frames  $\mathcal{F}$  of the TTS cycle, such that all dependencies are respected.

- 3. Apply a simulated annealing approach to generate and explore neighboring mappings (assignments of tasks to cores) and schedules (assignment of jobs to sub-frames), until an optimized solution is found or a given computational budget is exhausted.

To express the optimality criteria, we define the cost function of the optimization problem as:

$$Cost(S) = \begin{cases} c_1 = \max_{f \in \mathcal{F}} \{\max_{\ell \in \{1, \dots, L\}} late(f, \ell)\} & \text{if } c_1 > 0\\ c_2 = \|barriers\|_3 & \text{if } c_1 \le 0 \end{cases}$$

(3)

where  $late(f, \ell)$  expresses the difference between the worst-case completion time of the last sub-frame of f and the length of f:

$$late(f, \ell) = \sum_{k=1}^{L} barriers(f, \ell)_k - \mathcal{L}_f.$$

(4)

Component  $c_1$  of the cost function provides a measure of "infeasibility". If  $late(f, \ell) > 0$ , the tasks in f cannot complete execution by the end of the frame for their  $\ell$ -level execution profiles. Therefore, with this cost function, we initially guide the design space exploration to find a feasible solution (by penalising infeasible solutions). When such a solution is found, cost  $c_1$  becomes negative or 0. Thereafter,  $c_2$ , i.e., the 3-norm of all sub-frame lengths,  $\forall f \in \mathcal{F}, \forall \ell \in \{1, ..., L\}$ , is used to minimize the worst-case lengths of all sub-frames. The 3-norm of a vector x with n elements (here, positive real numbers) is defined as  $||x||_3 := (\sum_{i=1}^{n} |x_i|^3)^{1/3}$ . We selected this value to map the flattened vector with the *barriers* values, for all sub-frames of the frames  $f \in \mathcal{F}$  and for all  $\ell \in \{1, ..., L\}$ , over other norms, such as the average or the Euclidean norm, because empirically it provides a good trade-off between reducing the worst-case sub-frame lengths (to ensure schedulability) and enabling progress in the optimization.

The simulated annealing approach for optimizing a TTS schedule is detailed and evaluated extensively in [24].

#### 4.2.1 Timing analysis

MCMSO is tightly coupled with a timing analyzer in our design flow (Fig. 1). During design space exploration, for every visited TTS schedule this tool performs worst-case response time analysis for all tasks in each sub-frame and each execution scenario, in order to compute the worst-case sub-frame lengths, i.e., the function *barriers*. Real-time analysis of concurrently executing tasks under resource contention is a highly complex problem. We have addressed this by applying the theory of timed automata [3] and real-time calculus [61] in [23], and by an analytic arbitration-dependent approach in [24]. The latter approach is implemented in DOL-Critical. For brevity, we omit the timing analysis here and refer the interested readers to the aforementioned publications.

# **5 Description language DOL-Critical**

In our design flow, the DOL-Critical language is used for specifying a mixed-criticality application (Sect. 3.1) and a target architecture (Sect. 3.2). The same language, specifically the integrated MCMSO tool and the timing analyzer (Sect. 4.2), are used for design space exploration and determination of a TTS schedule with maximal aggregate slack time. This section provides details about the user-defined specifications of mixed-criticality applications and multi-core architectures, as well as the auto-generated specification of the mapping and scheduling solution in DOL-Critical.

# 5.1 Specification of a mixed-criticality application

To specify an application that complies with the MC model of computation of Sect. 3.1, in DOL-Critical, we distinguish between two layers: a *functional* layer which consists of tasks and data channels, and a *control* layer which consists of task controllers and task dependencies. The specification of each task contains source code and its execution profiles, while the task controllers (one per task) specify the tasks' activation patterns and deadlines. For the specification, DOL-Critical uses two distinct languages: C/C++ to program the task functionality and complex activation patterns, and XML for the task properties, connections through data channels and dependencies. The choice of these languages is based on practical reasons. C/C++ allows to reuse existing legacy code. XML is easy to handle due to the large number of available tools. Alternative choices are ADA, Simulink, and SDL for functional code [48], and UML or AADL for task control and data interfaces.

# 5.1.1 Inter-task communication

The DOL-Critical model of computation supports two concrete types of the defined in Sect. 3.1 data channels: blackboards (buffers) and mailboxes (queues). Note that unlike most dataflow languages, we use non-blocking communication and do not force the tasks to write/read a fixed number of tokens at each execution. For this reason, every data channel is equipped with a *validity bit*, which indicates that the channel is not empty.

For simplicity, we present *blackboard* as a protected shared variable<sup>4</sup> that can be written via a 'write' port of a single task and read via a 'read' port by one or more tasks. The reading

<sup>&</sup>lt;sup>4</sup> In reality, the blackboard is defined and implemented as a more complex object [17], for which the given simplified definition provides a reasonable abstraction.

| 01 | <process criticality="2" name="square"></process>                                                        | 01 | struct Square state {                                 |

|----|----------------------------------------------------------------------------------------------------------|----|-------------------------------------------------------|

| 02 | <superblock></superblock>                                                                                | 02 | int index:                                            |

| 03 | <info_level="1" <="" maxaccess="10" minaccess="5" td=""><td>03</td><td>int length;</td></info_level="1"> | 03 | int length;                                           |

| 04 | minExecution="7" maxExecution="18"/>                                                                     | 04 | };                                                    |

| 05 | <info <="" level="2" maxaccess="20" minaccess="5" td=""><td>05</td><td>struct DOLCData {</td></info>     | 05 | struct DOLCData {                                     |

| 06 | minExecution="5" maxExecution="25"/>                                                                     | 06 | bool valid:                                           |

| 07 |                                                                                                          | 07 | float value:                                          |

| 08 | <pre><pre>&gt;port type="in data" name="pIN"/&gt;</pre></pre>                                            | 08 | };                                                    |

| 09 | <pre><pre>port type="out data" name="pOUT"/&gt;</pre></pre>                                              | 09 | ,,                                                    |

| 10 | <pre><pre>&gt;port type="in event" name="p2"&gt;</pre></pre>                                             | 10 | void Square init(Square state *ST) {                  |

| 11 | <pre><event name="start"></event></pre>                                                                  | 11 | ST→index =0;                                          |

| 12 |                                                                                                          | 12 | ST->length = 200;                                     |

| 13 | <source location="square.c"/>                                                                            | 13 | }                                                     |

| 14 |                                                                                                          | 14 |                                                       |

| 15 |                                                                                                          | 15 | <b>void</b> Square fire(Square state *ST, int mode) { |

| 16 | <controller deadline="0.2" name="Ctrl square"></controller>                                              | 16 | DOLCData x,y;                                         |

| 17 | <activation type="periodic"></activation>                                                                | 17 |                                                       |

| 18 | <pre><pre>cparameter name="period" value="0.2"/&gt;</pre></pre>                                          | 18 | if (mode = DEGRADED) {                                |

| 19 |                                                                                                          | 19 | return;                                               |

| 20 | <pre><port name="p1" type="out event"></port></pre>                                                      | 20 | }                                                     |

| 21 | <event name="start"></event>                                                                             | 21 |                                                       |

| 22 |                                                                                                          | 22 | if (ST->index < ST->length ) {                        |

| 23 |                                                                                                          | 23 | DOLC_read ("pIN", &x, sizeof(float));                 |

| 24 |                                                                                                          | 24 | if (x.valid) {                                        |

| 25 | <data_channel length="2" name="dataIN" size="8" type="mailbox"></data_channel>                           | 25 | y.value = x.value * x.value;                          |

| 26 | <pre><port name="pdOUT" type="out_data"></port></pre>                                                    | 26 | y.valid = true;                                       |

| 27 | <td>27</td> <td>DOLC_write ("pOUT", &amp;y, sizeof(float));</td>                                         | 27 | DOLC_write ("pOUT", &y, sizeof(float));               |

| 28 | <connection name="dataInToSquare"></connection>                                                          | 28 | }                                                     |

| 29 | <pre><port name="pdOUT"></port></pre>                                                                    | 29 | }                                                     |

| 30 | <pre><port name="pIN"></port></pre>                                                                      | 30 | $ST \rightarrow index = ST \rightarrow index + 1;$    |

| 31 |                                                                                                          | 31 | }                                                     |

|    |                                                                                                          |    |                                                       |

Listing 1 XML source code for process square and data channel dataIN

Listing 2 C source code for process square(square.c)

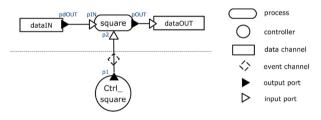

Fig. 4 Square application example

operation does not change the state of the blackboard, which preserves the last written value. If no value was previously written, the reading operation returns with validity bit set to 'false'.

A *mailbox* connects one writing task with one reading task. It is a bounded queue allowing to store several data elements of the same type. The queue length is determined at design time according to the needs of the given application. It is typically desirable that a writing attempt to a full mailbox never occurs in the nominal mode of execution. If this situation still occurs, the writing operation will not block the writer task, but instead it will return an error code. Similarly, reading from an empty mailbox does not cause blocking, but returns with validity bit set to 'false'.

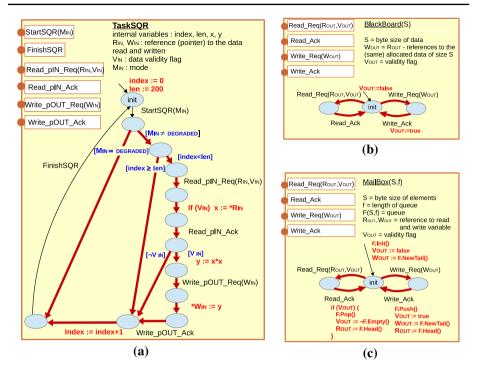

*Example 6* A partial example of a DOL-Critical application specification can be found in Listing 1 (XML) and Listing 2 (C). Note that in the context of DOL-Critical, we use the terms task and process interchangeably. The application (Fig. 4) features one periodic, implicit-deadline task, square. Task square reads floating-point values from a mailbox, dataIN, computes the square of them, and writes the result to mailbox dataOUT, as indicated by the source code in square.c. It is characterized by safety criticality level 2 (high in a dual-criticality system) and its execution time (CPU cycles) and number of resource accesses are given for both execution levels. Note that the parameter ranges for level 1 are included into the respective parameter ranges of level 2. The controller Ctrl\_square, is responsible

to activate square periodically every 0.2s. Communication between the controller and the task is achieved via an event channel. Specifically, Ctrl\_square sends a control event start to square to activate it. The mailbox dataIN, from which square reads, corresponds to a queue with a capacity of 8 elements, each with a size of 2 bytes.

#### 5.1.2 Task functionality

The C/C++ code that defines the functionality of the tasks is written in a DOL-Critical specific *dialect*. The data channels, control events (for communication between controllers and tasks), and ports of data channels and tasks, which are defined in XML, are re-used in the C/C++ code in a way that establishes a unique connection between the XML and the C/C++ specification (see e.g., port "pIN" in Listings 1, 2). Each task has a state data structure, an initialisation subroutine, and a subroutine defining one execution of a job. In the DOL-Critical application programming interface (API), these are denoted <Task>\_state, <Task>\_init(), and <Task>\_fire(), respectively. Furthermore, the API supports two main functions for the communication between tasks: DOLC\_read() and DOLC\_write() (see Fig. 4 for an example). These functions enable reading/writing from/to a data channel and have different semantics depending on the type of the target data channel. The complete semantics of the DOL-Critical programming interface are omitted here for brevity. However, a detailed presentation of the API as well as XML templates for the specification of mixed-criticality applications in DOL-Critical can be downloaded from [17].

# 5.2 Specification of a target architecture and a TTS schedule

For the specification of a resource-sharing multicore that complies with the model of Sect. 3.2, the computation and communication components, along with their attributes and connections, are described in XML format. Specifically, one can model processing cores with attributes such as their frequency, and shared resources with their arbitration policy and maximum access latency. The abstraction level defines the accuracy of the timing analysis, which is performed during design space exploration by the MCMSO tool (Sect. 4.2).

After the scheduling optimization, the MCMSO tool exports the optimized TTS schedule (see Fig. 2 for reference) in XML format. This specification includes (i) the mapping of tasks to cores, (ii) the dimensioning of the TTS scheduling cycle (period, number of frames, frame lengths), (iii) the values *barriers*(f,  $\ell$ )<sub>k</sub> for all sub-frames k of frame  $f \in \mathcal{F}$  and for different execution scenarios  $\ell \in \{1 \dots L\}$ , (iv) the execution order of the assigned tasks on each core and each TTS frame.

Customized XML schemata are used for describing the format of architecture and mapping specifications. These specifications are used as inputs for timing analysis during design space exploration as well as software synthesis after they are compiled into the concurrency language BIP, which is presented in the following section.

# 6 Concurrency language for mixed-criticality systems—BIP

The cornerstone of our rigorous system design approach is the WYVIWYG principle, realized via an automata-based language. We refer to it as '*concurrency language*', as it defines the concurrency and timing semantics of all system software components. After compilation from system specification into a concurrency language, one obtains an executable model that

Fig. 5 BIP model example: four single-port components and four dual-port connectors

can be simulated for functional validation. This model is also used as the input for system analysis and code generation. In our design flow, the concurrency language is BIP.

Under 'BIP' we refer to the so-called 'RT-BIP' dialect [1], which is designed to express networks of connected timed automata components (Sect. 6.1). In the present work, we extend BIP from timed to task automata, by allowing *self-timed* automata transitions. This extension allows expressing control decisions based on runtime monitoring of task response times in timed automata. This feature is important for runtime resource management mechanisms, such as those employed for mixed criticality. For example, recall that the TTS scheduling policy makes online decisions based on the exhibited sub-frame lengths at runtime. A particular feature of BIP is the ability to specify a *network* of components, so that multiple tasks can be executed in different components concurrently. This makes it particularly suitable for multi-core platforms. Our extensions to the original RT-BIP dialect are presented in Sect. 6.2.

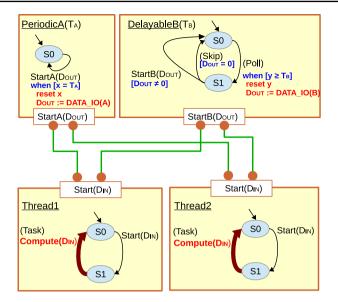

# 6.1 Introduction to BIP

To familiarise the readers with BIP notation, Fig. 5 shows a BIP example, representing two tasks, A and B. These blocks can be scheduled on one of the two available threads running on two different cores. The model consists of four components, namely, 'PeriodicA', 'DelayableB', 'Thread1' and 'Thread2'. All the components are defined by an automaton and a set of *ports* (shown in white rectangles), used for connecting to other components via *connectors* (shown as green lines that join the bullets).

A BIP component has multiple *locations*, denoted in Fig. 5 as 'S0', 'S1'. The *execution run* of a component consists of going from location to location by taking a *transition*, denoted by an arc. For example '(Skip)' is a transition from location 'S1' to location 'S0' in component 'DelayableB'. Each component has an *initial transition*, which brings it to initial location at system start. Initial transition is shown as an arc without origin pointing to the initial location, such as location 'S0' in 'DelayableB'. A transition may have an *enabling condition* and may trigger some *action*. In our figures, we show the conditions in blue color and square brackets,

e.g., component 'DelayableB' has condition ' $[D_{OUT} \neq 0]$ ' for transition 'StartB'. The actions are shown in red color.

The transition labels such as 'StartB' signify a port of the component, in which case the transition *participates in interactions* through this port, which means that it is synchronized with transitions in other components whose ports are connected, e.g., 'StartB' may interact with 'Start' in 'Thread1' or 'Thread2'. Note that a port may participate in one interaction at a time. In our example, each port is linked to two connectors, so if both of them have an enabled interaction, a non-deterministic choice has to be made between them. There are also *internal transitions*, not associated to ports, executed by a component independently. We put their labels in parentheses, e.g., '(Skip)' and '(Poll)'.

In BIP, every component is seen as an object in an object-oriented programming sense. Every component encapsulates some data and some subroutines to manipulate the data. The actions of transitions can call subroutines written in an imperative language (C/C++). In the figures, the actions are depicted as blocks of pseudo-code in red color, e.g., in component 'DelayableB', transition '(Poll)' executes action ' $D_{OUT}$  := DATA\_IO(B)', where a subroutine is called and its return value is assigned to variable ' $D_{OUT}$ '. The actions have access only to the local variables of their component. Nevertheless, some variables are classified as 'OUT' and 'IN' communication variables, bound to ports, e.g., variables  $D_{IN,OUT}$  are bound to port 'Start'. The components send data from 'OUT' to 'IN' variables at interactions via ports. For example, port 'Start( $D_{IN}$ )' receives the new value of  $D_{IN}$  from the  $D_{OUT}$  of either 'StartA' or 'StartB', depending on the component with which it interacts. Note that the data exchange between ports precedes the transitions, e.g., port 'StartA( $D_{OUT}$ )' sends the value of  $D_{OUT}$  before it is modified by the respective transition.

As for the data variables, in this work we consider four main types: integer, Boolean, reference, and queue. A *reference* is a pointer to a user-type object that is allocated at component initialisation. Our models for critical systems do not dynamically allocate data after system initialisation. A *queue* is a circular buffer of statically-known size. Unless explicitly done otherwise in the initial transition or in natural-language annotations, in the presented figures we assume that the initial transition implicitly sets the data variables to zero in the case of integers, 'False' for Booleans etc. Besides data variables, the components can have compile-time parameters, such as period  $T_A$  and minimal execution interval  $T_B$  in Fig. 5.

The condition to execute a transition in fact consists of two parts: a data condition and a timing constraint, indicated by the keyword 'when'. The *timing constraint* defines an interval of time when a transition may be enabled. By default it is 'always', i.e., the whole time axis.

To define the timing constraints a component uses private *clock variables*. The clocks are real-valued variables that are initialized to zero and whose values are continuously and synchronously increasing with the passage of physical time. In our models, we use letters x, y and t for the clocks, e.g., the model in Fig. 5 uses two clocks. The usage of clocks is restricted to two possible scenarios. Firstly, a clock can be reset to zero inside a transition action (e.g., 'reset x' in 'PeriodicA'). Secondly, it can be used in the timing constraint of a transition, see, (e.g., 'when  $x = T_A$ ' in 'PeriodicA').

In our models we assume that all transitions are marked as '*urgent*' in BIP. The presence of 'urgency' attribute means that the transition should start *as soon as (and no later than)* the given transition and all those that participate in the same interaction (if any) get enabled. For example, consider timing constraint 'when  $[y \ge T_B]$ ' in Fig. 5. Due to this constraint, if component 'DelayableB' is in location 'S0', then it should execute transition '(Poll)' immediately when it sees that clock y has reached a value at least equal to  $T_B$ . Note that the 'urgency' property is usually not directly available in timed automata languages, but it is very useful for modeling compute-intensive real-time systems, where typically the system must make progress *immediately* when several conditions become true. For example, in the TTS scheduling policy the barrier synchronization should occur immediately when all tasks scheduled in a given sub-frame finish their execution.

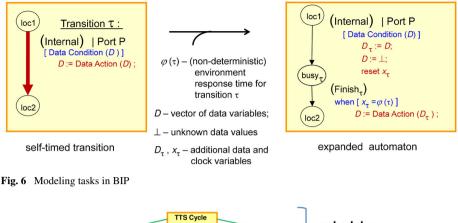

#### 6.2 BIP extension for modeling the tasks

By default, BIP assumed that all data-processing actions cost zero time (at least, conceptually). However, real-time tasks may occupy the processing cores at significant utilisation levels, and to properly model them one should allow executing their data-processing operations in non-zero time. Therefore, in the extended version of BIP, we distinguish between the 'starting' and the 'finishing' times of a transition, and we refer to the time duration in between as *transition response time*. Further, we introduce the '*self-timed*' attribute for the transitions and we assume that all transitions are conceptually instantaneous (i.e., have zero response time) unless they have this attribute. A transition marked as self-timed has a response time equal to the time required to finish the corresponding action on a finite-speed physical resource. This can take any time duration, not known at the moment when the transition starts.

We use *internal self-timed transitions* to represent task processing steps and *self-timed interactions via ports* to represent inter-task communication. In our figures, we denote self-timed transitions by thick arrows, e.g., '(Task)' transitions in Fig. 5. Note that by putting a self-timed transition in between two instantaneous transitions, one can measure its response time by resetting a clock before and checking the clock value after the self-timed transition. This is a necessary feature to program scheduling policies, especially mixed-criticality ones, such as TTS.