DISS. ETH NO. 25980

### Low-Noise InP High Electron Mobility Transistors

A dissertation submitted to attain the degree of DOCTOR OF SCIENCES of ETH ZÜRICH (Dr. sc. ETH Zürich)

presented by

Tamara Popovic, born Saranovac MSc, EPFL Lausanne born on 30 May 1987 citizen of Serbia

accepted on the recommendation of

Prof. Dr. C. R. Bolognesi examiner Prof. Dr. T. Suemitsu, co-examiner

2019

This thesis is dedicated to my son Stefan. Becoming a mother made me realize that I can do almost anything one-handed...even finish writing this thesis.

<u>A Mother's Wisdom</u> Sleep when the baby sleeps. Write the PhD thesis when the baby writes the PhD thesis.

#### ACKNOWLEDGEMENTS

First of all, I would like to thank my supervisor Prof. Colombo Bolognesi for giving me his support, and allowing me to pursue PhD studies in his group (which I love). Besides placing great trust in me regarding the continuance of successful ESA collaboration started by my predecessors, he also granted me a lot of endorsement and freedom for both my research and teaching duties. I am also thankful to Prof. Tetsuva Suemitsu for co-examining this work and his helpful comments and suggestions. I am very grateful to our collaborators of the Centro Astronómico de Yebes for their characterization and implementation of our transistors. I am indebted to Dr. Andreas Alt for introducing me to the world of HEMT fabrication and characterization, as well for all his help and experience he generously shared with me. I owe my gratitude to Hansruedi Benedickter for his assistance with device characterization and measurement equipment maintenance, and to Angel Pallin for his help with device fabrication and for his insights on important life questions. A special thanks goes to Dr. Olivier Ostinelli, whose excellent epitaxial layers are the foundation of this work, and to Diego Ruiz for being a great HEMT teammate and for his invaluable help with noise measurements. For all their criticism, sometimes approval and always being available to help I am forever grateful to the DIRAMICS duo, Dr. Ralf Flückiger and Dr. Diego Marti, this project would not have been the same without them. With great pleasure I thank all my past and present colleagues in MWE group for all their assistance and support: Dr. Anna Hambitzer, Wei Quan, Akshay Arabhavi, Daxin Han, Sara Hamzeloui, Dr. Stefano Tirelli, Dr. Maria Alexandrova, Dr. Rickard Lövblom and Dr. Martin Leich. In addition, I highly appreciate the support of FIRST team members for keeping the cleanroom in an excellent condition and for the help with equipment maintenance, namely Dr. Yargo Bonetti, Dr. Emilio Gini, Dr. Silke Schön, Maria Leibinger, Petra Burkard, Sandro Loosli, Hansjakob Rusterholz and Tobias Häusler. I would also like to express my gratitude to all my ebeam evaporator co-responsibles over the years.

Furthermore, I would like to thank my mother- and father-in-law Gordana and Zoran Popovic for providing me the help I needed to bring this thesis to its end.

I am deeply indebted to my parents Gordana and Lazar Saranovac, and to my sister Tijana Saranovac, for their never ending support, motivation and patience. I am blessed to have so many great things in my life, they would not have been possible without my family.

Finally, I would like thank Nemanja Popovic for being my best friend, understanding partner, loving husband, perfect dad to our son, and for surviving the final stage of my PhD studies; or better said, surviving ME at the final stage of my PhD studies.

#### ABSTRACT

Indium phosphide high electron mobility transistors (InP HEMTs) represent the state-of-the-art technology for both room and cryogenic temperature low noise amplifiers. For years they have been playing a central role in the most demanding niche applications such as radio astronomy and deep space communications, and they are expected to significantly contribute to communication networks of the future. Modern lithography tools have enabled straightforward processing of transistors with sub-100 nm gate lengths, however, the improved RF performance did not result in the expected advancement of noise behavior. The physical limits of noise performance are currently motivating research into this subject, with indications that a significant decrease of minimum noise figure from reducing the gate length cannot be expected. Nevertheless, there is room for improvement in transistor noise behavior with further development of epitaxial growths and bandgap engineering.

This work centers on the optimization of InP HEMTs epitaxial layers by bandgap engineering, small-signal modeling and characterization. A common approach in improving carrier confinement and mobility with narrow bandgap materials used for the channel results in impact ionization taking place even at a relatively low drain bias. The small-signal model was extended to account for the effects of impact ionization and now features excellent agreement between simulated and measured S-parameters at lower frequencies at both room and cryogenic temperatures: we are now able to resolve in which material impact ionization takes place in a composite channel. The noise model proposed in this work including the impact ionization effects shows good agreement with noise measurements performed at room temperature. Achieving the best possible transistor gain and noise behavior depends highly on the quality of contacts: epitaxial structures were therefore optimized in order to reduce contact resistance and improve channel transport properties. Composite channel structures with narrow and wide bandgap materials were implemented to reduce the effects of impact ionization. Further refining of the channel layers in combination with vertical device scaling should allow improvement of both the device bandwidth and minimum noise figure.

#### ZUSAMMENFASSUNG

Indiumphosphid-HEMTs (Feldeffekt-Transistoren, in deren Kanal Elektronen mit sehr hoher Beweglichkeit auf elektrische Felder reagieren) repräsentieren sowohl bei normalen als auch extrem tiefen Arbeitstemperaturen den Stand der Technik aktiver Bauelemente für rauscharme Verstärker. Seit Jahren spielen diese Komponenten eine zentrale Rolle bei anspruchsvollsten Nischenanwendungen, beispielsweise in der Radioastronomie oder Deep-Space Kommunikation. Weiterhin wird ein wesentlicher Beitrag dieser Komponenten für künftige leistungsfähigere Kommunikationsnetze erwartet. Moderne lithographische Methoden erlauben die unkomplizierte Herstellung von Halbleitern mit Gate-Längen von weniger als 100 nm, wobei die verbesserten Eigenschaften bei höchsten Frequenzen keinesfalls das erwartete verbesserte Rauschverhalten beinhalten. Die physikalischen Grenzen des Rauschverhaltens sind gegenwärtig Gegenstand der Forschung, mit der daraus resultierenden Erkenntnis, dass eine Reduzierung der minimalen Rauschzahl durch Reduktion der Gate-Länge nicht erwartet werden kann. Dennoch bestehen Möglichkeiten der Verbesserung des Rauschverhaltens dieser Transistoren mittels Weiterentwicklung der Epitaxie und sogenanntes Bandgap-Engineering.

Diese Arbeit beinhaltet im Wesentlichen die Optimierung der epitaktischen Schichten von Indiumphosphid-HEMTs durch Bandgap-Engineering, der Erstellung von Kleinsignal-Modellen resultierender Transistoren und deren weitergehende Charakterisierung. Eine allgemein gebräuchliche Methode zur Verbesserung der Eingrenzung und Beweglichkeit der Ladungsträger durch Verwendung von Materialien mit schmaler Bandlücke innerhalb des Kanals ergibt Stossionisationsprozesse bei relativ niedrigen Drainspannungen. Das Kleinsignalmodell wurde um die Darstellung der durch Stossionisation bedingten Effekte erweitert und ermöglicht nun eine hervorragende Übereinstimmung zwischen simulierten und gemessenen S-Parametern bei niedrigen Frequenzen und sowohl kryogenen Bedingungen als auch bei Raumtemperatur. Wir können deshalb nun unterscheiden, in welchem Material innerhalb eines aus mehreren Materialien zusammengesetzten Kanals Stossionisation stattfindet. Bei Raumtemperatur vorgenommene Rauschmessungen zeigen gute Übereinstimmung mit dem die Effekte von Stossionisationsprozessen einschliessenden vorgeschlagenen Rauschmodell. Der höchstmögliche Gewinn eines Transistors und dessen bestmöglichstes Rauschverhalten hängt in hohem Masse von der Qualität seiner Kontakte ab. Deshalb wurden die epitaktischen Strukturen hinsichtlich der Reduktion des Kontaktwiderstands und der Transporteigenschaften des Kanals optimiert. Es wurden aus Materialien mit kleiner und grosser Bandlücke zusammengesetzte Kanäle implementiert, um die Effekte der Stossionisation zu reduzieren. Die Weiterentwicklung der Schichtstruktur des Kanals in Kombination mit einer vertikalen Skalierung der Transistoren sollte zu einer Verbesserung hinsichtlich minimal möglicher Rauschzahl und Bandbreite führen.

#### $\rm CONTENTS$

| 1              | INTRODUCTION                        |        |                                             |    |  |  |  |

|----------------|-------------------------------------|--------|---------------------------------------------|----|--|--|--|

| 1.1 Background |                                     |        |                                             |    |  |  |  |

|                | 1.2                                 |        | of Dissertation                             | 4  |  |  |  |

| 2              | THEORY AND CHARACTERIZATION METHODS |        |                                             |    |  |  |  |

|                | 2.1                                 | Device | e Structure and Working Principle           | 5  |  |  |  |

|                |                                     | 2.1.1  | HEMT Heterostructure                        | 5  |  |  |  |

|                |                                     | 2.1.2  | Principle of Operation                      | 7  |  |  |  |

|                | 2.2                                 | Device | e Characterization and Figures-of-Merit     | 8  |  |  |  |

|                |                                     | 2.2.1  | Introduction                                | 8  |  |  |  |

|                |                                     | 2.2.2  | DC Characterization and DC Figures-of-Merit | 9  |  |  |  |

|                |                                     | 2.2.3  | RF Characterization                         | 14 |  |  |  |

|                |                                     |        | 2.2.3.1 RF Figures-of-Merit                 | 14 |  |  |  |

|                |                                     |        | 2.2.3.2 RF Measurements                     | 16 |  |  |  |

|                |                                     | 2.2.4  | HEMT Modeling                               | 19 |  |  |  |

|                |                                     |        | 2.2.4.1 Basic Small-Signal Model            | 19 |  |  |  |

|                |                                     |        | 2.2.4.2 Extended Small-Signal Model         | 22 |  |  |  |

|                |                                     | 2.2.5  | Noise Characterization                      | 26 |  |  |  |

|                |                                     |        | 2.2.5.1 Noise Metrology                     | 26 |  |  |  |

|                |                                     |        | 2.2.5.2 Noise Measurements                  | 27 |  |  |  |

|                |                                     | 2.2.6  | Oscillations                                | 37 |  |  |  |

| 3              | HEN                                 | AT FAE | BRICATION                                   | 43 |  |  |  |

|                | 3.1                                 | Epitax | tial Layer Design                           | 43 |  |  |  |

|                |                                     | 3.1.1  | Introduction                                | 43 |  |  |  |

|                |                                     | 3.1.2  | Description of the HEMT Epitaxial Layers    | 44 |  |  |  |

|                | 3.2                                 | Device | Process Flow                                | 47 |  |  |  |

|                |                                     | 3.2.1  | Overview                                    | 47 |  |  |  |

|                |                                     | 3.2.2  | Cleaving and Characterization               | 47 |  |  |  |

|                |                                     | 3.2.3  | Ohmic Contact Formation                     | 49 |  |  |  |

|                |                                     | 3.2.4  | Device Isolation                            | 53 |  |  |  |

|                |                                     | 3.2.5  | Recess Etching                              | 54 |  |  |  |

|   | 3.2.6 Gate Contact Formation                                                        | 56 |  |  |  |  |

|---|-------------------------------------------------------------------------------------|----|--|--|--|--|

|   | 3.2.7 Active Area Passivation                                                       | 58 |  |  |  |  |

|   | 3.2.8 Overlay Metalization                                                          | 59 |  |  |  |  |

|   | 3.2.9 Air Bridge Metalization                                                       | 60 |  |  |  |  |

| 4 | EPITAXIAL LAYER OPTIMIZATIONS                                                       | 61 |  |  |  |  |

|   | 4.1 Introduction                                                                    | 61 |  |  |  |  |

|   | 4.2 Composite GaInAs/InP Channel                                                    | 63 |  |  |  |  |

|   | 4.3 Composite GaInAs/InPAs/InP Channel                                              | 78 |  |  |  |  |

|   | 4.4 Cap Layer Design for Reduced Access Resistances                                 | 87 |  |  |  |  |

|   | 4.5 Vertically Scaled HEMTs                                                         | 94 |  |  |  |  |

| 5 | CONCLUSION                                                                          | 01 |  |  |  |  |

|   | 5.1 Summary of Results 1                                                            | 01 |  |  |  |  |

|   | 5.2 Outlook 1                                                                       | 02 |  |  |  |  |

| А | APPENDIX                                                                            |    |  |  |  |  |

|   | A.1 Y-parameters of the Exdended Small-Signal Intrinsic Equi<br>alent Circuit Model |    |  |  |  |  |

|   | A.2 Basics of Impact Ionization 1                                                   | 06 |  |  |  |  |

|   | BIBLIOGRAPHY 1                                                                      | 21 |  |  |  |  |

# 1

#### INTRODUCTION

#### 1.1 BACKGROUND

Data of interest in deep space communication networks and radio astronomy is carried by ultra low-power electromagnetic signals as a consequence of the astronomical distances between the signal source and the receiver. The exceptionally low amplitude of these signals, as low as  $6.3 \cdot 10^{-19}$  W, often tends to make them indistinguishable from surrounding interference such as radiation emitted from other celestial objects or noise generated by the receiver itself. To be able use these extremely weak signals without significantly degrading them, special attention needs to be paid to the design of the low-noise receiver. The major bottleneck of the receiver is the first amplifying element in the signal path – Low Noise Amplifier (LNA). Besides amplification of the received signal, the LNA degrades total Signal-to-Noise Ratio (SNR) by the amount of its internally generated noise. For deep space missions, amount of science data returned to Earth is limited by capacity of the space-to-Earth network, with maximum downlink data rate determined by the receiver's SNR. As deep space missions often have limited amount of time to explore their targets, increasing the volume of returned data is a high priority considering both scientific and economical reasons. In the field of radio astronomy, the resolution of image acquired by the radio telescope highly depends on the noise contribution of the receiver, primarily on its first stage the LNA. By cryogenically cooling the LNA, thermal noise will be significantly reduced compared to the room temperature operation due to reduction in resistances and improved transport characteristics [1]. Therefore, with the cooled LNA, the receiver's SNR can be improved considerably, which is followed by the increase of the maximum transferable data rate or the enhanced radio image resolution. InP-based High Electron Mobility Transistors (HEMTs) as the key components of LNAs proved to be very attractive due to their superior channel transport properties such as high electron mobility and high saturation velocity at both room and cryogenic temperatures.

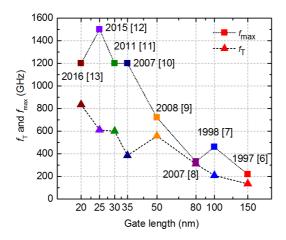

Since the invention of the first HEMT based on the AlGaAs/GaAs heterostructure [2], much effort was invested in improving the original design including modifications of the epitaxial layers and progresses in manufacturing technology. One of the first major steps was introduction of a thin GaInAs layer as the channel in AlGaAs/GaAs structure, improving electron transport, carrier confinement and allowing higher sheet charge density [3]. From there it did not take long to develop the first pseudomorphic Al<sub>0.48</sub>In<sub>0.52</sub>As/Ga<sub>0.47</sub>In<sub>0.53</sub>As/InP HEMT [4], and a year later, the first HEMT with increased In content in the channel [5]. Introduced strain in previously lattice matched Ga<sub>0.47</sub>In<sub>0.53</sub>As channel resulted in a decrease of the electron effective mass and a rise of the low field mobility followed by additional gain in terms of microwave performance. AlInAs/GaInAs/InP heterostructures excelled over previously used AlGaAs/GaInAs/GaAs due to higher conduction band discontinuity, enhanced transport properties and better carrier confinement, however at a cost of having lower breakdown voltage and more pronounced impact ionization effects. The advancements in bandgap engineering, further revisions of the AlInAs/GaInAs/InP layer structure, and reduction of the transistor parasitics by gate, source, and drain scaling made the InP-based HEMT a key component of today's high-speed, high-gain and low-noise applications such as THz transmitters, receivers, LNAs and frequency multipliers. Figure 1.1 shows the improvement of cut-off and maximum oscillation frequencies with the gate length scaling over the years for some benchmarked InP HEMTs.

Cryogenic noise performance of InP HEMTs has also made an immense progress in the last few decades, allowing construction of ultra low-noise amplifiers implemented as Hybrid Microwave Integrated Circuits (HMICs) or Monolithic Microwave Integrated Circuits (MMICs). Table 1.1 shows reported performance in terms of minimum noise temperature and gain per stage for today's state of the art cryogenic InP HEMT LNAs MMICs.

The present work indicates there is however a limit to the continuous improvement of InP HEMT capabilities, particularly regarding noise performance. While aggressive transistor scaling and increasing channel In content to the point where it consists of pure InAs can improve its bandwidth, transistor noise performance will suffer due to the Short-Channel Effects (SCEs), reduced quality of pinch-off and increased impact ionization in the channel. Assumption that an improvement in  $f_{\rm max}$  under constant drain current should result in a corresponding improvement in minimum noise figure is

FIGURE 1.1:  $f_{\rm max}$  and  $f_{\rm T}$  increase with gate length reduction.

| Freq. band (GHz) | $T_{\min}$ (K) | $L_{\mathbf{g}}$ (nm) | Gain/stage (dB) | Year          |

|------------------|----------------|-----------------------|-----------------|---------------|

| 4-8 <sup>1</sup> | 1.4            | 130                   | 14.7            | 2012 [14]     |

| 4.6-13.8         | 2.6            | 100                   | 14              | 2017 [15]     |

| 24-40            | 7              | 100                   | 9.7             | 2017 [16]     |

| $25.5 - 32.3^1$  | 9.8            | 100                   | 8.3             | 2015 [17]     |

| 26-40            | 8              | 80                    | 9               | $2012 \ [18]$ |

| 28-52            | 6.7            | 100                   | 8.5             | 2017 [16]     |

| 50-75            | 18             | 35                    | 9               | 2017 [19]     |

| 65-116           | 18.6           | 100                   | 6               | 2017 [20]     |

| 67-114           | 22             | 35                    | not reported    | 2017 [21]     |

| 70-100           | 23             | 35                    | not reported    | 2017 [21]     |

| 85-116           | 26             | 35                    | 8.5             | 2017 [22]     |

TABLE 1.1: Overview of performance for today's state of the art cryogenic LNAs.

not valid for sub-100 nm gate lengths due to the large increase in drain noise countering the desired  $f_{\text{max}}$  enhancement [23]. Therefore, for HEMTs that

$<sup>^1\</sup>mathrm{Implemented}$  as HMIC

are to be utilized in low-noise applications a trade-off has to be made between further advances in RF performance and their influence on the minimum achievable noise figure.

#### 1.2 SCOPE OF DISSERTATION

The aim of this work was to further improve transistor's noise performance, partly for the "Next Generation of Very Low Noise Cryogenic Amplifiers in K/Ka Band" project collaboration with *Centro Astronómico de Yebes* and *European Space Agency (ESA)*. The development of new generations of transistors included design and optimization of new epitaxial layers that were grown in ETH FIRST Laboratory, followed by the optimization of fabrication process and characterization.

This thesis is structured in the following way:

#### • Chapter 2: Theory and Characterization Methods

This chapter focuses on the HEMT principle of operation, description of the main measurement systems with most important figures-of-merit, followed by basic transistor model and extraction methods.

#### • Chapter 3: HEMT Fabrication

The first part of Chapter 3 describes the epitaxial layers used to fabricate transistors, and in the second part overview of the standard process flow is presented.

## • Chapter 4: Optimization of the HEMT Epitaxial Layer Structure

Chapter 4 describes several optimizations which were carried out in order to improve device performance together with comparison of DC, RF and noise measurement results.

#### • Chapter 5: Conclusion and Outlook

The results achieved in the course of this work are discussed and summarized. Also, suggestions for future work are given.

#### THEORY AND CHARACTERIZATION METHODS

#### 2.1 DEVICE STRUCTURE AND WORKING PRINCIPLE

#### 2.1.1 HEMT Heterostructure

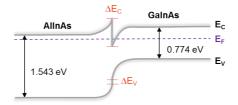

The working principle of a HEMT is based on the formation of a heterojunction between two semiconductor materials with different bandgaps [24]. Creation of a dense quasi two-dimensional sheet of electrons, localized at the interface between the two materials, results in an enhanced carrier mobility in this transistor type. In P based HEMTs, which are the focus of this work, have thin layers of lattice matched (or strained) AlInAs and GaInAs representing wide and narrow bandgap semiconductors that form a type I heterostructure. The energy band diagram of such system has discontinuities at the junction, as shown in figure 2.1, as a result of different electron affinities of two materials. If a wide bandgap AlInAs layer is n-doped, electron diffusion occurs across the heterointerface leading to a build-up of electrons in GaInAs, and to a depleted zone in AlInAs. The conduction band discontinuity ( $\Delta E_{\rm C}$ ) on the AlInAs side of the junction serves as a barrier which separates majority carriers electrons accumulated in GaInAs and remained ionized donors in AlInAs. Together with the resulting conduction band edge on the GaInAs side, the potential barrier forms a quantum well along the boundary of two materials where large number of electrons is confined.

FIGURE 2.1: Schematic band diagram of a type I heterojunction consisting of two semiconductors with different bandgaps.

#### 6 THEORY AND CHARACTERIZATION METHODS

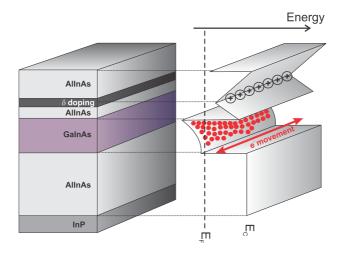

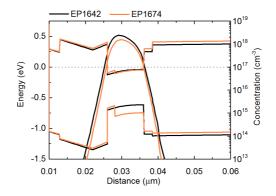

Electrons confined in the GaInAs quantum well are only free to move in a quasi two-dimensional plane which is parallel to the heterointerface forming a Two-Dimensional Electron Gas (2DEG). The energy of electrons is quantized in direction perpendicular to the heterointerface. Current flowing through a HEMT 2DEG channel will be a function of 2DEG sheet carrier density,  $n_s$ , and electron mobility,  $\mu_n$ . To achieve good transport properties and high electron density in the 2DEG, the semiconductor forming the quantum well should have a narrow bandgap with low electron effective mass such as In-rich GaInAs or pure InAs. Figure 2.2 represents a typical InP HEMT heterostructure along with the corresponding conduction band diagram. It utilizes two AlInAs/GaInAs heterointerfaces to confine the electrons between two potential barriers.

FIGURE 2.2: Schematic of a typical InP HEMT heterostructure together with conduction band diagram in thermal equilibrium.

Doping of top AlInAs layer is done with a thin layer of Si donor atoms, referred to as  $\delta$ -doping. As a result of separating free electrons from their donors with the potential barrier, impurity scattering is reduced and the mobility of electrons is enhanced, justifying the name of these transistors. At cryogenic temperatures, where impurity and alloy scattering are two dominating scattering mechanisms [25], separation of carriers and donors leads to further increase of the channel mobility and decrease of the channel sheet

7

resistance. Consequently, the transistor exhibits higher gain and overall better noise behavior, thus motivating the study of cryogenically cooled LNAs based on InP HEMTs.

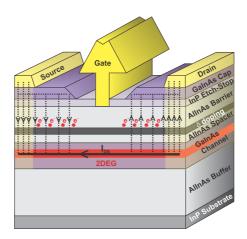

#### 2.1.2 Principle of Operation

Figure 2.3 shows the cross-section of the InP HEMT structures processed in this work, with a T-shaped gate contact placed between two annealed Ohmic source and drain contacts. Besides the layers forming a heterostructure, as described in figure 2.2, fabricated devices also have a thin InP etch-stop layer. A good HEMT device also requires a highly *n*-doped GaInAs capping layer in order to allow low resistance source and drain Ohmic contact formation. Source and drain contacts are placed directly on the GaInAs layer, while the cap has to be removed underneath the gate to allow the formation of the gate Schottky contact. In the growth direction, the full HEMT structure as described in figure 2.3 consists of an AlInAs buffer layer, a GaInAs or composite channel layer, an AlInAs spacer, a  $\delta$ -doped Si plane, an AlInAs Schottky barrier, an InP etch stop and a highly-doped GaInAs (or composite GaInAs) cap layer.

The operational principle of a HEMT shown in figure 2.3 is as follows: voltage applied at the gate contact modulates the amount of electrons in the 2DEG which participate in current transport, while source and drain contacts drive those electrons through the GaInAs channel. A majority of electrons tunnel from the annealed source and drain contacts directly to the channel to contribute to the current. However, a fraction of electrons flows through the highly-doped cap layer and subsequently tunnels through the barrier layer to the channel thereby effectively making the cap layer serve as an extension of the metal contacts. By applying a negative voltage at the gate, the 2DEG underneath the contact is depleted and the current through the channel, driven by the drain-source voltage, is small. By applying a more positive voltage at the gate, the sheet density of the 2DEG, as well as the current, is increased. For large forward gate bias, the current will saturate and the channel is said to be fully open. Further increase of the forward gate bias leads to a formation of a parasitic parallel channel in the barrier layer which is an undesirable effect leading to diminished transistor control and worse noise behavior.

FIGURE 2.3: Cross-section of the InP HEMT processed in this work with gate Schottky contact and annealed source and drain Ohmic contacts. Arrows depict the electron movement and the current direction throughout the structure.

#### 2.2 DEVICE CHARACTERIZATION AND FIGURES-OF-MERIT

#### 2.2.1 Introduction

There are several measurements and figures-of-merit used to characterize InP HEMTs, most important being DC, RF and noise measurements at both room and cryogenic temperatures. While DC and RF characterizations are fairly straightforward, noise measurements invoke a complex procedure. Besides having several noise sources which are bias and temperature dependent, a single InP HEMT noise level is often as low as the measurement uncertainty, particularly at cryogenic temperatures. Noise characterization therefore requires a sophisticated measurement setup, very precise calibrations of instruments and accurate noise models for the device. However, noise behavior can be predicted to some extent by examining different figures-of-merit extracted from DC and RF measurements.

Along the course of this work, all devices were DC and RF characterized at both room and cryogenic temperatures. During measurements at room temperature, devices were exposed to ambient light at the manual probe

9

station. For cryogenic characterization at 15 K, devices were measured with a covered viewport using Lakeshore CRX-4K probe station. Representative devices were later selected for additional noise characterization at room temperature.

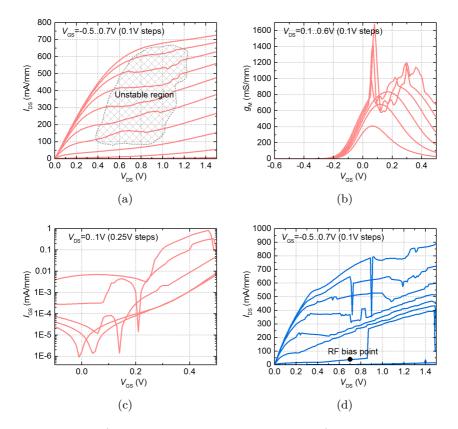

#### 2.2.2 DC Characterization and DC Figures-of-Merit

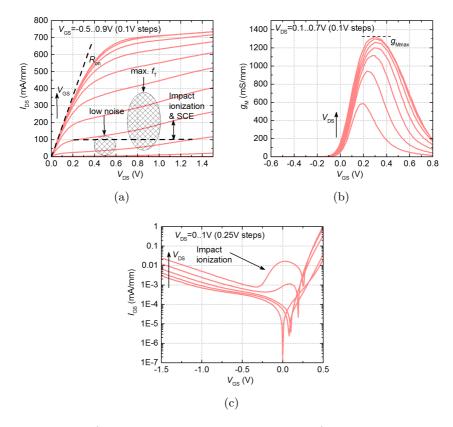

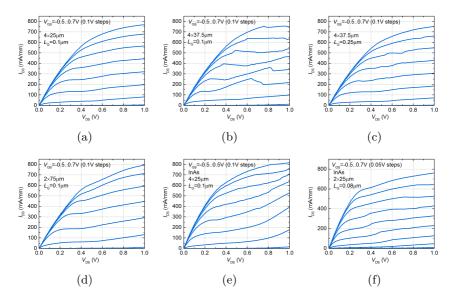

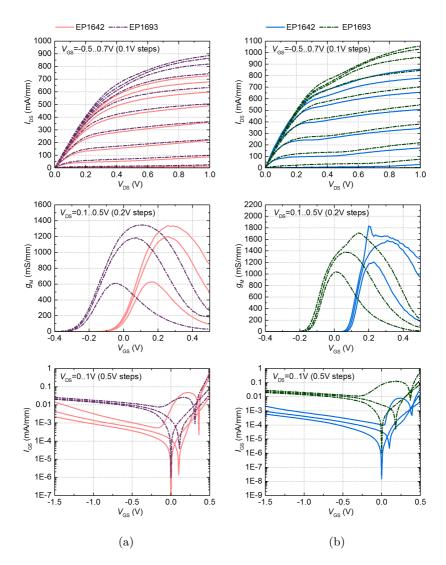

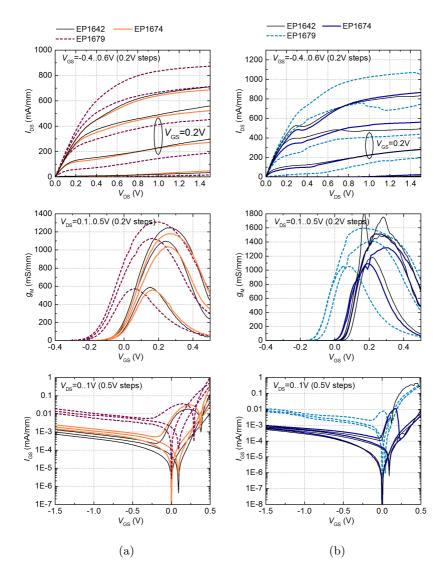

DC characteristics were obtained from on-wafer measurements using an Agilent HP4156B parameter analyzer. A common way of presenting the DC behavior of a HEMT is to plot the normalized I-V characteristics, the extrinsic DC transconductance  $g_{\rm M}$  and the gate leakage current  $I_{\rm GS}$ . Figure 2.4 shows the typical DC measurement of a two-finger HEMT, with a gate finger width of 25 µm (2 × 25 µm), measured at 300 K, for a device processed on standard epitaxial layer defined in section 3.1. Bias regions for obtaining best noise performance and highest cut-off frequency  $f_{\rm T}$  are depicted in figure 2.4a.

For low drain-source voltages  $I_{\rm DS}$  increases linearly, with a slope depending on the on-state resistance  $R_{\rm on}$  as depicted in figure 2.4a. At high  $V_{\rm DS}$ ,  $I_{\rm DS}$ does not stay constant but is increasing due to SCEs and impact ionization generated electrons in the narrow bandgap GaInAs channel, which reduce the output resistance of the HEMT.

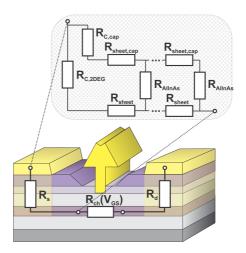

$R_{\rm on}$  can be used as a figure-of-merit to predict the noise behavior, as low values of  $R_{\rm on}$  imply low parasitic resistances and better noise behavior. For epitaxial layers where electrons tunneling indirectly through the cap and barrier layer into the channel do not contribute significantly to  $I_{\rm DS}$ , a simplified expression can be used to calculate  $R_{\rm on}$  based on the contact resistance  $R_{\rm C}$  and channel sheet resistance  $R_{\rm sheet}$ :

$$R_{\rm on} \approx 2 \cdot R_{\rm C} + R_{\rm sheet} \cdot l_{\rm SD}$$

(2.1)

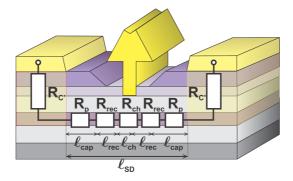

where  $l_{\rm SD}$  is the source-drain spacing (set to 1 µm along the course of this work). In figure 2.4a, extracted  $R_{\rm on} \approx 0.57 \,\Omega$ ·mm which corresponds well to extracted contact resistance  $R_{\rm C} = 0.11 \,\Omega$ ·mm and channel sheet resistance  $R_{\rm sheet} = 350 \,\Omega$ /square for our standard epitaxial layer. If conduction through cap and barrier layers is not negligible, a more complex model for  $R_{\rm on}$  should be used. The complex model is more suited for epitaxial structures optimized for non-annealed Ohmic contacts, structures with high  $\delta$ -doping or structures with very high cap doping where the cap serves as the extension of the source and drain metal contacts. As presented in figure 2.5,

FIGURE 2.4: a) Normalized DC output characteristic, b) transconductance  $g_{\rm M}$  and c) gate current of a  $2 \times 25 \,\mu{\rm m}$  HEMT with 100 nm gate length measured at 300 K.

a more complete  $R_{\rm on}$  model accounts for: contact resistance both directly from the metal layer to the channel and indirectly from the cap through the barrier into the channel, conductance through the cap and barrier layers in parallel over the length of the cap  $(R_{\rm p})$ , resistance of the channel in the recess area  $(R_{\rm rec})$  and resistance of the channel  $(R_{\rm ch}(V_{\rm GS}))$  underneath the gate:

$$R_{\rm on} \approx 2 \cdot R_{\rm C'} + 2 \cdot R_{\rm p} \cdot l_{\rm cap} + 2 \cdot R_{\rm rec} \cdot l_{\rm rec} + R_{\rm ch}(V_{\rm GS}) \cdot l_{\rm ch}.$$

(2.2)

FIGURE 2.5: Cross-section of the InP HEMT showing contributions to the on-state resistance  $R_{on}$ .

Separated contributions of the individual terms from equation 2.2 are difficult to obtain; up to some extent the parallel resistance of channel and cap  $R_{\rm p}$  can be extracted from standard Transfer Length Method (TLM) measurements on the full epitaxial structure, and  $R_{\rm rec}$  can be taken as equal to  $R_{\rm sheet}$  obtained from Hall measurements when the cap is layer removed. Contact resistance is hard to extract due to the fact that it accounts both for direct and indirect contact to the channel. One possibility investigated was fabrication of the TLM structures with constant  $l_{cap}$  and different lengths of the recessed area  $l_{rec}$ . However, measurements of those types of structures failed to provide linear and reproducible dependence of measured resistance versus the  $l_{rec}$ , hence the accurate  $R_{C'}$  could not be extracted.

Another important figure-of-merit is the quality of gate control over the channel, represented by the transconductance  $g_{\rm M} = \partial I_{\rm DS}/\partial V_{\rm GS}$ , and plotted in figure 2.4b. High  $g_{\rm M}$  values indicate high intrinsic and RF transconductance,  $g_{\rm M,intr}$  and  $g_{\rm m}$ , and allow predictions of the maximum transistor gain. Besides having high control of the channel current via gate voltage, a good pinch-off behavior is necessary to achieve good noise performance [1]. To

assess the pinch-off quality, the ratio of the drain current in on- and offstate  $(I_{\rm on}/I_{\rm off})$  around the threshold voltage is used. Good pinch-off at room temperature is considered to be  $I_{\rm on}/I_{\rm off} > 70$  dB.

The gate diode current plotted in figure 2.4c should be below acceptable level required for good noise devices [1], which is on order of several  $\mu$ A/mm at room temperature, and an order of magnitude lower for cryogenic applications. To compare the leakage current for different epitaxial layers, the value of  $I_{\rm GS}$  at  $V_{\rm GS} = -1$  V and  $V_{\rm DS} = 0$  V was usually used. Impact ionization, visible in the measurement of the drain current, can also be observed in the measurement of the gate current as the bell-shaped increment (hump) present at higher drain voltages. At moderate negative  $V_{\rm GS}$  values, electron concentration in the channel is significant and the impact ionization coefficient is high if the drain voltage is high. Additional electron-hole pairs are generated in the region between gate and drain, and fraction of them can transfer over the barrier, get collected by the gate, and add to the gate current thereby giving the gate current specific bell-shape. If the gate current is high this feature might not be visible. However, impact ionization will still be noticeable in the I-V characteristic and S-parameters.

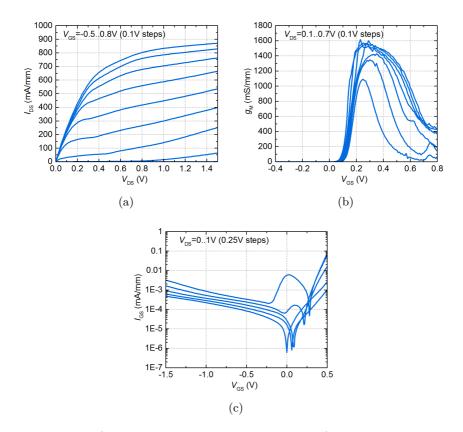

Figure 2.6 shows the DC measurement at 15 K of the same  $2 \times 25 \,\mu\text{m}$  HEMT from figure 2.4. At cryogenic temperatures  $R_{\rm on}$  is decreased while maximum current, transconductance and  $I_{\rm on}/I_{\rm off}$  ratio are improved due to decreased thermal resistances, as shown in figures 2.6a and 2.6b. At lower temperatures gate leakage is decreased due to reduced thermionic emission over the Schottky barrier as shown in figure 2.6c.

FIGURE 2.6: a) Normalized DC output characteristic, b) transconductance  $g_{\rm M}$  and c) gate current of a  $2\times25\,\mu{\rm m}$  HEMT with 100 nm gate length measured at 15 K.

#### 2.2.3 RF Characterization

#### 2.2.3.1 RF Figures-of-Merit

High frequency behavior of two-port networks such as HEMTs is usually described using the scattering parameters. S-parameters matrix elements are defined as:

$$S_{11} = \frac{b_1}{a_1} \bigg|_{a_2=0} S_{21} = \frac{b_2}{a_1} \bigg|_{a_2=0}$$

$$S_{12} = \frac{b_1}{a_2} \bigg|_{a_1=0} S_{22} = \frac{b_2}{a_2} \bigg|_{a_1=0}$$

(2.3)

where  $a_1$  and  $b_1$  are the intensities of the incident and the reflected wave at port 1, and  $a_2$  and  $b_2$  are the intensities of the incident and the reflected wave at port 2.  $S_{ii}$  therefore represents the reflection coefficient at port *i* when all other ports are terminated with a reference impedance, whereas  $S_{ij}$  represents the transmission coefficient from port *j* to port *i* when port *i* is terminated with a reference impedance. Reference (or characteristic) impedance of measuring systems, probes, cables etc. in practice is usually 50 or 75  $\Omega$ . S-parameters are complex numbers, with real and imaginary part, and their graphical representation with respect to the frequency is usually done in the polar coordinate system such as the Smith diagram. The S-parameter matrix can be transformed to any other two-port network parameter set such as impedance (Z), admittance (Y), hybrid (H) and chain matrix (ABCD) parameters and vice versa.

*S*-parameters can be used to determine the RF figures-of-merit, of which the two most commonly used for high speed transistors are the current gain cut-off frequency  $f_{\rm T}$  and the maximum oscillation frequency  $f_{\rm max}$ . For a Field Effect Transistor (FET),  $f_{\rm T}$  is defined as the frequency where the small-signal common-source current gain  $(|h_{21}| = \frac{|i_{\rm ds}|}{|i_{\rm gs}|})$  drops to 1.  $h_{21}$  can be calculated from measured *S*-parameters as:

$$h_{21} = \frac{-2 \cdot S_{21}}{(1 - S_{11}) \cdot (1 + S_{22}) + S_{12} \cdot S_{21}}.$$

(2.4)

The frequency at which the power gain is equal to 1 is called  $f_{\text{max}}$ , but, due to different definitions used for power gain  $f_{\text{max}}$  is not a unique value. Assuming that  $|S_{12}|$  is small and can be neglected (which is mostly the case in practice) a device can be considered to be unilateral, and Mason's unilateral power gain (U) can be used to determine  $f_{\text{max}}$ . U can be calculated from measured S-parameters as follows:

$$U = \frac{\left| \left( S_{21}/S_{12} \right) - 1 \right|^2}{2 \cdot \left( k \cdot \left| S_{21}/S_{12} \right| - \operatorname{Re}\left( S_{21}/S_{12} \right) \right)}$$

(2.5)

where k is the Rollet's stability factor:

$$k = \frac{1 - |S_{11}|^2 - |S_{22}|^2 + |S_{11} \cdot S_{22} - S_{12} \cdot S_{21}|^2}{2 \cdot |S_{21} \cdot S_{12}|}.$$

(2.6)

The device is said to be unconditionally stable when stability factor  $k \ge 1$  for all frequencies of interest. If that condition is fulfilled, a useful figure-of-merit is the maximum available gain (MAG):

MAG =

$$\frac{|S_{21}|}{|S_{12}|} \cdot (k - \sqrt{k^2 - 1}).$$

(2.7)

MAG indicates the highest amount of power gain that can be achieved with simultaneous conjugate matching on the input and the output of the device, but it is defined only for  $k \ge 1$ . If k < 1 for certain frequencies, the device is conditionally stable and the maximum stable power gain (MSG) defined as:

$$MSG = \frac{|S_{21}|}{|S_{12}|} \tag{2.8}$$

should be used to calculate the power gain under stable operating conditions. At low frequencies, transistor gain is usually very high and consequently k < 1, therefore MSG is used for characterization. As the frequency increases, the gain is reduced and k >= 1 is obtained. In this case MSG converts into MAG. Unlike MAG, the unilateral gain U is defined for all values of k. All three power gain definitions can be used for estimating the  $f_{\rm max}$  of the transistor. Along the course of this work,  $f_{\rm max}$  was determined from Mason's unilateral power gain, unless noted otherwise.

#### 2.2.3.2 RF Measurements

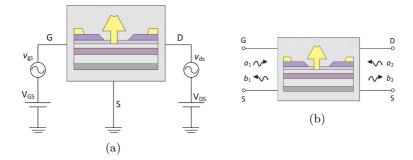

In order to measure the RF properties of InP HEMTs, devices were biased by applying DC voltages at the gate and drain as depicted in figure 2.7a. An RF signal was then superimposed to the device by a Vector Network Analyzer (VNA), either to the gate or drain electrode successively, for the selected frequency range. The RF signal amplitude was small and did not affect the bias point of the device thereby facilitating the small-signal characterization of the HEMT. The VNA measures intensities of incident  $(a_1)$ and  $a_2$ ) and reflected ( $b_1$  and  $b_2$ ) normalized voltage waves over a selected frequency range as depicted in figure 2.7b, and calculates the scattering parameters as described in equations 2.3. During the course of this work all S-parameter measurements, both at room and cryogenic temperatures, were performed using an Agilent N5245 PNA-X network analyzer, with an Agilent HP4156B parameter analyzer used for biasing. Devices were measured on-wafer, up to 50 GHz, with a reference impedance of 50  $\Omega$ . The PNA-X was calibrated and systematic errors of the test setup were corrected up to the measuring probe tips using the Line-Reflect-Reflect-Match (LRRM) technique with Thru/Short/Load off-wafer calibration standards.

FIGURE 2.7: a) Schematic representation of the measurement setup used for measuring the RF behavior of InP HEMT at a bias point defined by  $V_{\rm DS}$  and  $V_{\rm GS}$ . b) Corresponding two-port network with port 1 defined by gate and source, and port 2 by drain and source electrodes.

The microwave probes used for contacting and measuring the device are usually large compared to the transistor active region, therefore device lay-

17

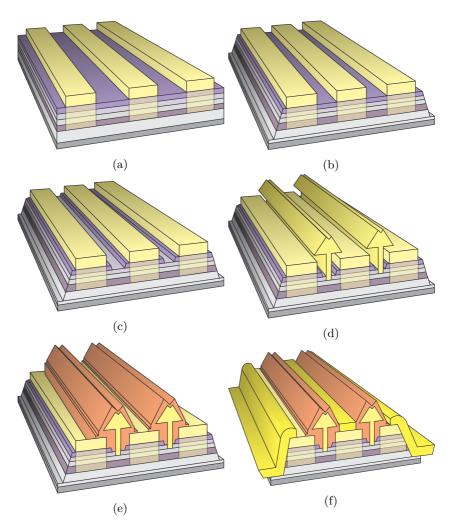

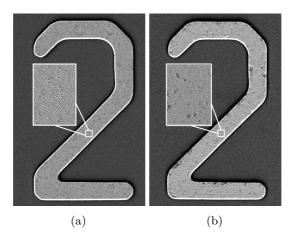

out had to include appropriately sized probing pads. Probing pads contribute with their own parasitic capacitance, inductance and resistance, and consequently the measured S-parameters include both device and pad elements. To take out the parasitic effects of the pads, a deembedding procedure was required, where the contribution of the pads was mathematically removed from the measured data. As the first step, special OPEN and SHORT structures, fabricated together with devices, were measured over the same frequency range. These structures use an identical layout to the transistor except that the active area is covered with a metalization for the SHORT and omitted for the OPEN structure, as depicted in figure 2.8. An iterative deembedding procedure [26] gradually subtracts the contributions of the measured OPEN and SHORT structures divided in n non-equal sections from the measured S-parameters. The deembedded Y-parameters of the Device Under Test (DUT),  $Y_{\text{DUT},n}^{\text{OS}}$ , can be calculated as follows:

$$Y_{\text{TEMP},i}^{\text{OS}} = \frac{Y_{\text{O},i-1}^{\text{OS}}}{n+1-i}$$

(2.9)

$$Z_{\text{TEMP},i}^{\text{OS}} = \frac{(Y_{\text{S},i-1}^{\text{OS}} - Y_{\text{TEMP},i}^{\text{OS}})^{-1}}{n+1-i}$$

(2.10)

$$Y_{\text{DUT},i}^{\text{OS}} = \left( (Y_{\text{DUT},i-1}^{\text{OS}} - Y_{\text{TEMP},i}^{\text{OS}})^{-1} - Z_{\text{TEMP},i}^{\text{OS}} \right)^{-1}$$

(2.11)

where  $Y_{\text{DUT},0}^{\text{OS}}$ ,  $Y_{0,0}^{\text{OS}}$  and  $Y_{s,0}^{\text{OS}}$  are the measured two-port admittance parameters of the DUT, OPEN and SHORT, n is the number of iterations and i is swept from 1 to n. n was usually set to a high value, typically 100, to allow the method to converge to a unique solution. From the deembedded S-parameters,  $f_{\text{T}}$  and  $f_{\text{max}}$  of the intrinsic transistor without the parasitic influence of the pads can be obtained.

For high speed transistors,  $f_{\rm T}$  and  $f_{\rm max}$  are usually above the measurement setup frequency range: it is therefore not possible to directly extract them using equations 2.4-2.8. However, both  $|h_{21}|$  and U behavior, plotted in dB on a logarithmic frequency scale, can be approximated using single pole functions with a -20 dB/dec roll-off after the first pole. Theoretical slopes form MSG and MAG are -10 dB/dec and -20 dB/dec, respectively. To be able to fit the measured data with a single pole fit (for  $|h_{21}|$  and U) or -10/-20 dB/dec linear fit (for MSG/MAG), devices need to be at least measured up to the first pole, or up to the frequency where  $k \ge 1$  and MSG converts to MAG.

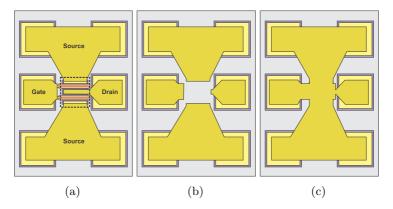

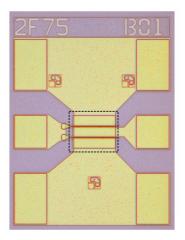

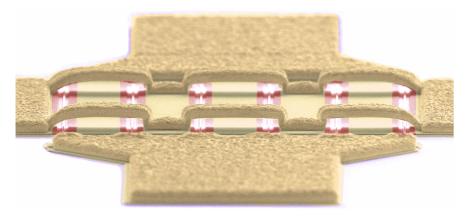

FIGURE 2.8: a) Schematic illustration of a complete two-finger transistor,b) OPEN and c) SHORT structures used to deembed the effects of the measurement pads.

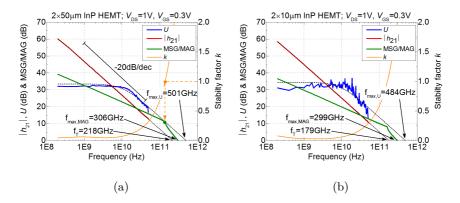

$f_{\rm T}$  and  $f_{\rm max}$  can be then extrapolated from the intersection of the respective characteristics with 0 dB as shown in figure 2.9a. Figure 2.9a shows the  $|h_{21}|$ ,  $U, {\rm MSG/MAG}$  and k calculated from measured S-parameters for a  $2\times50\,\mu{\rm m}$  device, fabricated on standard epitaxial layer described in section 3.1. Device was measured at room temperature, and biased for maximum  $f_{\rm T}$ .

Due to their low input resistance and capacitance, nanoscale HEMTs may exhibit resonant spikes in U as a consequence of the measurement uncertainties in S-parameters which can make a precise single pole fit and extrapolation of  $f_{\text{max}}$  difficult [27]. These resonances are more pronounced for transistors with  $S_{11}$  close to unity, as is the case for narrow gate widths, short gate lengths or large gate-to-channel distance, all resulting in small gate-to-source capacitance  $C_{\text{gs}}$ . According to equation 2.5, U is also very sensitive to the  $S_{21}/S_{12}$  ratio, which is inherently decreasing for narrower gate widths. Figure 2.9b shows the  $|h_{21}|$ , U, MSG/MAG and k calculated from measured S-parameters for a short  $2 \times 10 \,\mu\text{m}$  device biased at the same bias point as the device in figure 2.9a. As it can be seen, clean extrapolation of  $f_{\text{max}}$  using the single pole fit through the U data with resonant spikes is problematic and its accuracy questionable. However, extrapolating  $f_{\text{max}}$  using MSG/MAG is only marginally better, since measurements above 100 GHz are required even for devices with low  $f_{\text{T}}$ .

19

FIGURE 2.9: Measurement of the current gain  $(|h_{21}|)$ , unilateral power gain (U), maximum stable gain (MSG) and maximum available gain (MAG) together with Rollet's stability factor k versus the measurement frequency for a) long device and b) short device.

#### 2.2.4 HEMT Modeling

#### 2.2.4.1 Basic Small-Signal Model

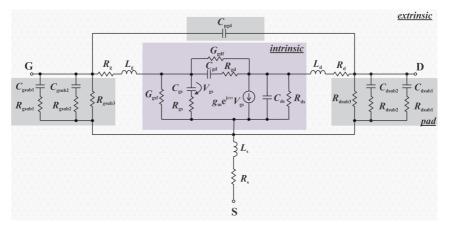

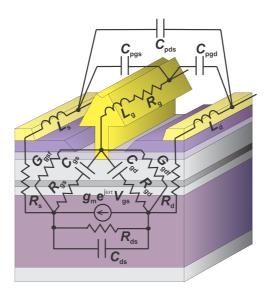

To design a microwave circuit such as an LNA, it is necessary to have an accurate device model that can reproduce measured S-parameters at a desired temperature. Most commonly used model is the Small-Signal Equivalent Circuit (SSEC) which describes the RF performance of a device for a discrete DC bias point. Being the link between physical features of the transistor structure and its electrical circuit representation, the SSEC allows analysis and provides insight into device behavior at high frequencies. A physically representative SSEC can give indications for device optimization, allows predictions for frequencies beyond measurement setup range and can be used for device scaling due to the close connection between the device's geometry and individual elements of the model. In general, the SSEC shown in figure 2.10 can be divided into two parts, extrinsic and intrinsic, where the extrinsic circuit also includes the contact pads. If the contribution of the pads has been deembedded, as explained in section 2.2.3.2, parallel branches with series capacitors and resistors,  $C_{g,dsubi}$  and  $R_{g,dsubi}$ , are replaced with two small capacitances to the ground  $C_{pgs}$  and  $C_{pds}$ . Figure 2.11 shows the physical origin of the SSEC elements presented in figure 2.10 (with deembedded contribution of the contact pads). All elements of the Small-Signal Extrinsic Equivalent Circuit (SSEEC) and Small-Signal Intrinsic Equivalent Circuit (SSIEC) can be extracted from the measured S-parameters. SSEEC elements are extracted when the device is in the cold FET mode with  $V_{\rm ds} = 0$ , and SSIEC elements are extracted when  $V_{\rm ds} > 0$  after the elements of the SSEEC have been mathematically removed from the measured data. Extraction routine of the SSEEC used in this work is described in detail in [28]. The method used to extract the SSIEC is based on the extended Berroth model [29].

FIGURE 2.10: Small-signal equivalent circuit of the InP HEMT consisting of extrinsic and intrinsic part as described in [28].

The SSEEC elements are bias-independent and are determined by the device's physical structure and properties such as the device size, geometrical shape, contact resistance etc. Measurement pads are modeled by several parallel branches with resistors and capacitors in series, while coupling between gate and drain contact pads is modeled by capacitance  $C_{pgd}$ . The extrinsic inductances  $L_{g}$ ,  $L_{s}$  and  $L_{d}$  model the inductive behavior of the gate, source and drain contacts. While  $L_{g}$  and  $L_{d}$  increase with increasing the device width,  $L_{s}$  decreases as a result of broadening the outer source pads. The extrinsic resistances  $R_{g}$ ,  $R_{s}$  and  $R_{d}$  model the resistive behavior of the respective contacts and access resistances. Whereas  $R_{s}$  and  $R_{d}$  are

FIGURE 2.11: Physical origin of the small-signal equivalent circuit elements of the InP HEMT depicted in figure 2.10.

mostly determined by the Ohmic contact resistance,  $R_{\rm g}$  is determined by the resistance of the gate metalization, and a special process monitor is required for its extraction [28].  $R_{\rm g}$  scales linearly with gate width, while  $R_{\rm s}$ and  $R_{\rm d}$  are inversely proportional to the gate width.

The SSIEC elements depend on the selected bias point and describe the behavior of the 2DEG in the active area of the device. The gain mechanism of the HEMT is modeled by a voltage controlled current source with a maximum transconductance  $g_{\rm m}^{\rm max}$ :

$$g_{\rm m}^{\rm max} = \frac{v_{\rm sat} \cdot \epsilon_0 \cdot \epsilon_{\rm 2DEG}}{d} \tag{2.12}$$

reached when electrons in the channel travel with the effective saturation velocity  $v_{\text{sat}}$ .  $g_{\text{m}}^{\text{max}}$  is inversely proportional to the physical distance between gate foot metal and the channel d.  $\tau$  and  $R_{\text{ds}}$  represent the transit time of the electrons underneath the gate and the output resistance, respectively. The capacitance  $C_{\text{gs}}$  accounts for the change of carrier density in the channel with

respect to the change of  $V_{gs}$ . The maximum value of  $C_{gs}$  can be assumed to correspond to the geometrical capacitance between gate foot and the channel:

$$C_{\rm gs} = \frac{l_{\rm G} \cdot \epsilon_0 \cdot \epsilon_{\rm 2DEG}}{d} \tag{2.13}$$

where  $l_{\rm G}$  is the gate length.  $C_{\rm gs}$  is also inversely proportional to the physical distance between gate foot metal and the channel *d*.  $C_{\rm ds}$  represents the capacitance between source and drain electrodes.  $C_{\rm gd}$  is the gate-drain feedback capacitance, representing the change of 2DEG density with the change of  $V_{\rm ds}$ , depending strongly on gate-to-drain distance.  $R_{\rm gs}$  and  $R_{\rm gd}$  account for the intrinsic gate contact resistance and gate-drain feedback resistance, respectively.  $G_{\rm gsf}$  and  $G_{\rm gdf}$  model the non-zero leakage current between the gate-source and gate-drain contacts, respectively. As a first approximation, it can be considered that intrinsic capacitances and the transconductance scale linearly with gate width, while intrinsic resistances are reverse proportional with respect to the device width. Both  $f_{\rm T}$  and  $f_{\rm max}$  as defined is section 2.2.3.1 can now be expressed using the small-signal model element values as follows:

$$f_{\rm T} = \frac{g_{\rm m}}{2\pi} \cdot \frac{1}{(C_{\rm gs} + C_{\rm gd}) \cdot (1 + \frac{R_{\rm s} + R_{\rm d}}{R_{\rm ds}}) + g_{\rm m} \cdot C_{\rm gd} \cdot (R_{\rm s} + R_{\rm d})}$$

(2.14)

$$f_{\text{max}} = \frac{f_{\text{T}}}{2\sqrt{\frac{R_{\text{g}} + R_{\text{s}} + R_{\text{gs}}}{R_{\text{ds}}} + 2 \cdot \pi \cdot f_{\text{T}} \cdot C_{\text{gd}} \cdot R_{\text{g}}}}.$$

(2.15)

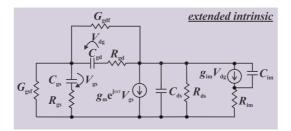

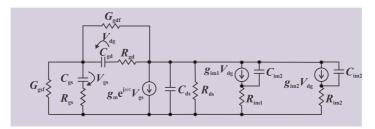

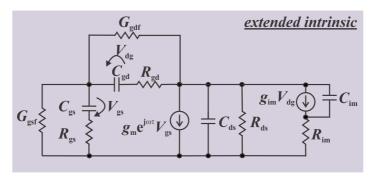

#### 2.2.4.2 Extended Small-Signal Model

According to equations 2.14 and 2.15, to further improve the RF performance of InP HEMTs it is necessary to increase the transconductance  $g_{\rm m}$ while decreasing the parasitic resistances and capacitances. Using a narrow bandgap channel material, such as In-rich GaInAs, will provide higher carrier mobility and saturation velocity and thereby also higher  $g_{\rm m}$ . However, at high drain-source voltages, narrow bandgap channels suffer from impact ionization effects which degrade transistor DC, RF and noise performance. For high In-content or pure InAs channel, the onset of impact ionization can be even at a relatively low drain voltage of  $V_{\rm DS} = 0.5$  V which is close to the

23

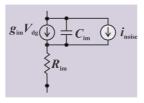

typical low-noise bias point. Impact ionization has been reported to cause an inductive drain impedance due to the phase lag between the drain-source voltage and the impact ionization current, as well as a reduced transmission coefficient  $S_{21}$  due to reduced output resistance at low frequencies [30] [31]. To model the electron-hole pair generation due to impact ionization, an additional voltage-controlled current source is added in the output circuit of the transistor's small-signal model [30] as depicted in figure 2.12.

FIGURE 2.12: Intrinsic small-signal equivalent circuit including circuitry modeling impact ionization.

The added current source is controlled by the intrinsic drain-gate voltage  $V_{\rm dg}$ , with transconductance  $g_{\rm im}$ , while its frequency dependence is modeled with a series  $R_{\rm im}C_{\rm im}$  circuit parallel to the output resistance  $R_{\rm ds}$ . Additional impact ionization modeling elements were determined using a numerical fitting method following the extraction of the basic SSEC as described in [28]. The fitting method used included applying a constrained nonlinear optimization to find the minimum of the difference between measured and modeled imaginary part of intrinsic  $Y_{12,i} + Y_{22,i}$  for the selected frequency range. According to figure 2.12, and as shown in appendix A1, the model  $Y_{12,i} + Y_{22,i}$  is calculated as:

$$Y_{12,i} + Y_{22,i} = \frac{1 + j \cdot \omega \cdot R_{\mathrm{ds}} \cdot C_{\mathrm{ds}}}{R_{\mathrm{ds}}} + \frac{g_{\mathrm{im}}}{1 + j \cdot \omega \cdot R_{\mathrm{im}} \cdot C_{\mathrm{im}}} \cdot \frac{1}{1 + j \cdot \omega \cdot R_{\mathrm{dg}} \cdot C_{\mathrm{dg}}}$$

(2.16)

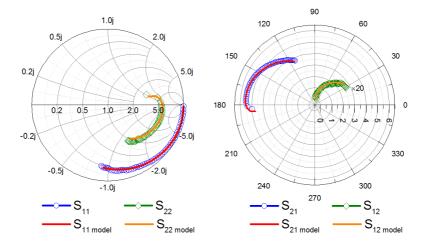

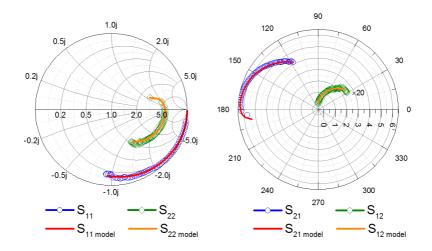

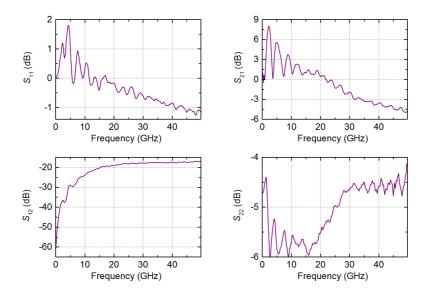

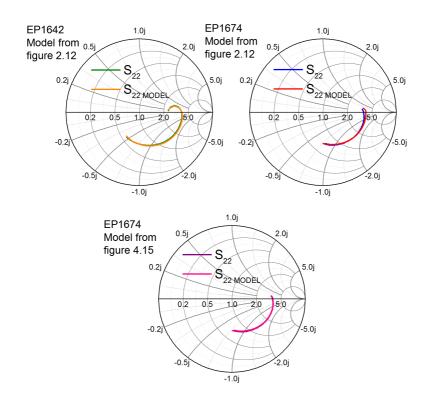

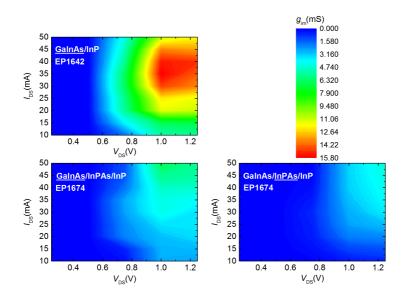

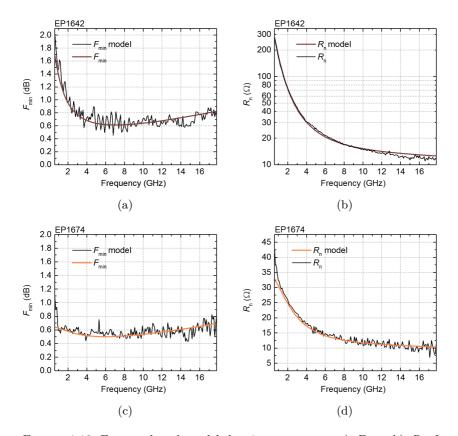

With respect to device size, transconductance  $g_{\rm im}$  scales linearly with device width, while the impact ionization time constant  $\tau_{\rm im} = (R_{\rm im} \cdot C_{\rm im})$  remains invariant. Because impact ionization is manifested in the low frequency measurements, the range used for extraction of additional elements was set to 0.05-10 GHz. The S-parameter measurement sweep included larger number of frequency points in the low frequency range to ensure good resolution for accurate extraction of the impact ionization related elements. The modeled and measured S-parameters for an InP HEMT (with deembedded contact pads) at a bias point where impact ionization is manifested are depicted in figures 2.13 (300 K) and 2.14 (15 K) and show a good agreement for both temperatures. Measured device was fabricated on standard structure detailed in section 3.1, featuring GaInAs channel, therefore the bias point used to demonstrate the effects of impact ionization had high drain voltage of  $V_{\rm DS} = 1$  V. The corresponding elements of the small-signal circuit are listed in table 2.1.

FIGURE 2.13: Measured and modeled S-parameters for a  $2 \times 25 \,\mu\text{m}$  HEMT measured at 300 K with  $V_{\text{DS}} = 1 \,\text{V}$  and  $V_{\text{GS}} = 0.3 \,\text{V}$ . Frequency range is 50 MHz to 50 GHz.

FIGURE 2.14: Measured and modeled S-parameters for a  $2\times25\,\mu{\rm m}$  HEMT measured at 15 K with  $V_{\rm DS}=1\,{\rm V}$  and  $V_{\rm GS}=0.3\,{\rm V}.$  Frequency range is 50 MHz to 50 GHz.

| Parameter     | Value at $300 \mathrm{K}$ | Value at 15 K      | Parameter    | Value at $300 \mathrm{K}$ | Value at 15 K           |

|---------------|---------------------------|--------------------|--------------|---------------------------|-------------------------|

| $R_{\rm s}$   | $4.03\Omega$              | $2.9\Omega$        | $R_{\rm gs}$ | $3.8\Omega$               | $1.14\Omega$            |

| $R_{\rm d}$   | $4.14\Omega$              | $3.2\Omega$        | $R_{\rm gd}$ | $22 \Omega$               | $21.4\Omega$            |

| $R_{\rm g}$   | $0.89\Omega$              | $0.17\Omega$       | $R_{\rm ds}$ | $238\Omega$               | $243\Omega$             |

| $L_{\rm s}$   | $0.17\mathrm{pH}$         | $0.16\mathrm{pH}$  | $C_{gs}$     | $47.5\mathrm{fF}$         | $45.9\mathrm{fF}$       |

| $L_{\rm d}$   | $7.1\mathrm{pH}$          | $7.71\mathrm{pH}$  | $C_{\rm gd}$ | $6.58\mathrm{fF}$         | $6.25\mathrm{fF}$       |

| Lg            | $10.8\mathrm{pH}$         | $10.1\mathrm{pH}$  | $C_{\rm ds}$ | $15.9\mathrm{fF}$         | $9.89\mathrm{fF}$       |

| $C_{pgd}$     | $0.28\mathrm{fF}$         | $0.22\mathrm{pF}$  | $g_{\rm m}$  | $90.7\mathrm{mS}$         | $95.3\mathrm{mS}$       |

| $C_{\rm pd}$  | $0.4\mathrm{fF}$          | $0.26\mathrm{pF}$  | $\tau$       | $60\mathrm{fsec}$         | $137\mathrm{fsec}$      |

| $C_{\rm pg}$  | $0.8\mathrm{fF}$          | $0.12\mathrm{pF}$  | $g_{ m im}$  | $6.23\mathrm{mS}$         | $6.54\mathrm{mS}$       |

| $G_{gsf}$     | $4\mu S$                  | $1\mu\mathrm{S}$   | $C_{\rm im}$ | $1.67\mathrm{fF}$         | $11.4\mathrm{fF}$       |

| $G_{\rm gdf}$ | $8\mu\mathrm{S}$          | $2.4\mu\mathrm{S}$ | $R_{\rm im}$ | $138\mathrm{k}\Omega$     | $27.1 \mathrm{k}\Omega$ |

TABLE 2.1: Extracted SSEC element values for a  $2\times25\,\mu{\rm m}$  HEMT measured at 300 and 15 K with  $V_{\rm DS}=1\,{\rm V}$  and  $V_{\rm GS}=0.3\,{\rm V}.$

### 2.2.5 Noise Characterization

#### 2.2.5.1 Noise Metrology

Beside amplifying both the signal and the noise presented at their input, all amplifying devices add extra noise generated within, and degrade the SNR ratio at their output. InP HEMTs add exceptionally low noise powers to the input signal due to their superior transfer properties and minimal parasitic resistances and are therefore very attractive for low-noise applications. To describe the SNR degradation for a signal passing through a device, a frequency dependent noise figure is used. Noise figure is a function of the input (source) admittance and of four independent noise parameters:

$$F = F_{\min} + 4 \cdot \frac{R_{n}}{Z_{0}} \cdot \frac{|\Gamma_{s} - \Gamma_{opt}|^{2}}{|1 + \Gamma_{opt}|^{2} \cdot (1 - |\Gamma_{s}|^{2})}.$$

(2.17)

Noise parameters describe how the noise figure changes as a function of the source reflection coefficient  $\Gamma_{\rm s}$ . For each frequency, there is an optimum input reflection  $\Gamma_{\rm s} = \Gamma_{\rm opt}$  coefficient where the minimum noise figure  $F_{\rm min}$  is achieved. The noise resistance  $R_{\rm n}$  characterizes how rapidly the noise figure changes from  $F_{\rm min}$  when the input impedance is diverging from optimum, whereas  $Z_0$  represent the characteristic impedance of a measurement setup (usually 50  $\Omega$ ). To characterize low noise devices it is also common to use the effective noise temperature,  $T_{\rm e}$ , instead of the noise figure. The effective noise temperature is related to the noise figure with the following expression:

$$T_{\rm e} = (F - 1) \cdot T_0 \tag{2.18}$$

where  $T_0$  is the reference temperature of 290 K.

To obtain the four noise parameters, at least four noise figure measurements corresponding to four different source reflection coefficients, adequately distributed over the Smith-chart, are needed. Usually, more than four terminations, provided by impedance tuners, are used to produce an overdetermined system of equations and minimize errors. Different techniques can later be used to extract the four noise parameters from the measured data. Besides direct extraction of the noise parameters from measurements, it is possible to use transistor's noise model to fit the modeled and measured data, and later use the model to predict the noise

27

performance. The noise model is usually based on the SSEC, together with different number of elements/parameters used for fitting the measured and modeled data. This method has been validated even if only one noise figure measurement, corresponding to one source impedance  $(50 \Omega)$ , was available [32] [33]. However, this approach relies highly on accuracy of the used noise model, and a very good match between the measured and modeled *S*-parameters is a prerequisite.

Several semi-empirical device noise models based on extracted SSEC elements and appropriate fitting factors can be used [34] [35] [36] to simulate the noise performance of InP HEMTs when designing an LNA. In this work, noise modeling was performed using the SSEC as described in section 2.2.4 and using Pospiezalski's method [35]. In Pospiezalski's method, the device parasitic resistances contribute only to the thermal noise, while noise properties of the intrinsic chip are treated by assigning effective temperatures to gate ( $T_g$ ) and drain ( $T_d$ ).  $T_g$  is usually set to ambient temperature while  $T_d$  is used as a free parameter for fitting the modeled performance with measured noise figures.

There are two basic approaches used to measure the noise figure of a two port network: the Y-factor and cold-source (or direct) method [37]. While the Y-factor technique obtains the noise figure by measuring the noise powers for two different noise levels at the input (hot and cold), the cold-source approach requires only measurement of one noise power corresponding to a single noise level (cold) at the input. However, in cold-source approach usage of both hot and cold states of the noise source is required for the calibration of the noise receiver. Although direct approach is more complex since it requires device's available gain and the gain-bandwidth product of the receiver to be previously determined by a separate measurement, it provides more accuracy than the Y-factor method when measuring single transistors. The Y-factor method adds systematic errors due to different reflection coefficients for the noise source in the hot and cold states, and due to generally poor matching of the device's output and the noise receiver.

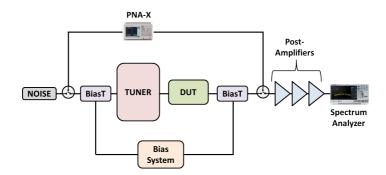

## 2.2.5.2 Noise Measurements

Noise measurements presented in this work were performed at room temperature, using the Maury Microwave ATS software v536.04 controlling the N5245A PNA-X, the HP4142 parameter analyzer, the noise receiver, the MT984AU automated tuner (8-50 GHz), HP87222E input and output switches and a 346CK01 noise source. The noise receiver was implemented with a cascade of three low-noise amplifiers and a spectrum analyzer unless noted otherwise. Test setup for the noise measurements is depicted in figure 2.15. Noise modeling and simulations presented in this work were performed using the Keysight's Advanced Design System (ADS) software.

FIGURE 2.15: Block diagram of the noise measurement setup.

For noise characterization, devices were measured over the 8-50 GHz frequency range at room temperature using the cold-source method unless noted otherwise. The noise figure of the device was obtained using following calculations based on measured S-parameters for the tuner and for the device, measured noise power  $P_{\text{COLD}}$  and measured output reflection coefficient of the noise source  $\Gamma_{\text{NS,COLD}}$ :

$$F = 1 + G_{\text{TUN}} \cdot \left(\frac{P_{\text{COLD}}}{G_{\text{REC}} \cdot G_{\text{AV}} \cdot MM} - \frac{F_{\text{REC}} - 1}{G_{\text{AV}}} - \frac{T_{\text{COLD}}}{T_0} + 1 - F_{\text{TUN}}\right)$$

(2.19)

where  $T_{\text{COLD}}$  is the ambient temperature, and  $T_0 = 290 \text{ K}$ .  $F_{\text{TUN}}$  and  $G_{\text{TUN}}$  are the tuner noise factor and gain:

$$F_{\rm TUN} = 1 + \left(\frac{1}{G_{\rm TUN}} - 1\right) \cdot \frac{T_{\rm COLD}}{T_0},$$

(2.20)

$$G_{\rm TUN} = \frac{1 - |\Gamma_{\rm NS,COLD}|^2}{|1 - S_{11,\rm TUN} \cdot \Gamma_{\rm NS,COLD}|^2} \cdot |S_{21,\rm TUN}|^2 \cdot \frac{1}{1 - |\Gamma_{\rm s,DUT}|^2}, \quad (2.21)$$

$$\Gamma_{\rm s,DUT} = S_{22,\rm TUN} + \frac{S_{21,\rm TUN} \cdot S_{12,\rm TUN} \cdot \Gamma_{\rm NS,\rm COLD}}{1 - S_{11,\rm TUN} \cdot \Gamma_{\rm NS,\rm COLD}}.$$

(2.22)

$F_{\rm REC}$  and  $G_{\rm REC}$  are the receiver noise figure and gain obtained during receiver calibration:

$$F_{\text{REC}} = F_{\text{min,REC}} + 4 \cdot \frac{R_{\text{n,REC}}}{Z_0} \cdot \frac{|\Gamma_{\text{s,REC}} - \Gamma_{\text{opt,REC}}|^2}{|1 + \Gamma_{\text{opt,REC}}|^2 \cdot (1 - |\Gamma_{\text{s,REC}}|^2)}, \quad (2.23)$$

$$\Gamma_{\rm s,REC} = S_{22,\rm DUT} + \frac{S_{21,\rm DUT} \cdot S_{12,\rm DUT} \cdot \Gamma_{\rm s,\rm DUT}}{1 - S_{11,\rm DUT} \cdot \Gamma_{\rm s,\rm DUT}}.$$

(2.24)

$G_{\rm AV}$  is the available gain of the cascade network of the device and the tuner, and MM is the mismatch between the device and the receiver:

$$MM = \frac{1 - |\Gamma_{\rm s,REC}|^2}{|1 - S_{11,\rm REC} \cdot \Gamma_{\rm s,REC}|^2}.$$

(2.25)

The procedure for noise characterization was as follows:

- The device was inserted in the noise measurement setup and *S*-parameters were measured for a selected bias point.

- The small-signal model was extracted from measured S-parameters.

- The noise figure was measured using the cold-source approach with 34 different impedances presented to the input of the device.

- The drain temperature  $T_{\rm d}$  was determined by varying its value until the difference between the simulated noise figure of extracted SSEC and measured noise figure for all 34 input impedances is minimized.

- Using the Pospiezalski's noise model, a small-signal simulation generates a complete set of four noise parameters.

Noise measurements, besides requiring a complex setup, are time consuming since they require several calibration steps, frequency sweeps for all tuner states and all bias points, model extractions, optimizations and simulations thus making characterization of each single transistor not practical. However, from the measured DC and RF performance it is possible to estimate to a certain extent the noise behavior of a device and preselect the most promising ones for noise measurements. Using Pospiezalski's noise model, an expression for the minimum noise temperature, omitting the influence of gate leakage current, is given as:

$$T_{\min} \approx 2 \cdot \frac{f}{f_{\mathrm{T}}} \cdot \sqrt{r_{\mathrm{t}} \cdot T_{\mathrm{g}} \cdot g_{\mathrm{ds}} \cdot T_{\mathrm{d}}}$$

(2.26)

where  $g_{\rm ds}$  is the output conductance and  $r_{\rm t} = R_{\rm s} + R_{\rm g} + R_{\rm gs}$ . Taking into account that only  $T_{\rm d}$  and  $f_{\rm T}$  are strong functions of transistor bias, with  $T_{\rm d}$ almost linearly depending on the drain current, the minimum noise temperature can be obtained for transistor bias where the value of

$$\frac{\sqrt{I_{\rm ds}}}{g_{\rm m}} \tag{2.27}$$

is minimized. Therefore, a low-noise HEMT should have high transconductance achieved at low drain-source current. Expression given in 2.27 is usually referred to as the Noise Indication Factor (NIF), and its minimum value can be used as one of the figures-of-merit to predict the noise performance. The RF transconductance  $g_{\rm m}$ , used in expression 2.27, and intrinsic DC transconductance  $g_{\rm M,intr}$  are comparable, with differences arising from impact ionization and charge trapping effects affecting only DC  $g_{\rm M,intr}$ . Improvement resulting from device or epitaxial optimization can be observed in both transconductances when biased away from regions where additional carriers are generated or trapped. Because the extrinsic  $g_{\rm M}$  and intrinsic  $g_{\rm M,intr}$  are correlated by following equation:

$$g_{\rm M} = \frac{g_{\rm M,intr}}{1 + g_{\rm M,intr} \cdot R_{\rm s}},\tag{2.28}$$

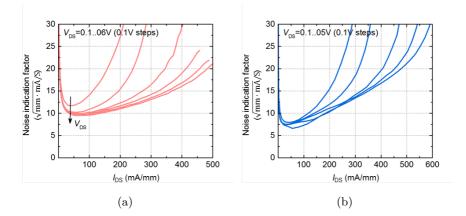

it is justified to use the DC extrinsic  $g_{\rm M}$  instead of  $g_{\rm m}$  to roughly evaluate NIFs for different devices. NIF can be used to compare devices with similar geometry; any change in vertical dimensions will not be properly reflected in the value of expression 2.27 since it does not include capacitances which have a large influence on  $f_{\rm T}$ . In figure 2.16a, the NIF versus drain current is shown for a 2 × 25 µm device from figure 2.4. A minimum is visible for  $I_{\rm DS}$  between 50 and 100 mA/mm, and  $V_{\rm DS} \approx 0.5$  V. At cryogenic temperatures, as a consequence of reduced resistances and increased  $g_{\rm m}$ , NIF is decreasing and optimum bias point is moving towards lower drain current as depicted in figure 2.16b. The optimum  $I_{\rm DS}$  at cryogenic temperatures is below 50 mA/mm with  $V_{\rm DS} \approx 0.5$  V.

FIGURE 2.16: Noise indication factor for a  $2 \times 25 \,\mu\text{m}$  HEMT with 100 nm gate length a) measured at 300 K and b) measured at 15 K.

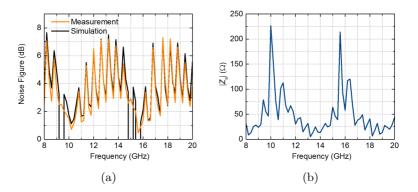

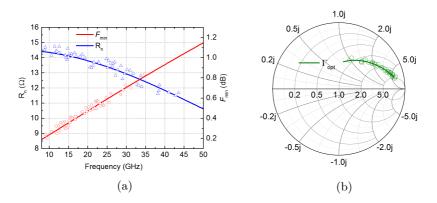

Typical noise measurement data and simulation of the extracted noise model from 8-20 GHz are depicted in figure 2.17a for one arbitrary impedance tuner state. Device in figure 2.17a is a  $2 \times 25 \,\mu\text{m}$  InP HEMT, the same device from figure 2.4, biased close to optimum low-noise bias point of  $V_{\rm DS} = 0.5 \,\text{V}$  and  $I_{\rm DS} = 100 \,\text{mA/mm}$ . Extracted drain temperature for this bias point is  $T_{\rm d} = 2153 \,\text{K}$ . Measurements and simulation show similar and good fit for all tuner states. The shape of measured noise figure has a characteristic form versus frequency due to the source impedance,  $Z_{\rm s}$ , varying with frequency as shown in figure 2.17b. The extracted and modeled noise parameters are shown in figure 2.18.

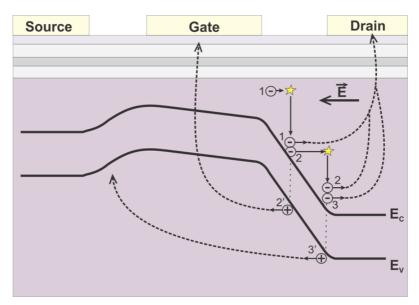

On the path to circuits operating at THz frequencies an increase of the transconductance  $g_{\rm m}$  is required, together with reduction of the parasitics resistances and capacitances by scaling the lateral and vertical HEMT dimensions. Common approach, as stated in section 2.2.4.2, is to use the narrower bandgap material for the channel such as In-rich GaInAs or pure InAs. However, while the device frequency performance will improve, the noise performance will suffer due to the optimum low-noise bias point potentially located close or at the onset of impact ionization. Along the collaboration with *Centro Astronómico de Yebes* and *ESA*, increased low-frequency noise was observed in devices with InAs/GaInAs channels compared to the devices

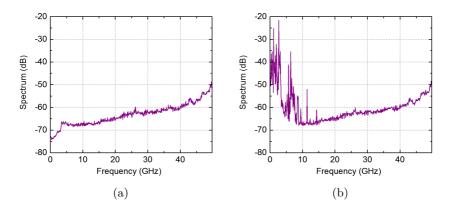

FIGURE 2.17: a) Measured and modeled noise figure for a  $2 \times 25 \,\mu\text{m}$  HEMT at  $300 \,\text{K}$  with  $V_{\text{DS}} = 0.5 \,\text{V}$  and  $I_{\text{DS}} = 100 \,\text{mA/mm}$ . b) Magnitude of the source impedance,  $|Z_{\text{s}}|$ , presented to the device.

FIGURE 2.18: Extracted and modeled noise parameters a)  $F_{\rm min}$  and  $R_{\rm n}$ and b)  $\Gamma_{\rm opt}$  for a 2 × 25 µm HEMT measured at 300 K with  $V_{\rm DS} = 0.5$  V and  $I_{\rm DS} = 100$  mA/mm. Extracted  $T_{\rm d} = 2153$  K.

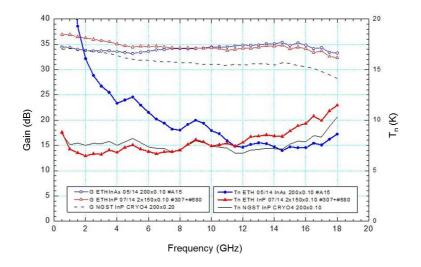

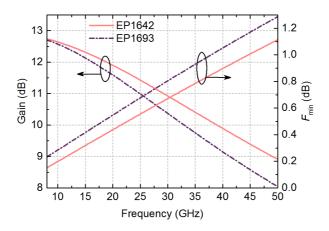

with conventional GaInAs channel. During the testing procedure devices were inserted in the first stage of the hybrid wide-band amplifier and their gain and effective noise temperature were measured at 15 K. In figure 2.19 a comparison for three different devices, all biased with equal  $V_{\rm DS}$  and  $I_{\rm DS}$ , is shown:

- $2 \times 100 \,\mu\text{m}$  HEMT with GaInAs channel from NGST,

- +  $2\times100\,\mu\mathrm{m}$  HEMT with 1 nm InAs inserted in GaInAs channel from ETH,

- $2 \times 150 \,\mu\text{m}$  HEMT with GaInAs channel from ETH.

FIGURE 2.19: Gain and effective noise temperature for various HEMTs measured at 15 K biased at the same bias point. Graph obtained from *Centro Astronómico de Yebes*.

For the device with InAs channel inset, a large increase in noise temperature  $T_{\rm n}$  can be observed below 10 GHz. The shape of elevated low frequency noise was similar as reported in [38], where it was attributed to impact ionization as a result of increased  $V_{\rm DS}$ . In figure 2.19, all three devices were biased with the same  $V_{\rm DS}/I_{\rm DS}$ , however, due to the InAs inset in the channel, onset for impact ionization was at lower  $V_{\rm DS}$  compared to devices with a GaInAs channel. The InAs channel inset device was the only one showing signs of impact ionization at the selected bias point, and it was also the only one exhibiting impaired noise performance.

The observed behavior could not be clearly identified or modeled using the noise figures obtained in the standard way described in this section. To investigate if the worse performance in fact impact ionization related, and whether it is possible to model it using the small-signal circuit as described in section 2.2.4.2, additional measurements were done in the low frequency range. Low frequency measurements were performed over 0.8-18 GHz range, with the same measurement setup from figure 2.15 but using a low frequency impedance tuner MT982BU (0.8-18 GHz) instead of MT984AU. For this frequency range the Maury MT7553 module was used as the noise receiver.

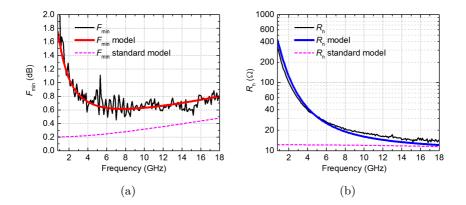

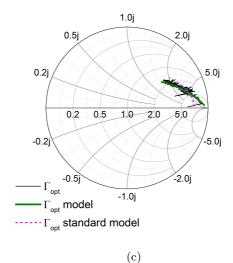

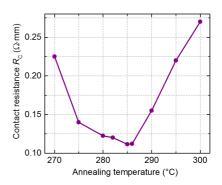

Measurements were performed on a device with GaInAs channel, the same shown for 8-50 GHz range in figures 2.17 and 2.18, to exclude any unknown effect arising from the InAs channel. The device was biased at  $V_{\rm DS} = 1 \,\rm V$ and  $I_{\rm DS} = 100 \,\rm mA/mm$ , a bias point where measured S-parameters showed the onset of impact ionization. The noise parameters  $(F_{\rm min}, R_{\rm n} \text{ and } \Gamma_{\rm opt})$ , extracted from measurements by the Maury software, were used to fit the model and measured data from over 0.8-18 GHz range as opposed to the total measured noise figure (F) which was used to fit the measurements over 8-50 GHz range. Noise parameters extracted from measurements, and noise parameters obtained from the standard and extended model including impact ionization are depicted in figure 2.21. Both the minimum noise figure  $F_{\rm min}$  and the noise resistance  $R_{\rm n}$  extracted from measurements show a large increase at lower frequencies, similar to what was observed in figure 2.19 for a device with an InAs channel inset.

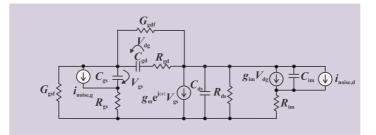

In order to fit the device model to the noise measurements shown in figure 2.21, an additional ideal white noise source had to be added to the noise model based on the extended SSEIC described in section 2.2.4.2. The additional current noise source  $i_{\text{noise}}$  accounting for noise generated by impact ionization was added parallel to the  $g_{\text{im}}$  and  $C_{\text{im}}$  as depicted in figure 2.20.

FIGURE 2.20: White noise source added to the device noise model representing the noise generated by impact ionization.

FIGURE 2.21: Extracted and modeled noise parameters a)  $F_{\rm min}$ , b)  $R_{\rm n}$  and c)  $\Gamma_{\rm opt}$  for a 2 × 25 µm HEMT measured at 300 K with  $V_{\rm DS} = 1$  V and  $I_{\rm DS} = 100$  mA/mm.

The frequency behavior of the added current noise source is given as:

$$i_{\rm im} = \frac{i_{\rm noise}}{\sqrt{1 + (\omega \cdot R_{\rm im} \cdot C_{\rm im})^2}}$$

(2.29)

due to the arrangement of the  $i_{\text{noise}}$  and the  $R_{\text{im}}C_{\text{im}}$  circuit. However, because of the significant increase in the gate current from holes generated by impact ionization, just adding  $i_{\text{noise}}$  to the noise model was not sufficient to fit all four noise parameters. To account for the increased gate leakage and its influence on the noise, the effective temperature of the resistances at the gate side ( $R_{\text{gs}}$ ,  $R_{\text{gd}}$ ,  $G_{\text{gsf}}$  and  $G_{\text{gdf}}$ ) had to be increased to  $T_{\text{im}}$ , similar as in [30]. In [30], three different noise temperatures and a white noise source were used for modeling, where the third temperature accounts for the gate leakage resulting from electrons tunneling through the barrier to the gate. The measured device, depicted in figure 2.21, had low gate leakage (order of magnitude lower compared to [30]), hence it was not necessary to add the third noise temperature to the model. Optimized values of  $T_{\rm d}$ ,  $T_{\rm im}$  and  $i_{\rm noise}$ for the device depicted in figure 2.21 are:

$$T_{\rm d} = 7661 \,{\rm K},$$

$T_{\rm im} = 951 \,{\rm K},$

$i_{\rm noise} = 377.5 \,{\rm pA}.$

They were obtained by tuning and optimizing their values to minimize the difference between extracted and simulated noise parameters using the least-squares error function built in the ADS Gradient Optimizer. From figure 2.21 it can be observed that the model which includes impact ionization circuit is capable of replicating low frequency behavior of noise parameters, whereas the standard model fails.

Another possibility for fitting the noise parameters when impact ionization is detected is to use two noise sources: one at the gate side and one on the drain side, as shown in figure 2.22. In that case, the increase of the effective temperature on the gate side was not necessary because the added white noise source models the effect that the increased gate current has on the noise figure. The optimized values of the circuit elements in this case are:

$$T_{\rm d} = 6840 \,\mathrm{K},$$

$$i_{\rm noise,d} = 407.5 \,\mathrm{pA},$$

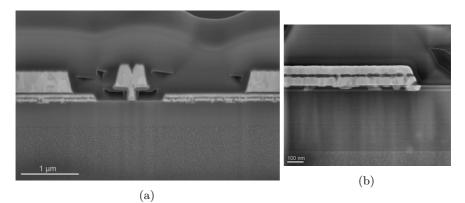

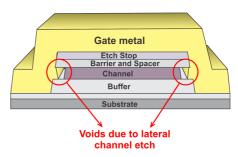

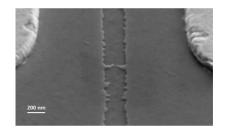

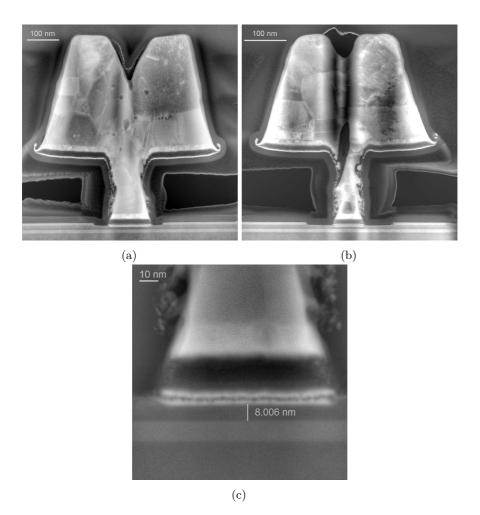

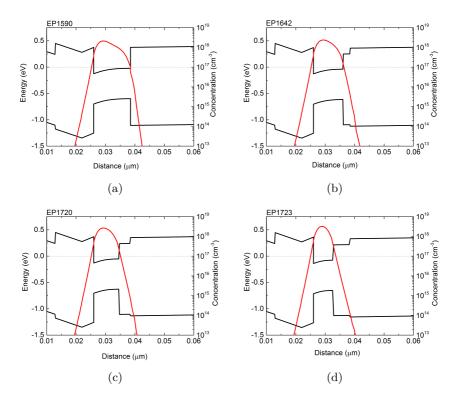

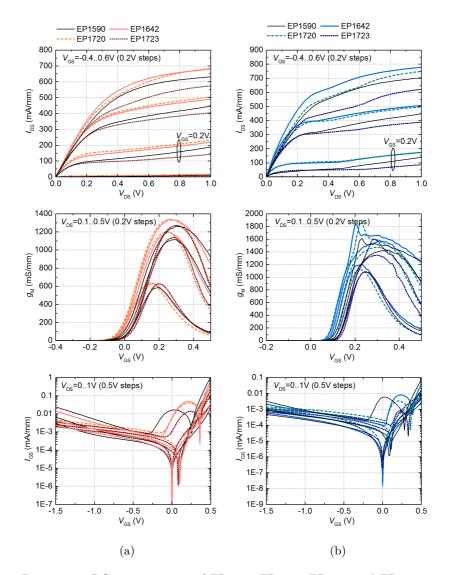

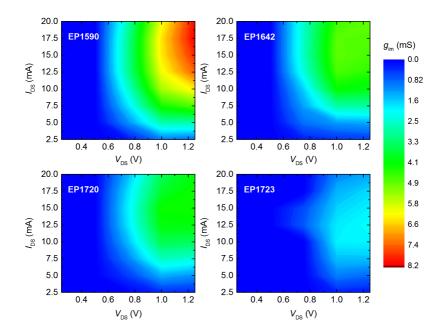

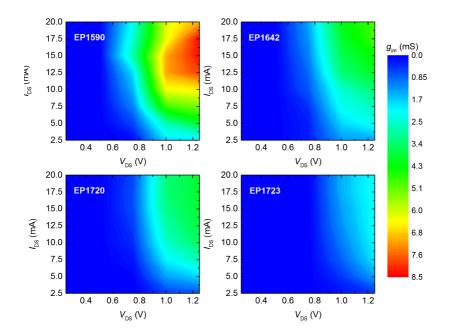

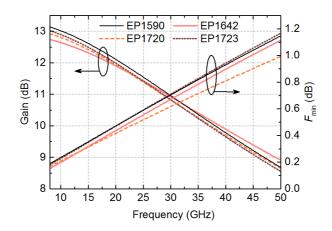

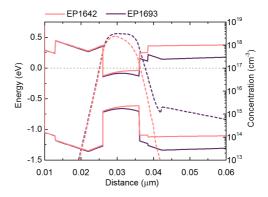

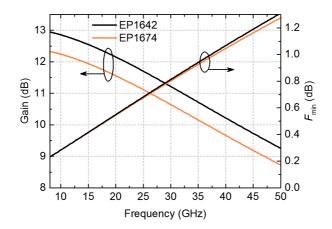

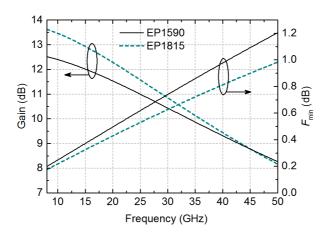

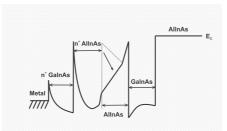

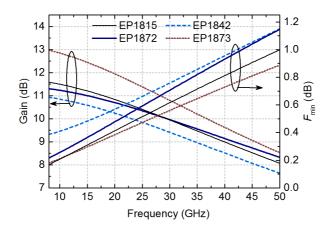

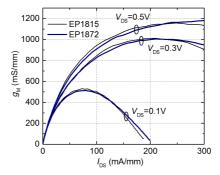

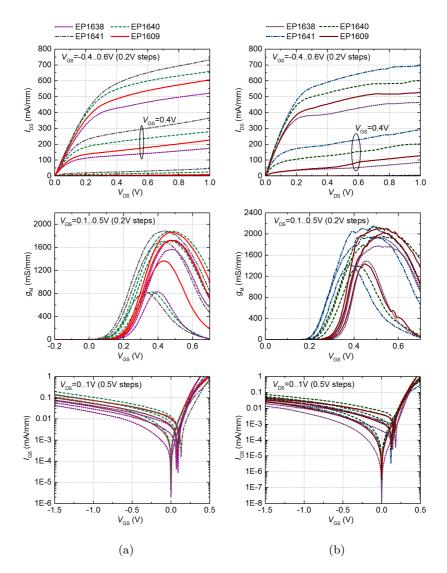

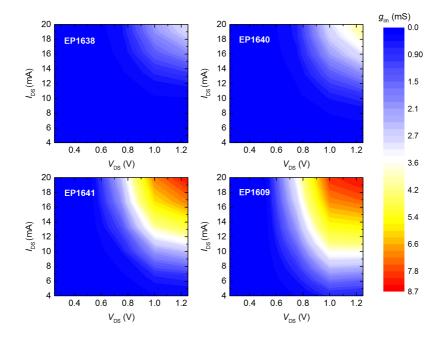

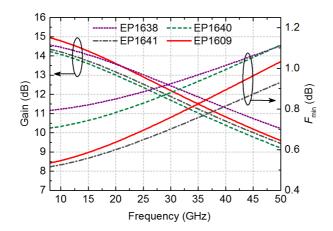

$$i_{\rm noise,g} = 1.7 \,\mathrm{pA}.$$