# Optical absorption in silicon layers in the presence of charge inversion/accumulation or ion implantation

### **Journal Article**

### Author(s):

Alloatti, Luca; Lauermann, Matthias; Sürgers, Christoph; Koos, Christian; Freude, Wolfgang; Leuthold, Juerg (1)

## **Publication date:**

2013-07-29

### Permanent link:

https://doi.org/10.3929/ethz-b-000071826

### Rights / license:

Creative Commons Attribution 3.0 Unported

### Originally published in:

Applied Physics Letters 103(5), https://doi.org/10.1063/1.4817255

# Optical absorption in silicon layers in the presence of charge inversion/accumulation or ion implantation

L. Alloatti, 1,a) M. Lauermann, 1 C. Sürgers, 2 C. Koos, 1 W. Freude, 1 and J. Leuthold 1,3

<sup>1</sup>Institutes IPQ and IMT, Karlsruhe Institute of Technology (KIT), Karlsruhe 76131, Germany

<sup>2</sup>Physikalisches Institut and DFG-Center for Functional Nanostructures, Karlsruhe Institute of Technology, P. O. Box 6980, Karlsruhe 76049, Germany

<sup>3</sup>Institute of Electromagnetic Fields (IFH), ETH Zurich, Zurich, Switzerland

(Received 17 June 2013; accepted 12 July 2013; published online 30 July 2013)

We determine the optical losses in gate-induced charge accumulation/inversion layers at a Si/SiO<sub>2</sub> interface. Comparison between gate-induced charge layers and ion-implanted thin silicon films having an identical sheet resistance shows that optical losses can be significantly lower for gate-induced layers. For a given sheet resistance, holes produce higher optical loss than electrons. Measurements have been performed at  $\lambda = 1550\,\mathrm{nm}$ . © 2013 Author(s). All article content, except where otherwise noted, is licensed under a Creative Commons Attribution 3.0 Unported License. [http://dx.doi.org/10.1063/1.4817255]

Small optical losses are essential for silicon photonics devices. However, for keeping *RC* time constants low and bandwidths high, an increasing number of components, like high-speed electro-optic modulators<sup>2,3</sup> or photodetectors, require highly conductive electrodes, which in turn create high free-carrier absorption (FCA).

Even though there are several methods to increase the conductivity  $(1/\rho)$  of a semiconductor, so far only doping has been considered in silicon photonics. For thin conductive films, the sheet resistance  $R_s = \rho/d$  is the relevant number when the film thickness d is given; the resistance of a sheet of length L and width w then is  $R = R_s L/w$ . However, while the optical loss via free-carrier absorption increases linearly with the doping level, the conductivity grows less than linearly, mainly because of electron-impurity scattering. This confronts designers with a trade-off problem between device speed and insertion loss, properties which both are of primary technological importance. A method for improving the conductivity of silicon structures without an undue increase of optical loss would therefore be highly desirable.

A possible solution for minimizing optical losses while maintaining a high electrical conductivity has recently been suggested. In this publication the bandwidth of a silicon-based modulator has been dramatically increased by exploiting an electron accumulation layer induced by a gate voltage. The optical loss created by such an accumulation layer was very small. However, the optical loss caused by inversion/accumulation layers in silicon has not been measured systematically yet.

In this work we measure the optical absorption caused by electron and hole charge accumulation layers at a silicon/silicon dioxide interface. For equal charge carrier concentrations as a result from either impurity doping, or from free carriers, e.g., accumulated under the influence of an applied electric field, the optical losses are comparable in both cases. However, due to impurity scattering, the electrical conductivity is smaller for doped layers. Thus, for the same

The paper is organized as follows: First, we determine the optical loss in a rib waveguide when a gate voltage is applied. Second, we derive a model for describing such losses. Finally, we compare these losses to published data for ion implantation.

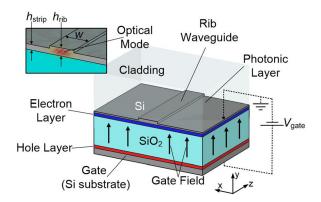

For determining the optical loss of conductive sheets as a function of gate fields, we record the optical transmission of rib waveguides structured on a silicon-on-insulator (SOI) wafer from Soitec, Fig. 1. We measure the transmission as a

FIG. 1. Cross-section of the silicon chip used for optical loss vs. gate field measurements. The waveguide is located on top of a low-refractive index substrate (SiO<sub>2</sub>). The optical quasi-TE<sub>00</sub> mode is mainly confined in the upper lowly-doped (ideally intrinsic) silicon layer, and extends slightly into the silicon-dioxide substrate and into the 0.8  $\mu$ m thick PMMA cladding. A gate voltage ( $V_{\rm gate}$ ) is applied between the silicon substrate and the grounded photonic layer. In the example shown in the picture, the gate voltage is positive, so that a hole charge layer (marked in red) is formed at the interface between gate and oxide, while an electron layer (marked in blue) is formed between the waveguide and the oxide. This electron layer reduces the sheet resistance in the photonic silicon layer, but also increases the optical losses. The rib height is  $h_{\rm rib} = 220\,{\rm nm}$ , the strip height is  $h_{\rm strip} = 150\,{\rm nm}$ , the rib width is  $w = 700\,{\rm nm}$ , and the silicon-oxide thickness is  $d_{\rm SiO_2} = 2\,\mu{\rm m}$ .

conductivities, the concentration of impurity-generated charges must be higher leading to a higher optical loss. By comparing our measurements with published data for doped layers, we show that the optical power attenuation coefficient for field-induced free carriers and given sheet resistance can be up to 3.5 times smaller.

a)Electronic mail: luca.alloatti@kit.edu

function of the gate voltage  $V_{\rm gate}$  applied to the silicon substrate (the photonic layer is electrically grounded). The fundamental quasi-TE $_{00}$  mode of the waveguide is strongly confined to the photonic layer, Fig. 1. The mode couples to external fibers by standard gratings. If the gate field across the silicon dioxide  $E_{\rm gate} = V_{\rm gate}/d_{\rm SiO2}$  is positive (negative), an electron (hole) layer is formed at the Si/SiO $_{2}$  boundary inside the photonic layer, Fig. 1. These charges then lower the sheet resistance of the photonic layer but will also increase the optical losses. Subsequently, we will measure and discuss these losses.

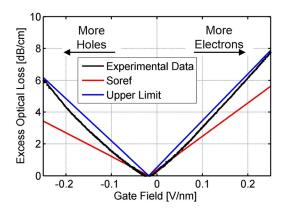

The optical transmission losses have been measured for different waveguide lengths (1, 3, and 10 mm) and the excess optical loss for free-carrier absorption have been extracted, black curve in Fig. 2. As expected, the optical loss increases for large positive or large negative gate fields. The minimum optical loss occurs at  $E_{\rm gate} = -0.018 \, \text{V/nm}$  instead at  $E_{\rm gate} = 0$  or at a slightly positive gate field, as one would expect since silicon has a residual p-type doping. This could be attributed to the presence of the PMMA cladding, but also residual impurities could play a role.  $^{18}$

We now compare the measured loss data in Fig. 2 as induced by applying a gate field with losses predicted due to free carrier absorption with doping. For this we follow Soref. According to Soref the optical power attenuation coefficient at position  $\vec{r}$  due to free carriers increases linearly with the concentration  $N_e$  and  $N_h$  of electrons and holes, respectively,

$$\alpha(\vec{r}) = C_e N_e(\vec{r}) + C_h N_h(\vec{r}). \tag{1}$$

In the case that the free carriers stem from impurity ionization only, the loss constants  $C_e$  and  $C_h$  in Eq. (1) have been empirically determined<sup>4,10</sup> at the wavelength  $\lambda = 1550$  nm,

$$C_e^{(\text{ion})} = 8.5 \times 10^{-22} \,\text{m}^2,$$

(2)

$$C_h^{(\text{ion})} = 6.0 \times 10^{-22} \,\text{m}^2.$$

(3)

FIG. 2. Measured excess optical loss of a rib waveguide as a function of the applied gate field (black line). For large positive (negative) gate fields, an electron (hole) layer forms in the photonic layer, and the optical loss increases. The red curve shows the calculated losses according to Eqs. (1)–(3), which were empirically derived by Soref<sup>4,10</sup> from doping measurements. The blue curve represents our measurements in a linear worst-case approximation.

In contrast to Soref, here the free-carrier concentration in the lowly-doped (ideally intrinsic) photonic layer depends on the gate field. If charges are injected in intrinsic silicon by applying a field, different constants might apply. Because these injected carriers do not experience impurity scattering,<sup>6</sup> optical losses could be smaller. On the other hand, when charges are injected by a gate voltage, charge densities close to  $10^{20}$  cm<sup>-3</sup> can appear in the vicinity of the Si/SiO<sub>2</sub> interface—a concentration regime where electron-electron scattering cannot be neglected.<sup>6</sup> Additionally, also the roughness of the Si/SiO<sub>2</sub> interface might play a role.<sup>11</sup> Therefore it is not clear *a priori* whether Soref's constants overestimate or underestimate the actual loss.

For calculating the waveguide attenuation coefficient  $\alpha_{\rm wg}$  of the quasi-TE<sub>00</sub> mode using Eq. (1), we first define in a Cartesian coordinate (x, y, z)- system (Fig. 1) the electric field components in the corresponding directions denoted by n = (1, 2, 3), and separate a dimensionless complex amplitude A(z) from the modal field  $\mathcal{E}_n(x, y)$ . A monochromatic wave propagating along the z-direction with propagation constant k and an angular frequency  $\omega$  is described by

$$E_n(x, y, z, t) = A(z)\mathcal{E}_n(x, y)e^{i(kz - \omega t)} + cc, \tag{4}$$

$$H_n(x, y, z, t) = A(z)\mathcal{H}_n(x, y)e^{i(kz-\omega t)} + \text{cc.}$$

(5)

In the slowly-varying amplitude approximation it can be shown<sup>12</sup> that the waveguide attenuation coefficient  $\alpha_{\rm wg} = -(1/|A(z)|^2)\partial|A(z)|^2/\partial z$  is given by (vacuum speed of light c, vacuum permittivity  $\epsilon_0$ )

$$\alpha_{\text{wg}} = \frac{\epsilon_0 c}{\int dx dy (\mathcal{E}_1 \mathcal{H}_2 - \mathcal{E}_2 \mathcal{H}_1)} \int dx dy n(x, y) \alpha(x, y) (\mathcal{E}_1^2 + \mathcal{E}_2^2 - \mathcal{E}_3^2),$$

(6)

where n(x,y) and  $\alpha(x,y)$  are the local refractive index and the local attenuation coefficient Eq. (1), respectively. We notice that the last negative sign in Eq. (6) is due to the fact that if  $\mathcal{E}_{1,2}(x,y)$  is chosen to be real, the quantity  $\mathcal{E}_3(x,y)$  will be imaginary.

Next, we substitute Eq. (1) in Eq. (6). Since the charge distribution varies only along y, the local power attenuation coefficient  $\alpha(x,y) = \alpha(y)$  does not depend on x (see coordinate system in Fig. 1). For the gate voltages considered in this work, our simulations<sup>9</sup> show that the electron and hole densities do not exceed  $10^{20}$  cm<sup>-3</sup>. This means that the variation of the silicon refractive index is less than 0.3%, we therefore assume that the refractive index is constant, n(x,y) = 3.48. If we further assume that  $\alpha(y)$  is large only in a thin silicon layer in the vicinity of the Si/SiO<sub>2</sub> interface at y = 0, the electric field  $\mathcal{E}_n(x,y)$  can be considered constant with respect to y, and the integral in Eq. (6) becomes

$$\alpha_{\text{wg}} = C_{e(h)} \sigma_{e(h)} \tilde{\Gamma}, \tag{7}$$

where  $C_{e(h)}$  represents the constant  $C_e$  for positive gate voltages or the constant  $C_h$  for negative voltages, and  $\sigma_{e(h)} = \sigma_{e(h)}(V_{\text{gate}})$  is the corresponding two-dimensional voltage-dependent carrier density (unit m<sup>-2</sup>)

$$\sigma_{e(h)} = \int \mathrm{d}y N_{e(h)}(y). \tag{8}$$

If the silicon is intrinsic and the charge layer thickness is much smaller than the oxide thickness (as in our case), the two-dimensional carrier densities for electrons and holes  $(\sigma_e = \sigma \text{ for } V_{\text{gate}} > 0, \ \sigma_h = \sigma \text{ for } V_{\text{gate}} < 0)$  can be approximated by

$$\sigma = \epsilon_0 \epsilon_{\text{SiO}_2} |V_{\text{gate}}| / (q d_{\text{SiO}_2}), \tag{9}$$

where  $\epsilon_{SiO_2} = 3.8$  is the static relative permittivity of silicon dioxide, and q is the elementary charge.<sup>13</sup>

The so-called optical interaction factor  $\tilde{\Gamma}$  of the waveguide (unit  $m^{-1}$ ) is defined as

$$\tilde{\Gamma} = \epsilon_0 c n_{\text{Si}} \frac{\int dx (\mathcal{E}_1^2 + \mathcal{E}_2^2 - \mathcal{E}_3^2)|_{y=0^+}}{\int dx dy (\mathcal{E}_1 \mathcal{H}_2 - \mathcal{E}_2 \mathcal{H}_1)}.$$

(10)

For evaluating the interaction factor, we perform a numerical integration of the mode field. To this end, the optical mode is computed with commercially available software, <sup>14</sup> and we find  $\tilde{\Gamma}=2.63~\mu\text{m}^{-1}$ .

Using the constants  $C_{e(h)}^{(\text{ion})}$  determined by Soref, Eqs. (2) and (3), we obtain the red curve in Fig. 2, which was shifted by the experimentally observed offset -0.018 V/nm as discussed before. The constants as used by Soref therefore underestimate the actual optical loss in the inversion/accumulation layer. If Soref's model should be applied nonetheless, its constants must be adjusted. In Fig. 2 the blue straight lines are a better approximation to the measurements and represent an upper loss limit. The corresponding loss constants are

$$C_{\varrho}^{(\text{upper})} = 1.4 C_{\varrho}^{(\text{ion})}, \tag{11}$$

$$C_h^{(\text{upper})} = 1.8 C_h^{(\text{ion})}.$$

(12)

We therefore conclude that optical loss due to an inversion/ accumulation layer can be empirically described by Eq. (1) only if the coefficients  $C_{e(h)}$  become field-dependent. For gate fields in the range from  $-0.25\,\mathrm{V/nm}$  to  $0.25\,\mathrm{V/nm}$ , we find that the coefficients  $C_{e(h)}$  lie between the values determined by Soref, Eqs. (2) and (3), and those given in Eqs. (11) and (12).

The assumption made in deriving Eqs. (7)–(9), namely, that the charge layer is infinitesimally thin, is true only approximately. However, numerical simulations based on industry's standard software ATLAS show that more than 50% of the total charge in intrinsic silicon is located within the first 5 nm from the interface(gate fields larger than 0.1 V/nm or smaller than -0.1 V/nm). If in this range of gate fields we replace the simulated charge distribution by a delta-shaped distribution as is assumed in Eq. (9), the calculated waveguide attenuation coefficient would differ by less than 5%, so we adopt the simpler approach Eqs. (7) to (9).

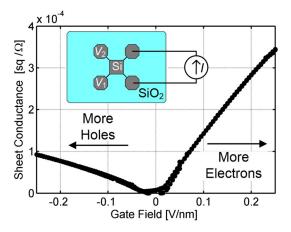

Now that we have measured the losses for a given gate field, we are also interested in the sheet conductance for a given gate field. Although several models exist for calculating the sheet resistance of accumulation/inversion layers in silicon, 11,15 we feel the need to measure this quantity for a sample belonging to the same SOI wafer as used for the optical loss measurements. To this end, a 2 mm × 2 mm square has been etched into a 220 nm thick photonic layer. The chip has been placed in a high-vacuum chamber for avoiding contamination of the surface, and to reduce the risk of electrical breakdown. The resistance is measured by a standard four-point procedure, <sup>16</sup> the result of which is shown in Fig. 3. For the highest gate field,  $E_{\text{gate}} = 0.25 \text{ V/nm}$ , we measure a sheet resistance of  $2.91 \,\mathrm{k}\Omega/\mathrm{sq}$ . This value corresponds, using Eq. (9), to an effective electron mobility  $\mu_{e,\text{eff}} = 1 / (q\sigma R_s) = 394 \text{ cm}^2/\text{V/s}$ , a factor 3.63 smaller than the intrinsic electron mobility  $\mu_e = 1430 \text{ cm}^2/\text{V/s}$ . For the gate field  $E_{\text{gate}} = -0.25 \text{ V/nm}$ , we obtain a sheet resistance of  $10.8 \,\mathrm{k}\Omega/\mathrm{sq}$ . We observe that the sheet resistance in inversion/accumulation layers on thermally oxidized silicon (as in our SOI) is a sensitive function of surface roughness and Coulomb scattering with fixed oxide charges. 11 Effective mobilities larger than the one we found are possible, 11 leading to potentially higher sheet conductances and lower optical losses for the same gate fields.

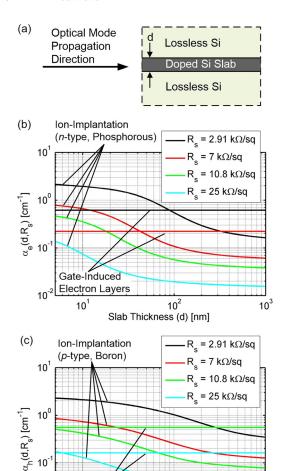

Finally, we compare optical losses of gate induced sheet layers with losses of ion-implanted layers for a given sheet resistance by using published data on conductivity and optical loss in doped silicon.

In order to get rid of any influence from the waveguide geometry (see interaction factor in Eq. (6)), we investigate an optical mode propagating along a doped silicon slab having a thickness d in a lossless background material with the same (real) refractive index  $n_{\rm Si} = 3.48$  as silicon. The optical mode is assumed to have dimensions much larger than the slab thickness d, Fig. 4(a).

We start looking at the attenuation coefficient  $\alpha_{e(h)}(d,R_s)$  in n-doped (p-doped) silicon slabs of thickness d with a sheet resistance  $R_{s,e(h)}$ . The sheet resistance  $R_{s,e(h)} = (q\mu_{e(h)}N_{e(h)}d)^{-1}$  depends on the electron (hole) mobility  $\mu_{e(h)}$ , the electron (hole) density  $N_{e(h)}$  and the slab

FIG. 3. Sheet conductance (inverse of sheet resistance) vs. gate field. The sample used consists of a 220 nm thick silicon belonging to an SOI wafer identical to the one used for the optical loss measurements. The measurements were performed in vacuum. The 2 mm  $\times$  2 mm silicon square as used for the four-point measurement is shown in the inset (the octagons are used for contacting the chip and connect the vertices of the square with 50  $\mu$ m wide silicon strips). A current I is forced to flow across two adjacent vertices and the voltages  $V_1$  and  $V_2$  are measured on the other vertices. The sheet resistance is calculated as  $R_{\rm s}=4.5324(V_2-V_1)/I.^{16}$

FIG. 4. Optical power attenuation coefficient of a mode (a) propagating along a silicon slab vs. slab thickness for a constant sheet resistance  $R_s$ , (b) for n-doping and an electron gate-induced layer and (c) for p-doping or gate-induced hole layers. The differently coloured lines represent different sheet resistances (legend) of the slab waveguide. If the carrier mobility in silicon would not depend on the doping levels, the curves for ion-implantation would be constant lines. The sheet resistance of gate-induced layers does not depend on the thickness of the silicon slab. For electrons, smaller optical losses can be obtained with gate-induced charge layers, especially for small thicknesses.

10<sup>2</sup>

Slab Thickness (d) [nm]

Gate-Induced

Hole Layers

10

10

thickness d. From tabulated data  $^{17}$  we extract the required ion concentration (for both n and p impurity types) for a given sheet resistance. We then assume that the ion concentration equals the free-carrier density  $N_{e(h)}$  (100% impurity ionization, see supplementary material). 9,19,20 The attenuation coefficient  $\alpha_{e(h)}(d,R_s)$  is then given by Eq. (7). Since the interaction factor  $\tilde{\Gamma}$  depends from the particular optical mode, we set here arbitrarily  $\tilde{\Gamma} = 1 \,\mu\text{m}^{-1}$ . It is found that the losses depend on the sheet thickness d, Figs. 4(b) and 4(c). This is because high impurity concentrations in silicon degrade the carrier mobility. For example, if the slab thickness is decreased, by a factor of ten, the ion concentration must be increased by more than a factor of ten for keeping the same sheet resistance  $R_s$ . And in fact, a sheet resistance of, e.g.,  $3 k\Omega/sq$  can be obtained in a 1000 nm thick slab with an *n*-type ion concentration of  $1.84 \times 10^{16} \, \mathrm{cm}^{-3}$ , as well as with a concentration of  $6.03 \times 10^{17} \, \text{cm}^{-3}$  (32 times larger) in a 100 nm thick slab, or a concentration of  $2.2 \times 10^{19}$  cm<sup>-3</sup> (an additional factor 36 larger) in a 10 nm thick slab. For an ion concentration of  $2.2 \times 10^{19} \, \mathrm{cm}^{-3}$ , the electron mobility has decreased by a factor 15 of its intrinsic value  $\mu_e = 1430 \, \mathrm{cm}^2/\mathrm{V/s}$ .

In the limit of large slab thickness, the attenuation coefficient  $\alpha_{e(h)}(d,R_s)$  converges to a finite limit which depends on the electron (hole) intrinsic mobility ( $\mu_e = 1430 \text{ cm}^2/\text{V/s}$  and  $\mu_h = 495 \text{ cm}^2/\text{V/s}$ ) as well as on the loss constants Eqs. (2) and (3). We denote this limit with  $\alpha_{e(h)}(\infty,R_s)$ . The ratio  $\alpha_h(\infty,R_s)/\alpha_e(\infty,R_s)$ , equals

$$\alpha_h(\infty, R_s)/\alpha_e(\infty, R_s) = C_h^{(\text{ion})}/C_e^{(\text{ion})} \times \mu_e/\mu_h = 2.04.$$

(13)

Since this value is larger than one, we recover the well-known result that for moderate doping levels and a fixed sheet resistance holes produce more optical loss than electrons.

Next, we derive the attenuation coefficient  $\alpha_{e(h)}(d, R_s)$  in the case of a gate-induced conductive sheet with a sheet resistance  $R_s$ . Since accumulation and inversion layers are a few nanometers thick only, the optical losses for layers thicker than, e.g., 5 nm must be independent of the slab thickness. For a given sheet resistance we derive the required gate voltage from the experimental data plotted in Fig. 3. The gate field in turn determines the optical losses according to the data in Fig. 1. The results are plotted in Figs. 4(b) and 4(c). We see that optical losses are independent of the slab thickness as stated above. Additionally, according to Fig. 4, holes produce more optical loss than electrons as is the case for ion implantation. But most importantly, one may observe that for thin slabs and for the same sheet resistance smaller optical loss can be obtained by injecting electrons with a gate voltage instead of using ion implantation.

In conclusion, we have measured the optical loss of inversion/accumulation layers in silicon, and loss coefficients have been determined. We find that the optical losses of thin sheet layers are smaller when the resistance is reduced by an inversion/accumulation layers rather than by doping silicon slabs.

We acknowledge support by the DFG Center for Functional Nanostructures (CFN), the Helmholtz International Research School of Teratronics (HIRST), the Karlsruhe School of Optics & Photonics (KSOP), the EU-FP7 projects SOFI (Grant No. 248609) and PHOXTROT, the BMBF joint project MISTRAL and the European Research Council (ERC Starting Grant 'EnTeraPIC', number 280145). We are grateful for technological support by the Karlsruhe Nano-Micro Facility (KNMF) and the Initiative and Networking Fund of the Helmholtz Association. We further acknowledge the Alfried Krupp von Bohlen und Halbach Foundation, the Deutsche Forschungsgemeinschaft and Open Access Publishing Fund of Karlsruhe Institute of Technology.

<sup>&</sup>lt;sup>1</sup>A. Liu, L. Liao, D. Rubin, J. Basak, Y. Chetrit, H. Nguyen, R. Cohen, N. Izhaky, and M. Paniccia, Semicond. Sci. Technol. 23(6), 064001 (2008); J. M. Brosi, C. Koos, L. C. Andreani, M. Waldow, J. Leuthold, and W. Freude, Opt. Express 16(6), 4177 (2008); R. Ding, T. Baehr-Jones, Y. Liu, R. Bojko, J. Witzens, S. Huang, J. Luo, S. Benight, P. Sullivan, J. M. Fedeli, M. Fournier, L. Dalton, A. Jen, and M. Hochberg, *ibid.* 18(15), 15618 (2010).

- <sup>2</sup>L. Liao, A. Liu, D. Rubin, J. Basak, Y. Chetrit, H. Nguyen, R. Cohen, N. Izhaky, and M. Paniccia, Electron. Lett. **43**(22), 1196 (2007).

- <sup>3</sup>Y. B. Tang, J. D. Peters, and J. E. Bowers, Opt. Express **20**(10), 11529 (2012).

- <sup>4</sup>R. A. Soref and B. R. Bennett, IEEE J. Quantum Electron. **23**(1), 123 (1987).

- <sup>5</sup>J. C. Irvin, Bell Syst. Tech. J. **41**(2), 387 (1962); D. B. M. Klaassen, Solid-state Electron. **35**(7), 953 (1992).

- <sup>6</sup>S. S. Li and W. R. Thurber, Solid-state Electron. **20**(7), 609 (1977).

- <sup>7</sup>J. Witzens, T. Baehr-Jones, and M. Hochberg, Opt. Express **18**, 16902 (2010); H. Yu, M. Pantouvaki, J. Van Campenhout, D. Korn, K. Komorowska, P. Dumon, Y. L. Li, P. Verheyen, P. Absil, L. Alloatti, D. Hillerkuss, J. Leuthold, R. Baets, and W. Bogaerts, *ibid.* **20**(12), 12926 (2012).

- <sup>8</sup>L. Alloatti, D. Korn, R. Palmer, D. Hillerkuss, J. Li, A. Barklund, R. Dinu, J. Wieland, M. Fournier, J. Fedeli, H. Yu, W. Bogaerts, P. Dumon, R. Baets, C. Koos, W. Freude, and J. Leuthold, Opt. Express 19(12), 11841 (2011).

- <sup>9</sup>See supplementary material at <a href="http://dx.doi.org/10.1063/1.4817255">http://dx.doi.org/10.1063/1.4817255</a> for details about waveguide fabrication, simulations and impurity ionization percentage.

- percentage. <sup>10</sup>Q. Lin, O. J. Painter, and G. P. Agrawal, Opt. Express **15**(25), 16604 (2007).

- <sup>11</sup>S. C. Sun and J. D. Plummer, IEEE Trans. Electron Devices **27**(8), 1497 (1980)

- <sup>12</sup>C. Vassallo, *Optical Waveguide Concepts* (Elsevier, Amsterdam, 1991).

- <sup>13</sup>S. M. Sze and K. Ng Kwok, *Physics of Semiconductor Devices*, 3rd ed. (Wiley, New York, 2006).

- <sup>14</sup>CST Microwave Studio, Computer Simulation Technology AG, Darmstadt, Germany.

- <sup>15</sup>C. Lombardi, S. Manzini, A. Saporito, and M. Vanzi, IEEE Trans. Comput.-Aided Des. 7(11), 1164 (1988).

- <sup>16</sup>L. J. van der Pauw, Philips Res. Rep. **13**, 1 (1958).

- <sup>17</sup>C. Bulucea, Solid-State Electron. **36**(4), 489 (1993).

- <sup>18</sup>W. Kern, Handbook of semiconductor wafer cleaning technology (Noyes Publications, Westwood, 1993).

- <sup>19</sup>W. Kuzmicz, Solid-State Electron. **29**(12), 1223 (1986).

- <sup>20</sup>F. Mousty, P. Ostoja, and L. Passari, J. Appl. Phys. **45**(10), 4576 (1974).